Chapter 9 Operational Amplifiers

operational amplifier (op-amp) 运算放大器无疑是模拟电路中最基础最重要的block之一. 这一章我们首先review telescopic and folded-cascode 拓扑, 然后学习two-stage and gain-boosting 结构, 和共模反馈问题, 最后引入slew rate, 分析supply rejection和op-amp的噪声问题.

9.1 General Considerations

运放一般和负反馈系统一起使用. 作为高增益差分运放, 高增益到底有多高呢? 取决于系统要求. 例如一个系统很看重speed, 而对gain error不那么在意, 那么我们就需要选择以速度优先的拓扑.

9.1.1 Performance Parameters

Gain

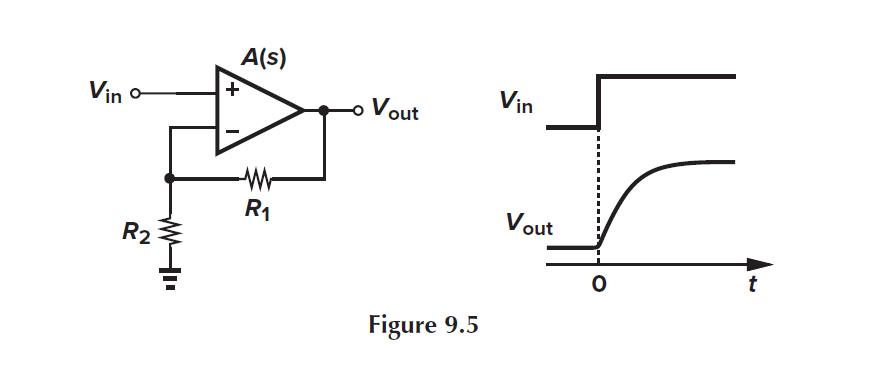

不同结构运放的增益不同, Cascode op-amp 能达到gain=1000, 单管CS结构 gain在10左右, 而且偏差很厉害

Small-Signal Bandwidth 小信号带宽

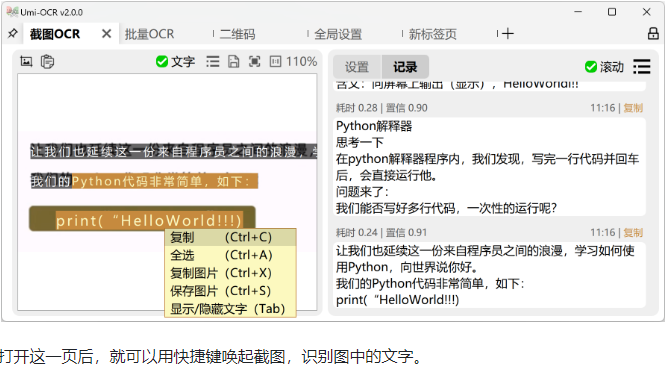

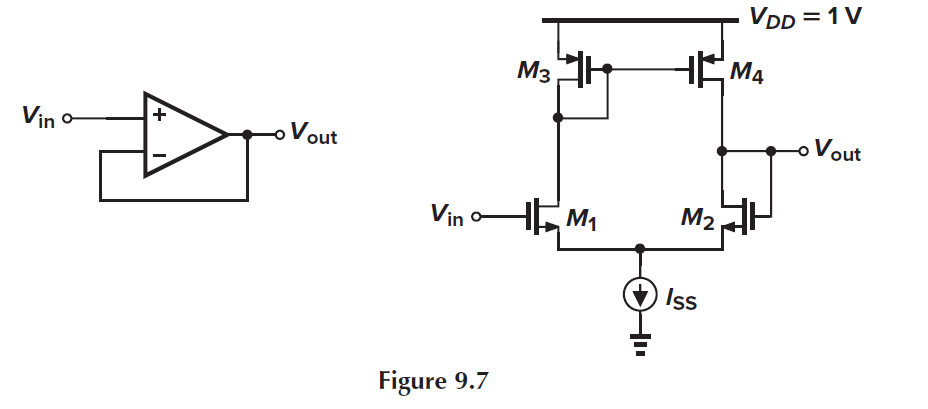

考虑下图的负反馈结构, Op-amp为单极点系统, 极点为wo

负反馈导致闭环极点为Loop Gain*wo, (增加了 loop gain 倍), 因此增加了带宽.

Large-Signal Behavior 运放的大信号表现为非线性, 但由于VDD和GND限制, 输出只能为VDD - 0V

Output Swing 输出摆幅, 能否输出rail-to-rail也是运放关心的指标. 取决于采用的架构

Linearity: 运放的线性性一般比较差, 因此大多采用闭环反馈运放实现Linearity. Chapter 14介绍用全差分运放来压制偶数项谐波频率

Noise and Offset: 噪声和offset 决定运放最小能处理的电压,

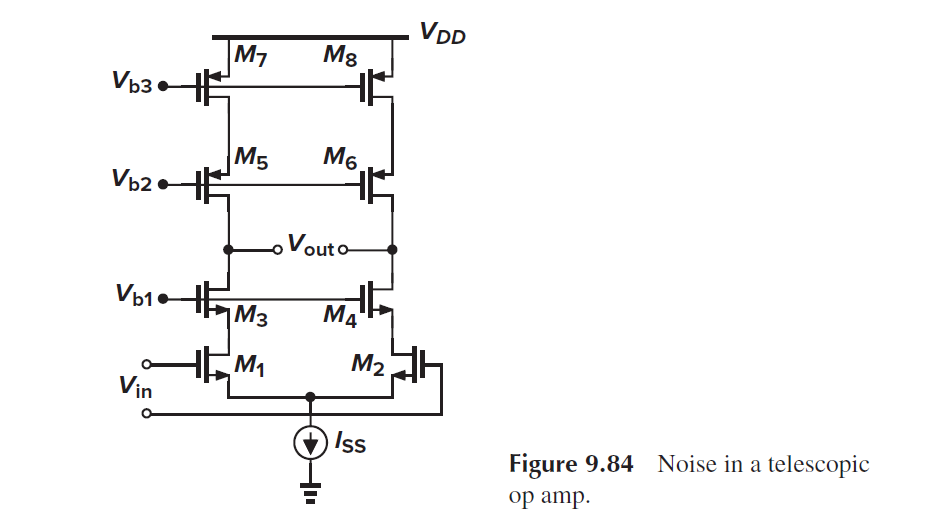

上图中, M1/M2, M7/M8 对噪声和offset产生主要贡献. 为了增加output swing, 我们希望M7/M8的override voltage即(Vgs-Vth)小. 但是这会增加M7的gm, 也会增加其噪声和offset贡献.

Supply Rejection PSRR也是op-amp指标之一, 采用全差分架构能增加PSRR.

9.2 One-Stage Op Amps

9.2.1 Basic Topologies

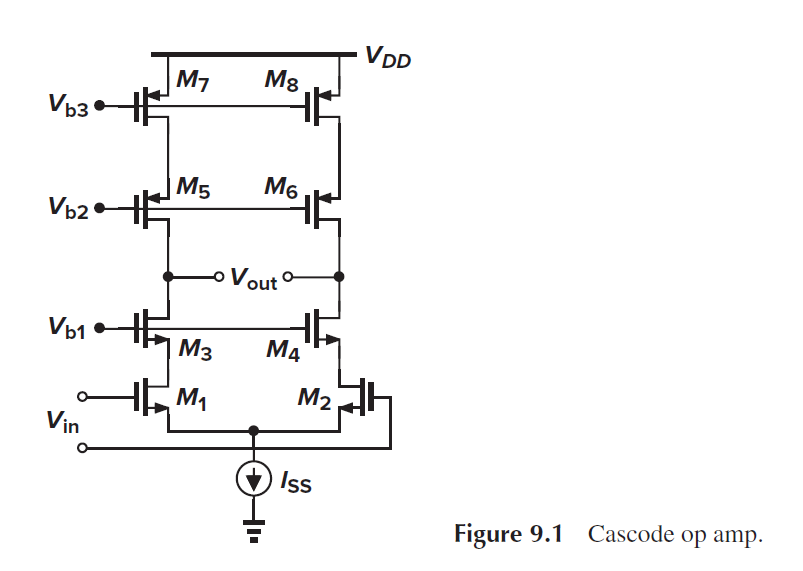

运放基本结构可用5管OTA架构

接成unity-gain buffer, 注意输入,输出的共模电压范围.

另外op-amp开环输出阻抗为rop||ron, 闭环输出阻抗为rop||ron/ (1 +gm*rop||ron)= 1/gm. 因此我们可以通过增加输出阻抗来增加开环gain, 同时实现较小的闭环输出阻抗.

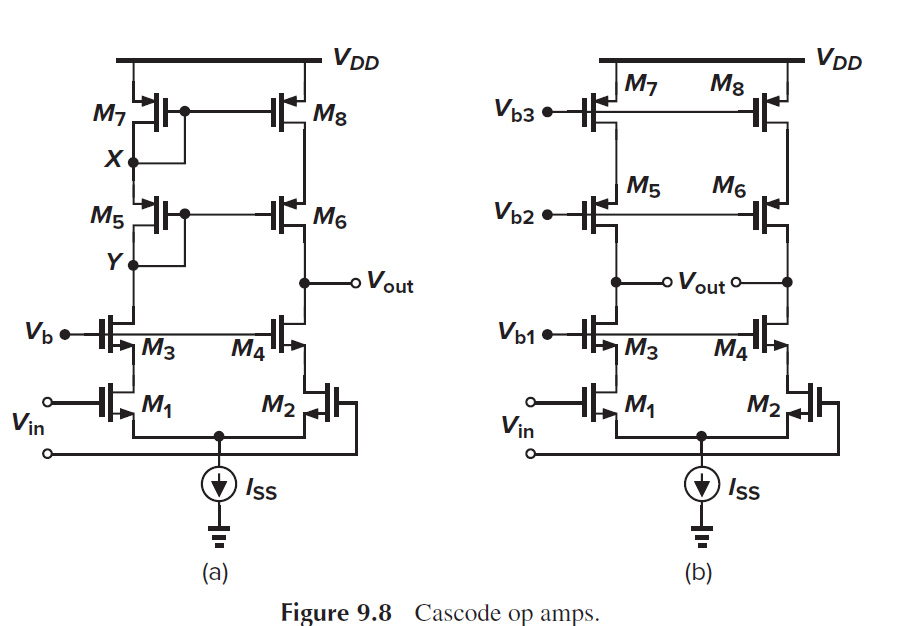

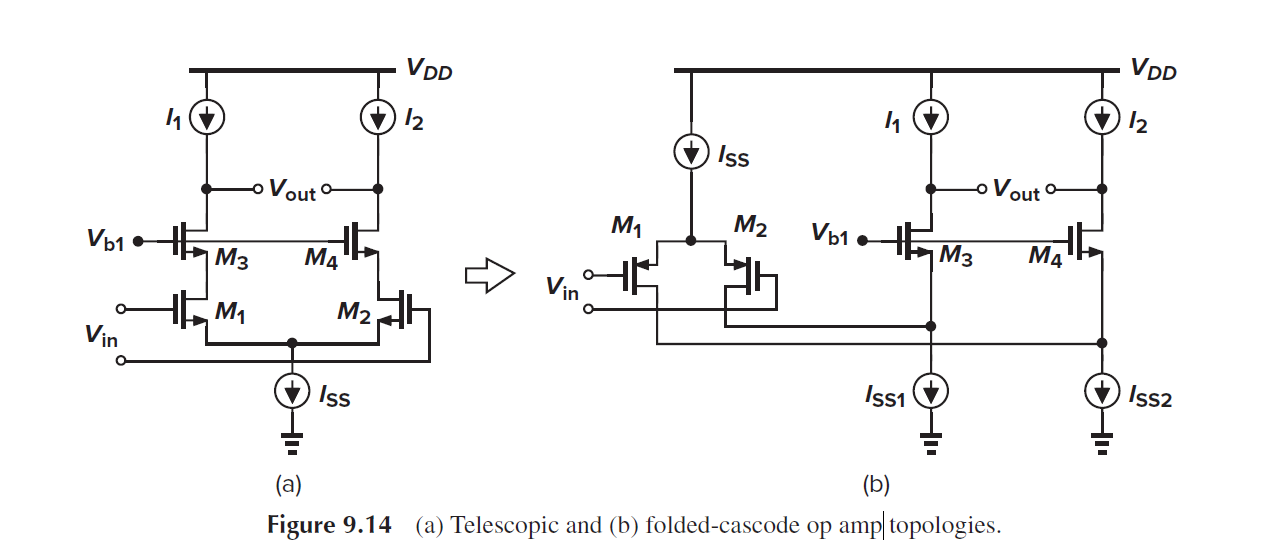

可以采用telescopic cascode 套筒式cascode 结构进一步增加输出阻抗和gain. 但代价为减小了输出摆幅, 而且引入极点 ( X和Y处).

9.2.2 Design Procedure

对于每个管子, 我们主要关注下面几个设计目标: ID, VGS − VTH, W/L, gm, and ro.

考虑上图

增益: Av ≈ gm1[(gm3rO3rO1)(gm5rO5rO7)].

减小bias电流或者提高W/L能增加增益.

考虑摆幅, PMOS的mobility小, Vgs-Vth override 电压设成300mV. NMOS的override电压设成200mV.

9.2.3 Linear Scaling

考虑加倍bias电流, 加倍W/L, 导致Vgs-Vth保持恒定, override输出摆幅保持恒定. gm 翻倍了(类似两个管子并联), ro减半. 因此gain和输出摆幅保持不变.

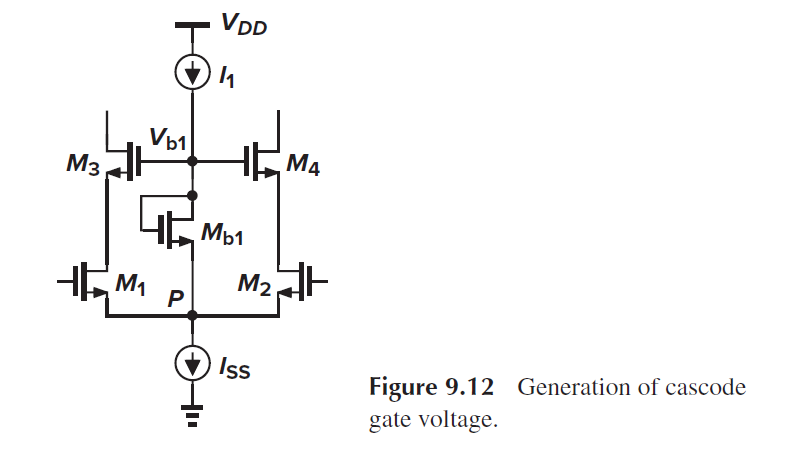

为了保证M3/M4处于饱和区, 可以加一个W/L很小(weak)的Mb1, 产生足够大的Vgs, 并且跟随Vcm, 确保M3,M4的gate voltage

9.2.4 Folded-Cascode Op Amps

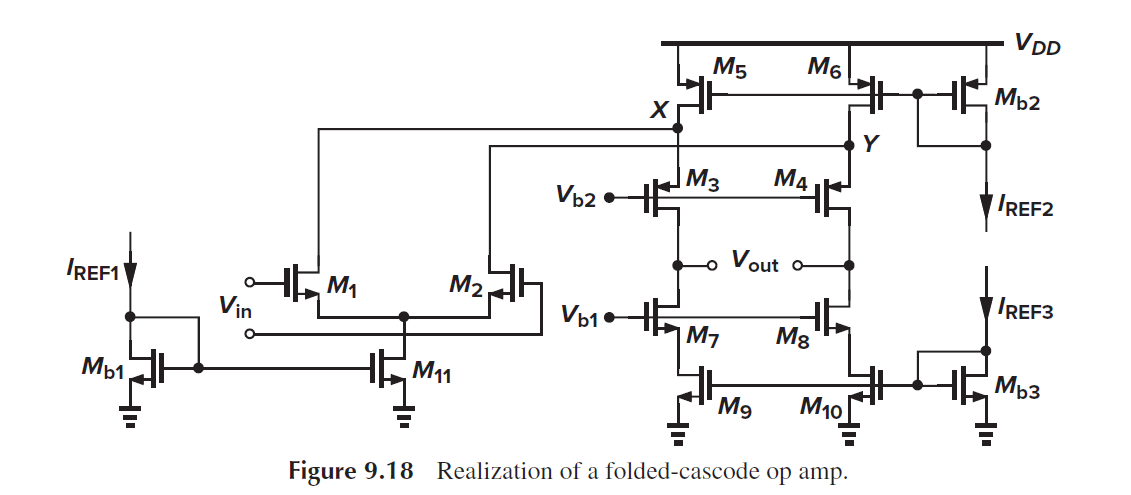

为了解决telescopic cascode的output swing和输入共模电压问题, 采用Folded-Cascode, 即输入对管和cascode管采用不同类型的PMOS/NMOS. 如下图所示

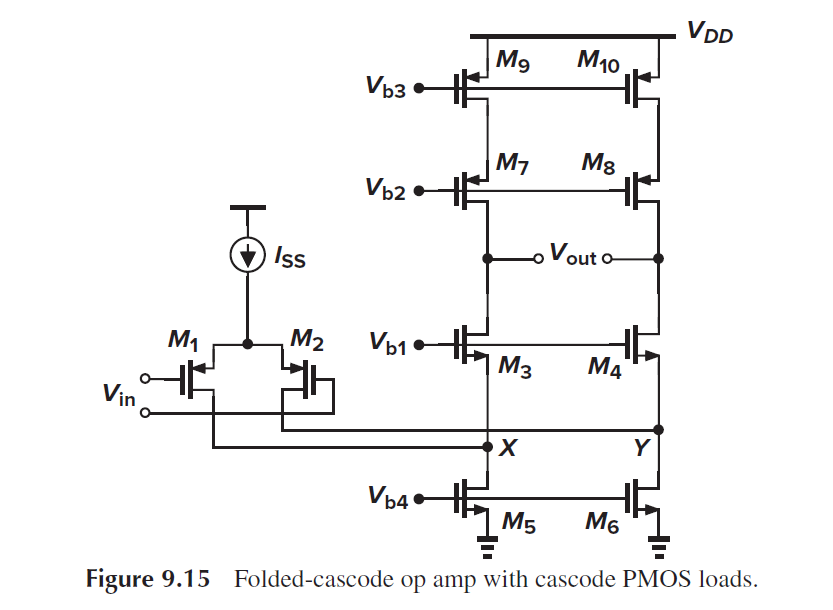

考虑下图的Folded-Cascode结构

输出最小值: VodM5+VodM3. 输出最大值: VDD-VodM9+VodM7.

输入电压最小值: Vb1-Vgs3-|Vth1|, Vin,cm最小值可以为负值, 因此可以将输入和输出接到一起, 做unity buffer.

增益: Av=Gm*Rout

NMOS输入的Folded-Cascode如下图所示

请注意X "folding point”处的极点. P=1/(R*C). 其中R=1/gm3, C包括CGS3,CSB3,CDB1,和CGD1. 这个极点较低, 需要小心.

9.2.5 Folded-Cascode Properties

比起telescopic cascode, Folded-Cascode的功耗更大, Av Gain更低, 极点更低. 但是瑕不掩瑜, Folded-Cascode的输入输出共模CM电压范围更大, 而且不影响输出摆幅, 因此还是被广泛应用.

NMOS作为输入对管, 其Vin,cm最高值可以到Vb2 +|VGS3|+ Vth1, 比VDD高都行

PMOS作为输入对管, 其Vin,cm最低值可以比GND电压还低.

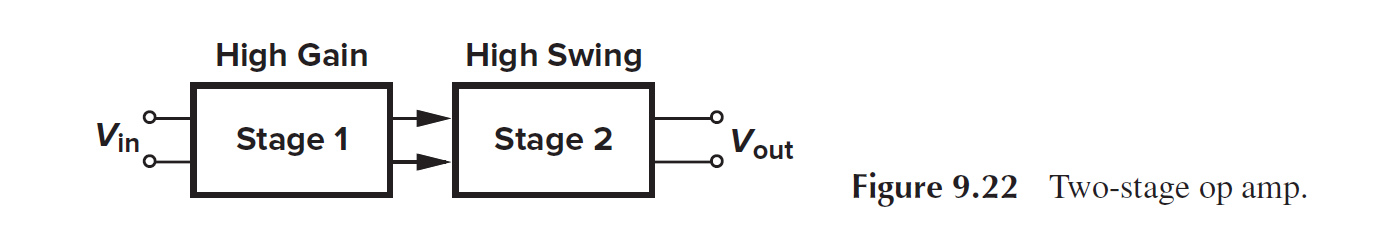

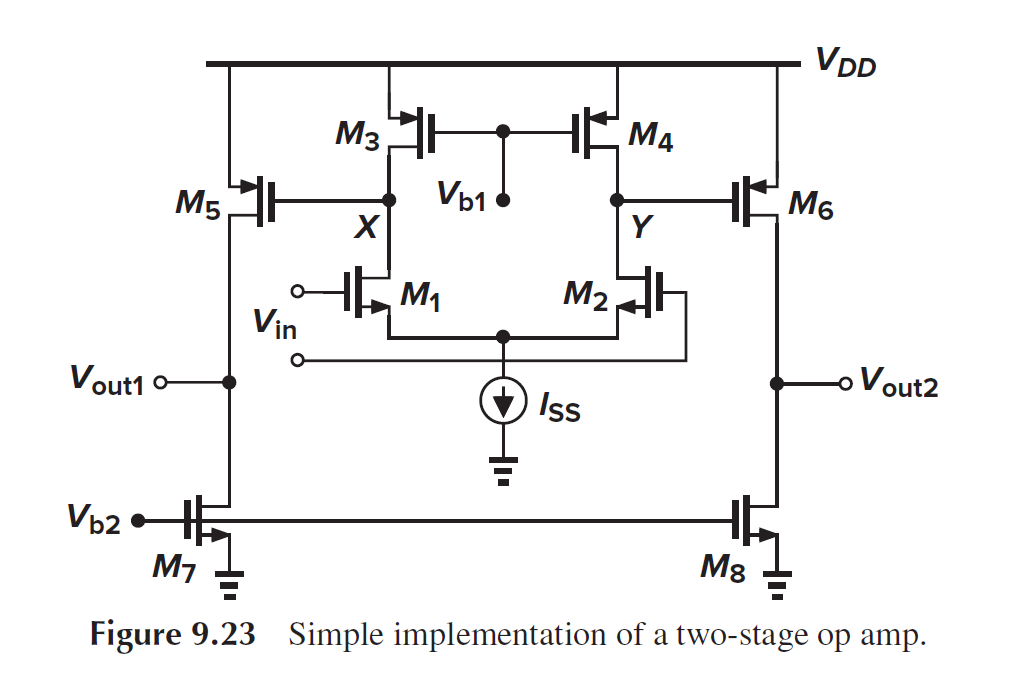

9.3 Two-Stage Op Amps

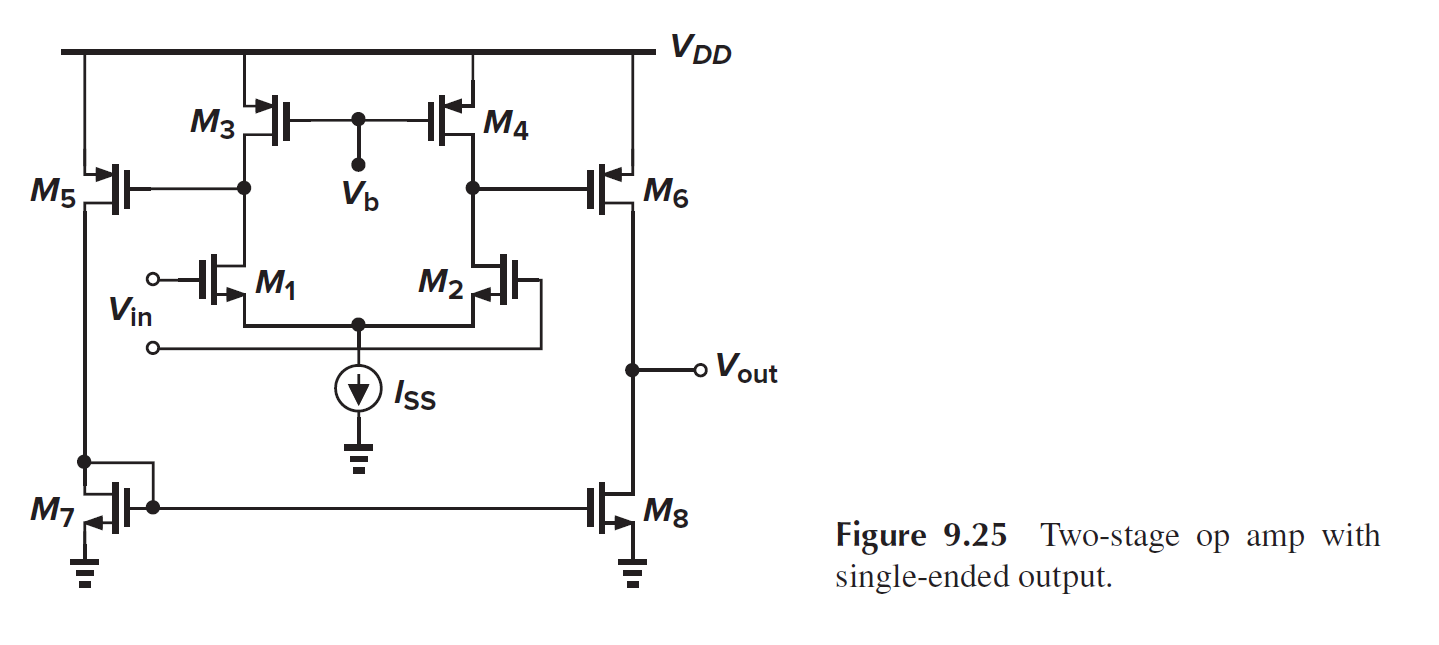

为了同时实现高增益和high swing, 可以采用2级运放结构. 如下图所示

输出级可用CS结构, 如下图所示

也可以产生单端输出, 如下图所示

如果要增加增益, 第一级可用cascode结构

9.4 Gain Boosting

9.4.1 Basic Idea

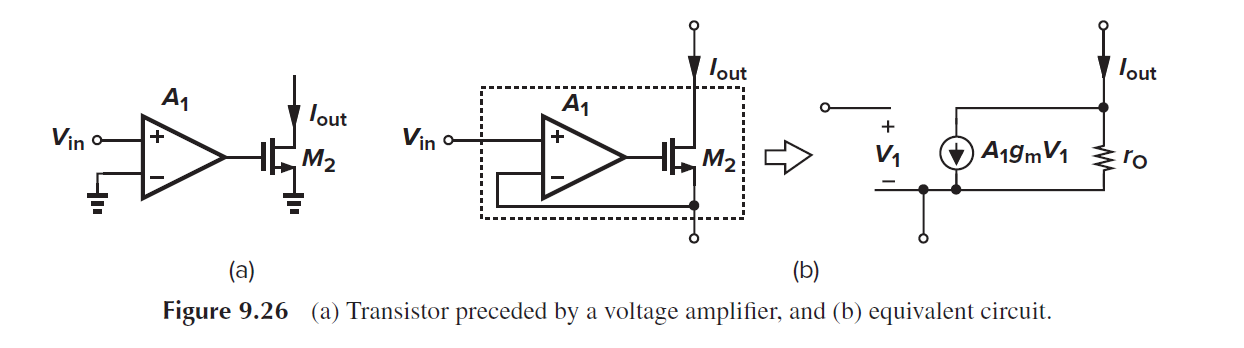

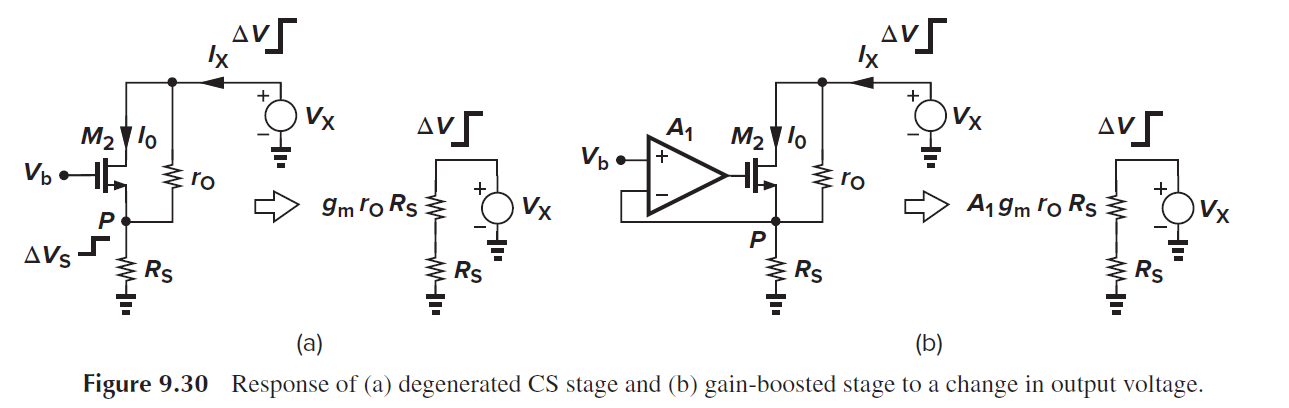

First Perspective Gain boosting 第一个观点是为了增大输出阻抗, 增大gain.

闭环增益为Av=−A1 *gm *ro.

下图为串联输出

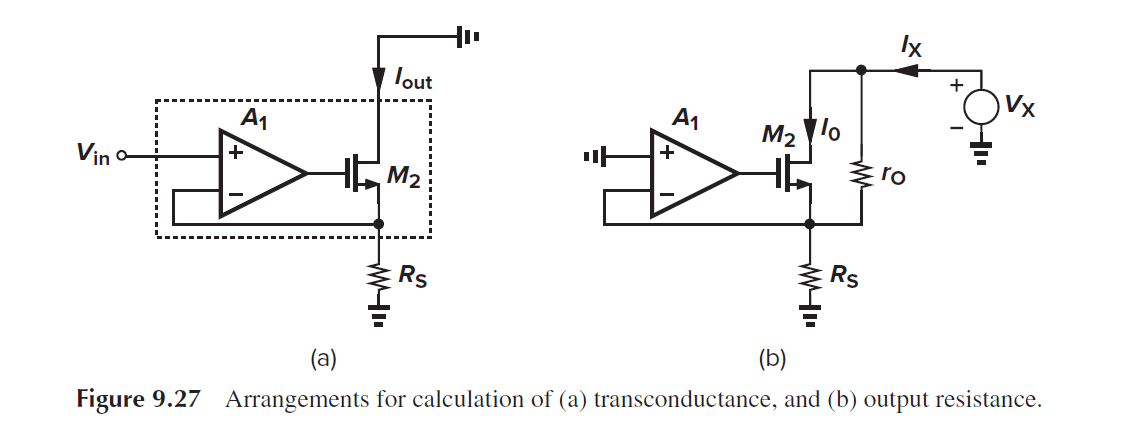

输出阻抗: Rout=Av*Rs

如果为下图所示, 并联输出. 输出阻抗=RD/Av

Second Perspective

gain boost第二个观点是通过检测source电压, 维持VP电压的稳定, 通过运放钳位输出电流, 这样能极大增加输出阻抗.

9.4.2 Circuit Implementation

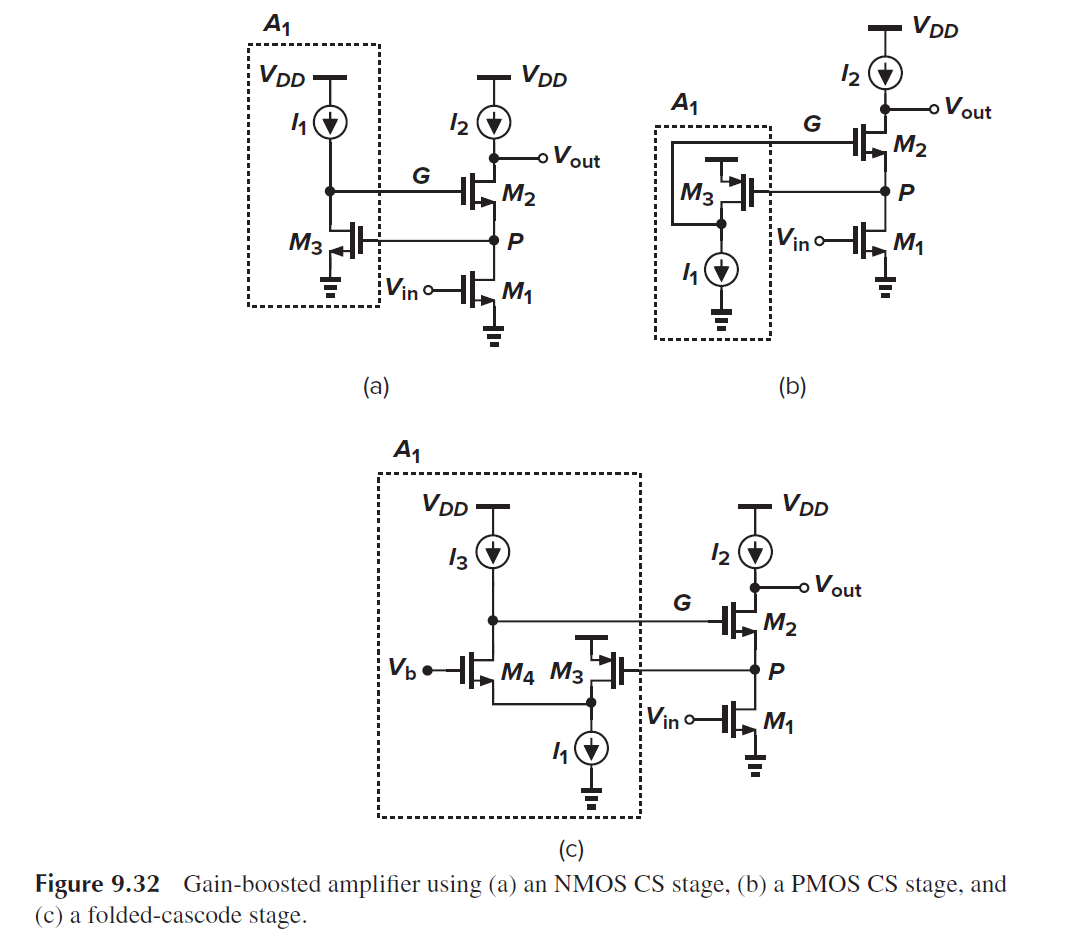

Gain Boosting电路实现可用下面电路 a) CS NMOS, b) CS PMOS, c) folded casecode

a) CS NMOS结构会抬高Vp点的headroom, 最低值=Vgs3, 而不是Vov1. Vout/Vin的gain为gm1ro1gm2ro2(gm3ro3+1)

b) CS PMOS结构, 解决了Vp的headroom问题, 但是M3可能处于线性区, 因为M2的gate可能很高

为了解决上述问题, 可以采用c) folded casecode 结构, M4可作为upward level shift, 抬高VG.

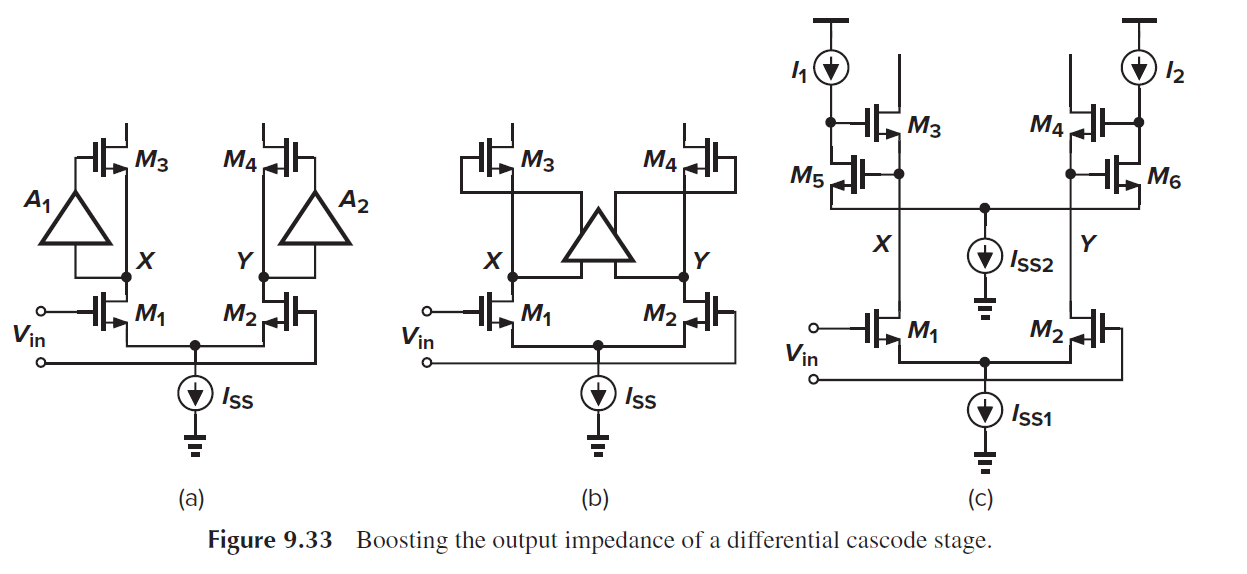

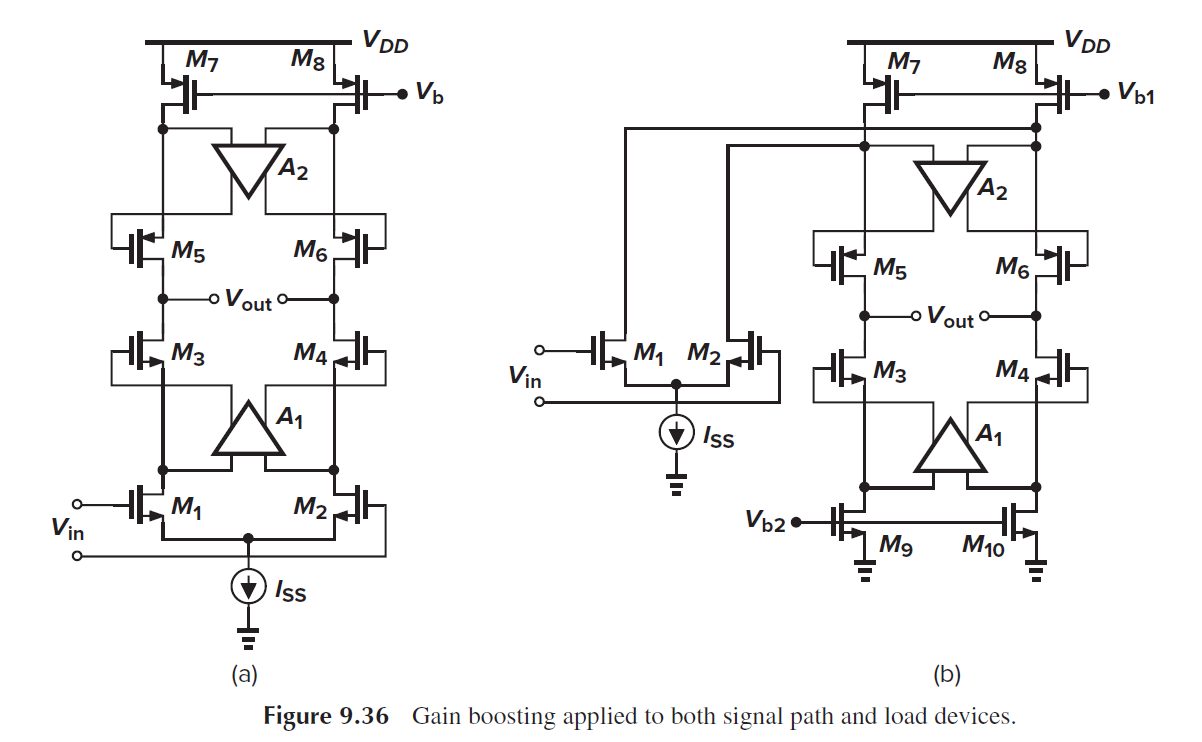

对于差分运放, 采用gain boosting技术可用下面几个结构:

c) 会引入headroom 问题, 可以采用folded casecode来解决.

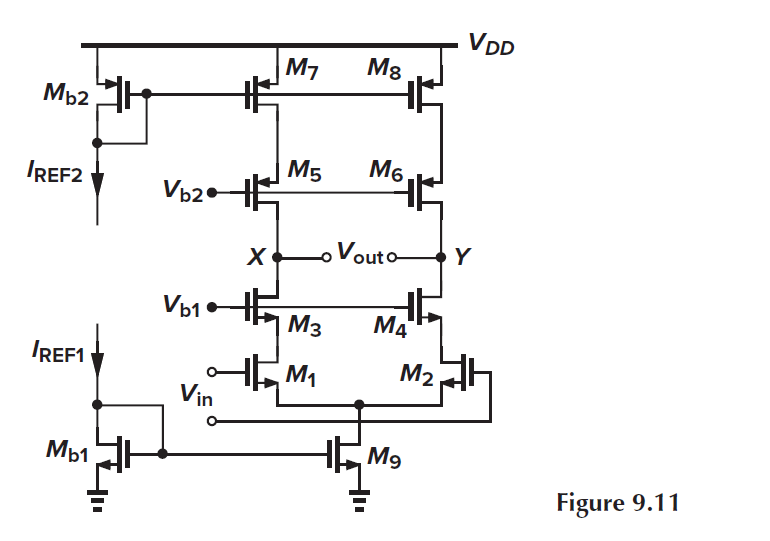

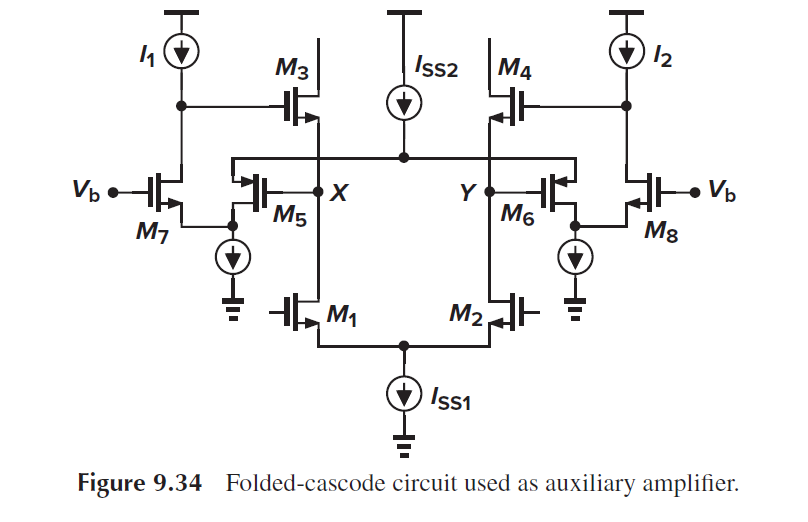

对于casecode op-amp可以采用gain boost技术来增加输出阻抗, 因而极大增加Av Gain. 如下图所示

注意这里A2需要采用NMOS作为输入对管的folded cascode结构. 即输入是NMOS, 输出是PMOS (和 Fig 9.34相反)

9.4.3 Frequency Response

Gain Boost的频率响应 取决于Gain放大电路的pole和系统本身pole.

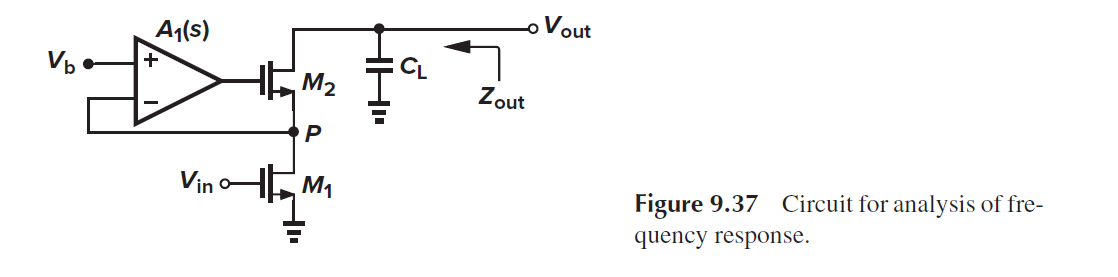

我们以下图Gain Boost为例

Gain Boost放大电路A1为单极点系统

A

1

(

s

)

=

A

0

1

+

s

ω

0

A_1(s)=\frac{A_0}{1+\frac{s}{\omega_0}}

A1(s)=1+ω0sA0

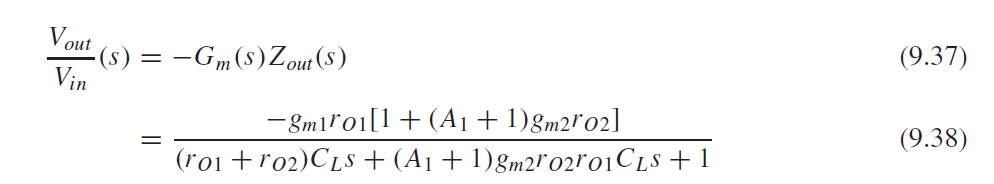

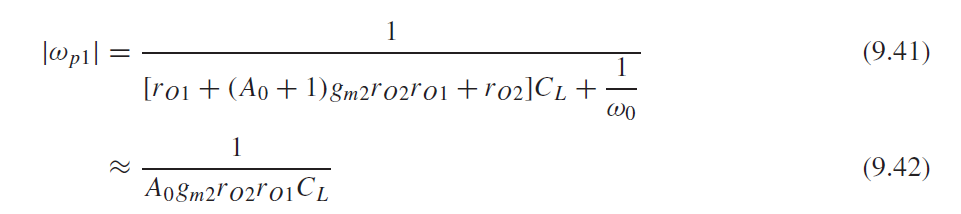

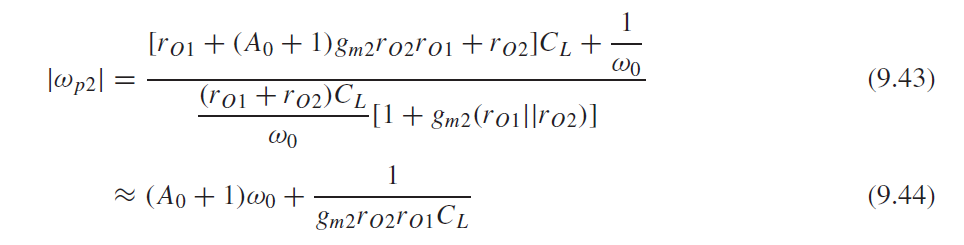

V o u t V i n = − G m Z o u t \frac{V_{out}}{V_{in}}=-G_mZ_{out} VinVout=−GmZout

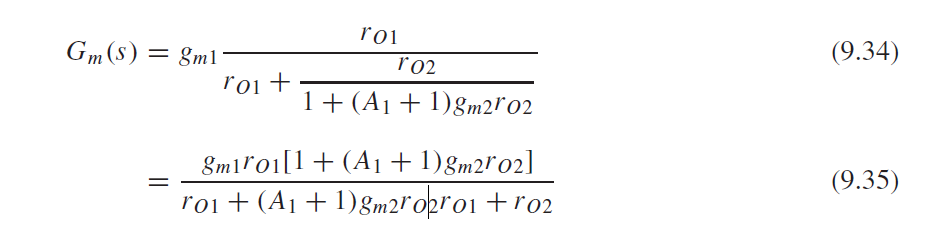

计算Gm, M2 source 看进去的阻抗为1/(Av1*gm2)

因此Gm约为gm1

Zout为

因此Gain=-Gm*Zout为

整理可得, 有左零点, 位置在Gain Boost放大器的GBW处

主极点, dominant pole, 即1/(Rout*CL)

次极点位置

注意, 这个次极点 比之前的casecode的GBW略高. 另外1/(gm2ro2ro1CL)就是不带Gain Boost运放A1的输出极点.

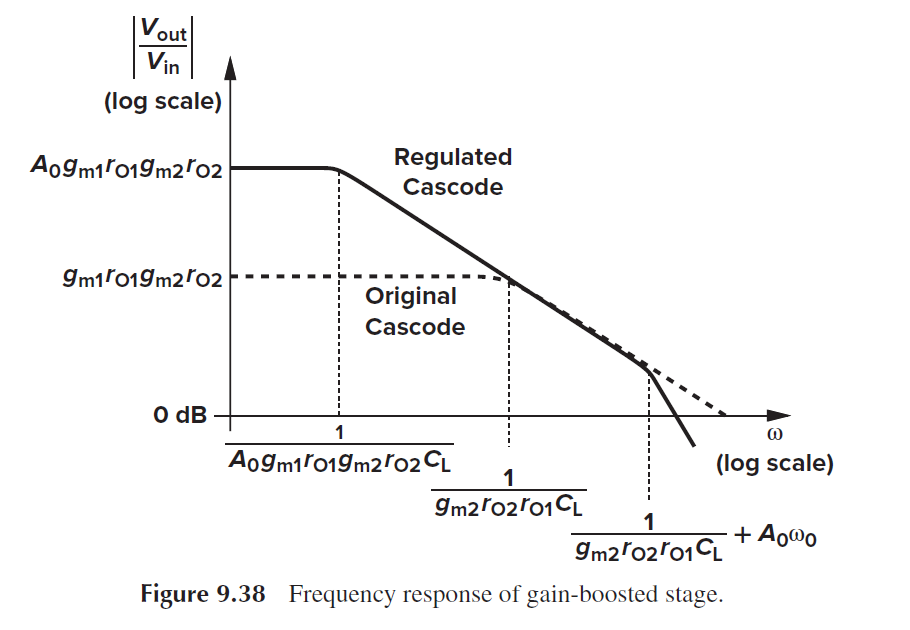

频率响应如下图所示

相比于普通cascode, regulated cascode频率响应类似单极点系统, 提高了低频增益 by Ao倍, 第二极点在原来的f-3db +Aowo (A1 GBW)处. 左零点位置在Gain Boost放大器的GBW处.

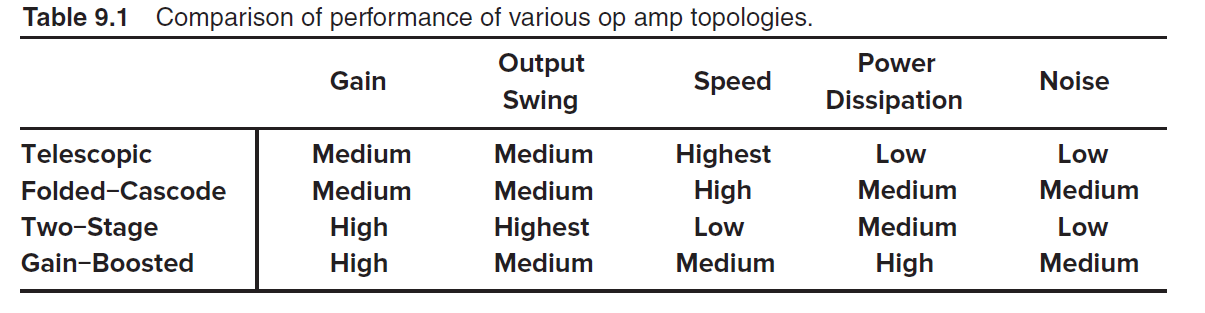

9.5 Comparison

下图比较了telescopic cascode, folded cascode, two-stage op amp, 和 gain boosting, 四种运放的增益, 输出摆幅, 速度, 功耗和噪声.

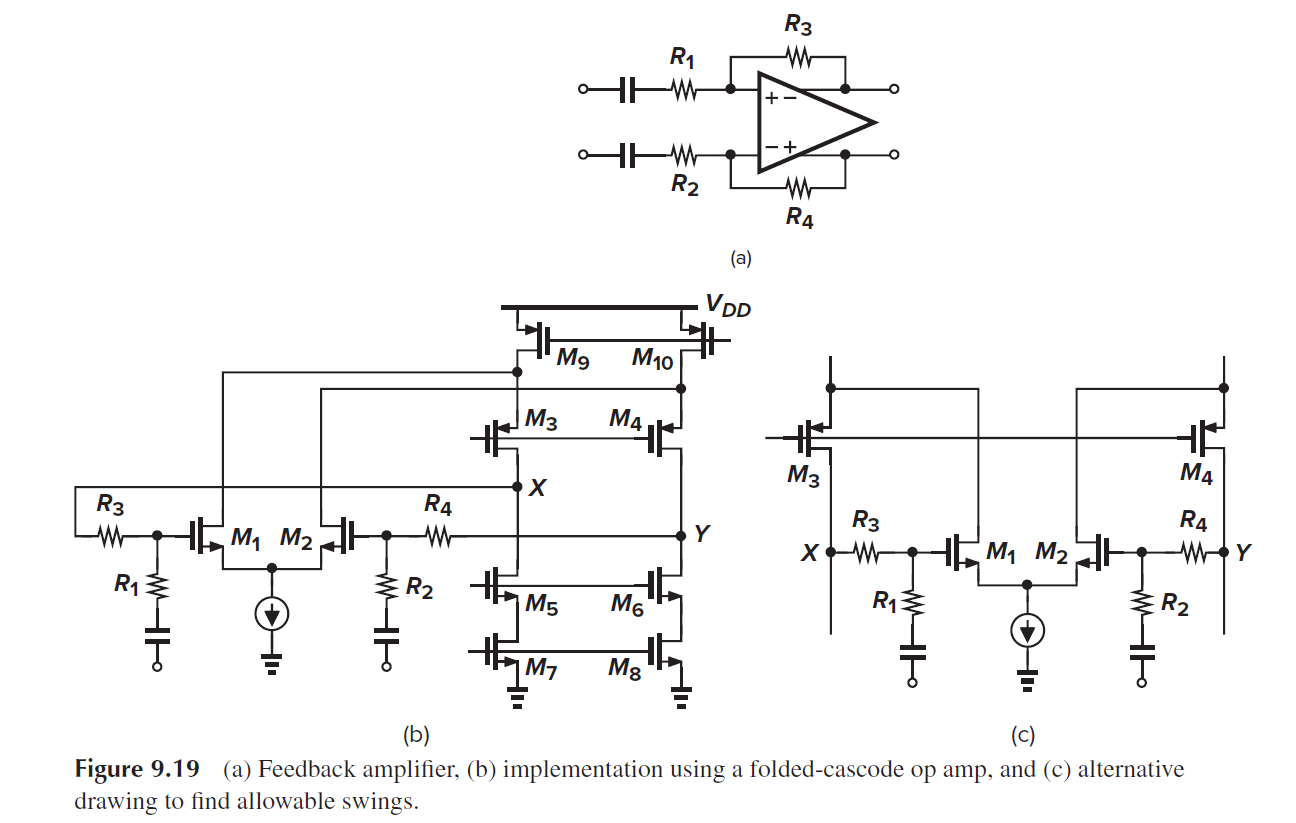

9.6 Output Swing Calculations

输出摆幅主要是影响gain, 从而影响线性度.

9.7 Common-Mode Feedback

9.7.1 Basic Concepts

之前chapter我们介绍了全差分结构, 其优点是没有mirror pole, 能实现更大的闭环速度, 输出摆幅更大. 但全差分结构需要共模反馈电路 “common mode feedback” (CMFB).

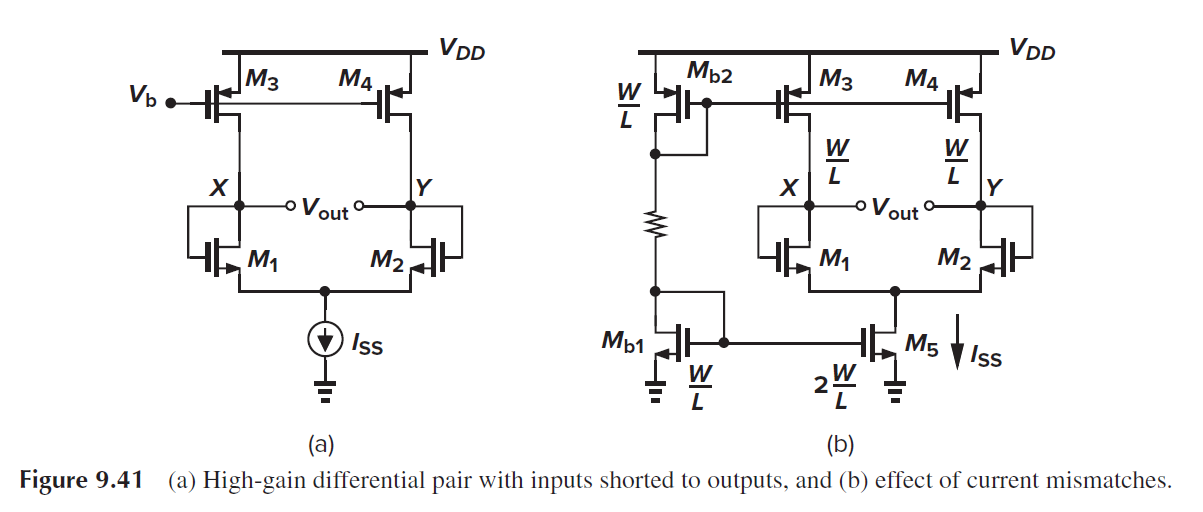

上面的电路看似美好, 尤其是b) 可以根据M5的Iss提供M3和M4的偏置电压. 但系统存在任何mismatch, M3+M4的电流就会大于或者小于M5 Iss电流, 造成X点或者Y点电压到达VDD或者VSS. 这是差分输入对不能解决的. 究其原因是对于高增益运放, 不能指望(Ip-In)*Rout=VDD/2.

9.7.2 CM Sensing Techniques

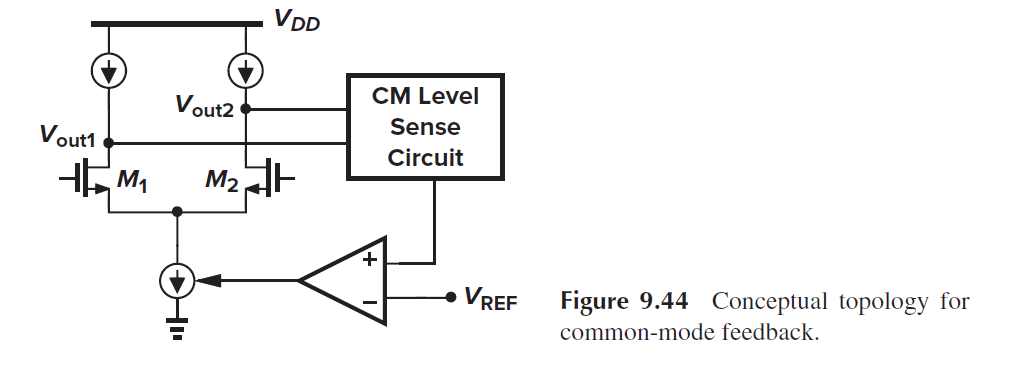

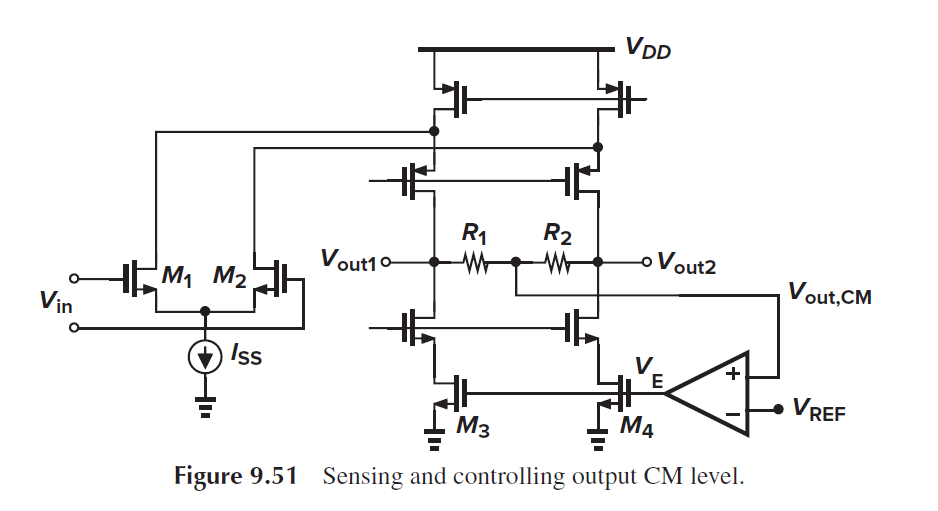

因此我们需要共模反馈电路CMFB来采样输出电压的共模CM值, 反馈调节运放的bias电流. 基本原理如下图所示

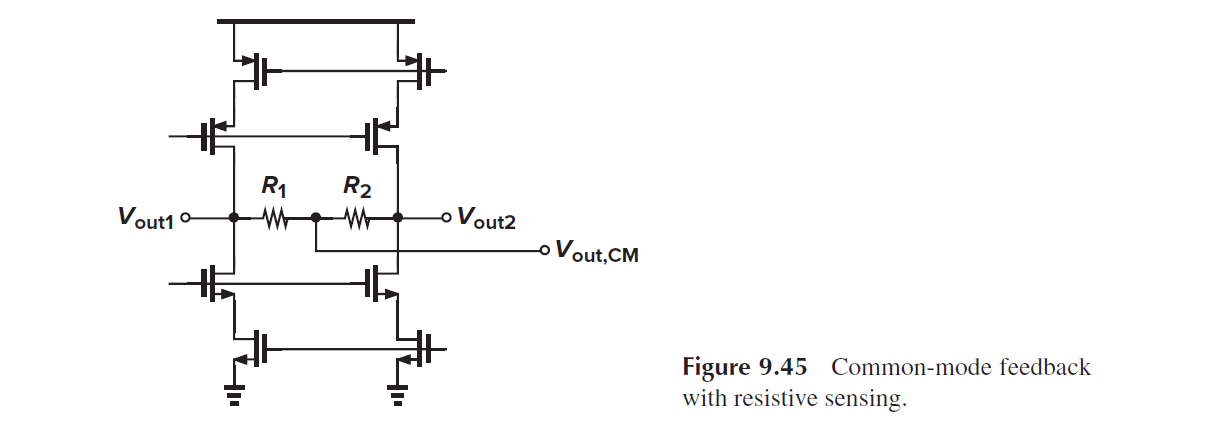

对于CM采样, 可以用大电阻的R1和R2 (为了维持差分增益)

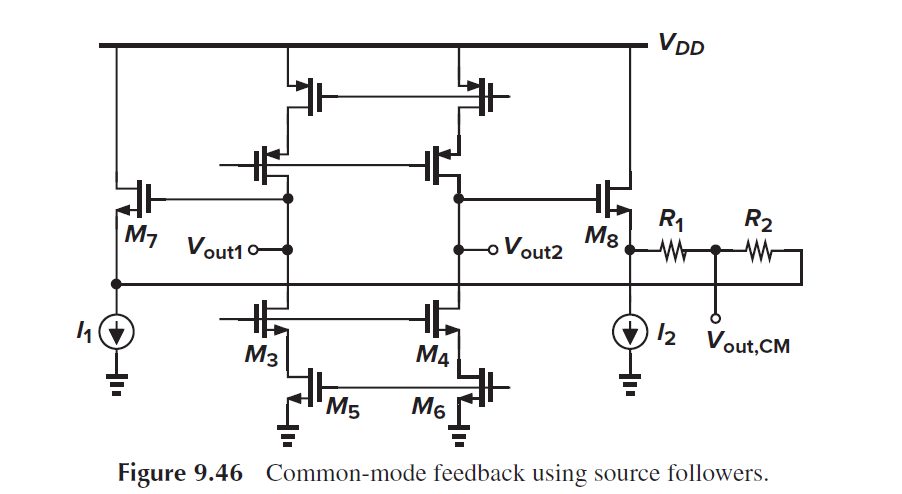

CMFB也可以用source followers代替, 注意R1需要large enough, 否则M7和M8要get starved, 就不能sense Vout的CM平均值.

用source followers作为CMFB的问题是限制了差分输出的摆幅. 由于source follower, 输出Vout需要最低电压增大到Vgs8+VI2.

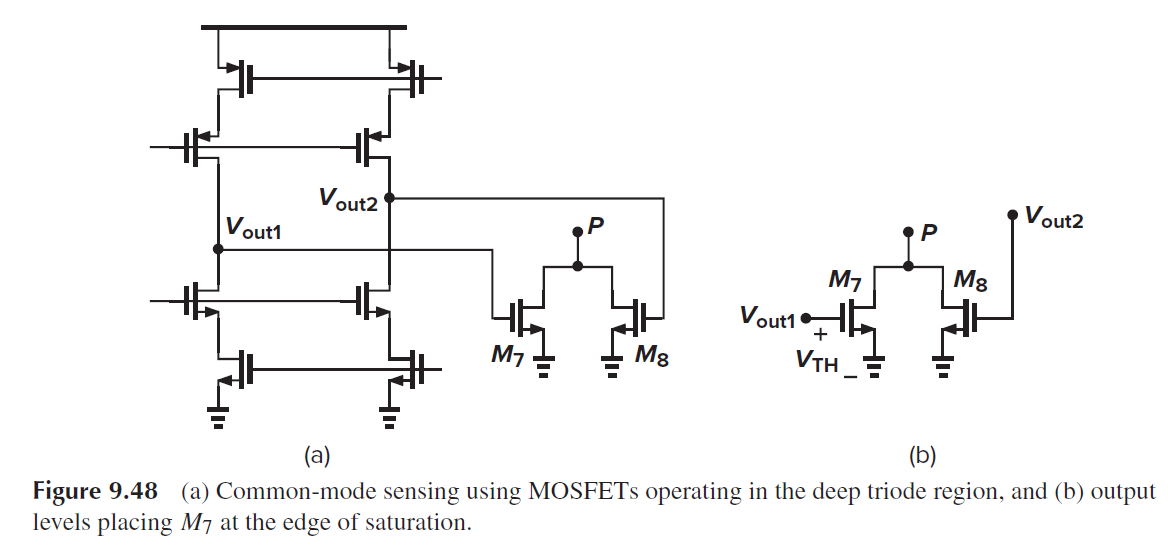

还可以用处于深线性区的MOS做采样电阻. 如下图所示

在输出Vout引入的电阻为

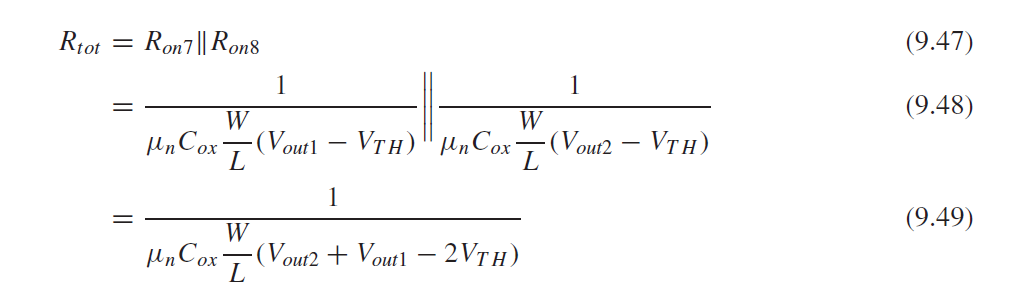

还有 一种方法, 将Vout与Vref (Vb)进行比较, 输出Icm. 因为M2的电流为(gm/2)Vout1, M4的电流为(gm/2)Vout2. 因此Icm正比于(Vout1+Vout2)

9.7.3 CM Feedback Techniques

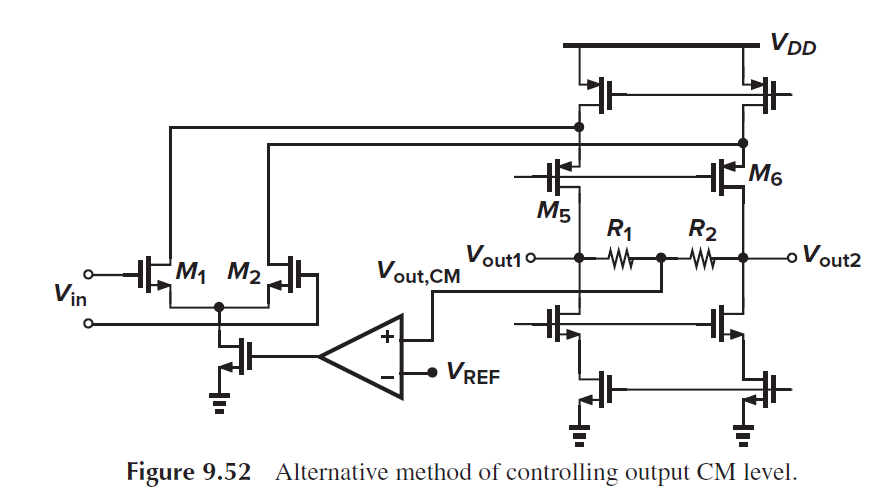

这一小结我们来研究CM反馈技术. 我们通过R1,R2把Vout,cm采样了, 用一个运放和Vref进行放大, 输出Ve可连接到M3和M4的gate端口.

或者控制M1,M2 current sink的gate端也行

原理都是当Vout,cm变大时, Ve变大, 通过负反馈降低Vout,cm

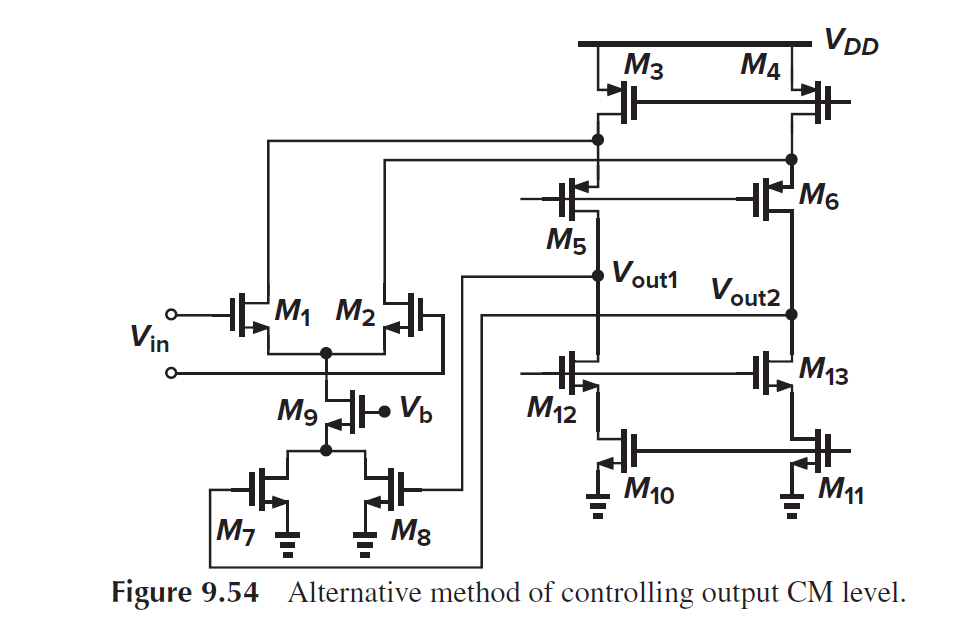

对于9.7.2采用线性区采样电阻的电路, Vout,cm通过电阻转换为电流Icm, 可直接控制Vout,cm. 如下图所示

当Vout1,2上升时, Ron7||Ron8降低, 导致M5,M6的电流增加, 从而把Vout1,2拉下来.

通过Vb − VGS9 = 2ID(Ron7||Ron8), 和线性区Rout公式可得

可以看到Vout值和device参数有关. 另外(Ron7||Ron8)的电压drop限制了输出摆幅.

Vb影响了输出Vout,cm. Vb上升, M1,M2电流增加, Vout,cm下降. M7,M8通过CMFB的loop gain来调节这个error

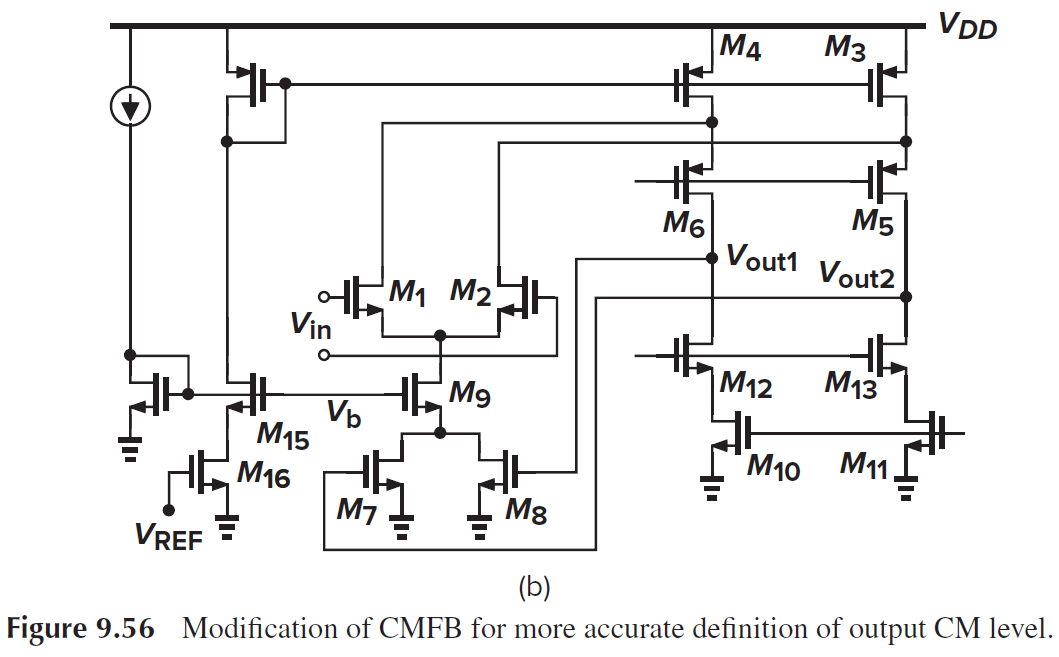

为了解决Vb对Vout,cm的影响, 我们引入下面这个电路

(W/L)15 = (W/L)9 , (W/L)16 = (W/L)7+(W/L)8.

用电流镜Ibias和Vref, 产生Vb, 让ID9跟随Ib和Vref. 只有当Vout,cm=Vref时, ID9=ID15=Ibias. 这样Vout,cm的值就能由CMFB定成Vref.

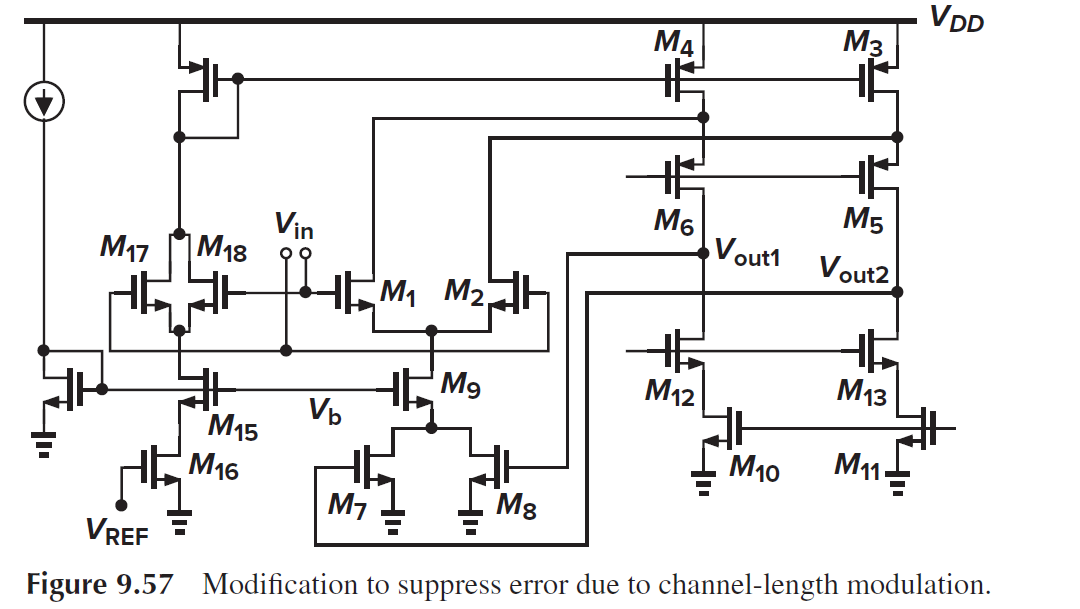

在实际应用中, VDS15 ≠ VDS9, 会产生error. 可以通过添加M17和M18消除M15的channel-length modulation

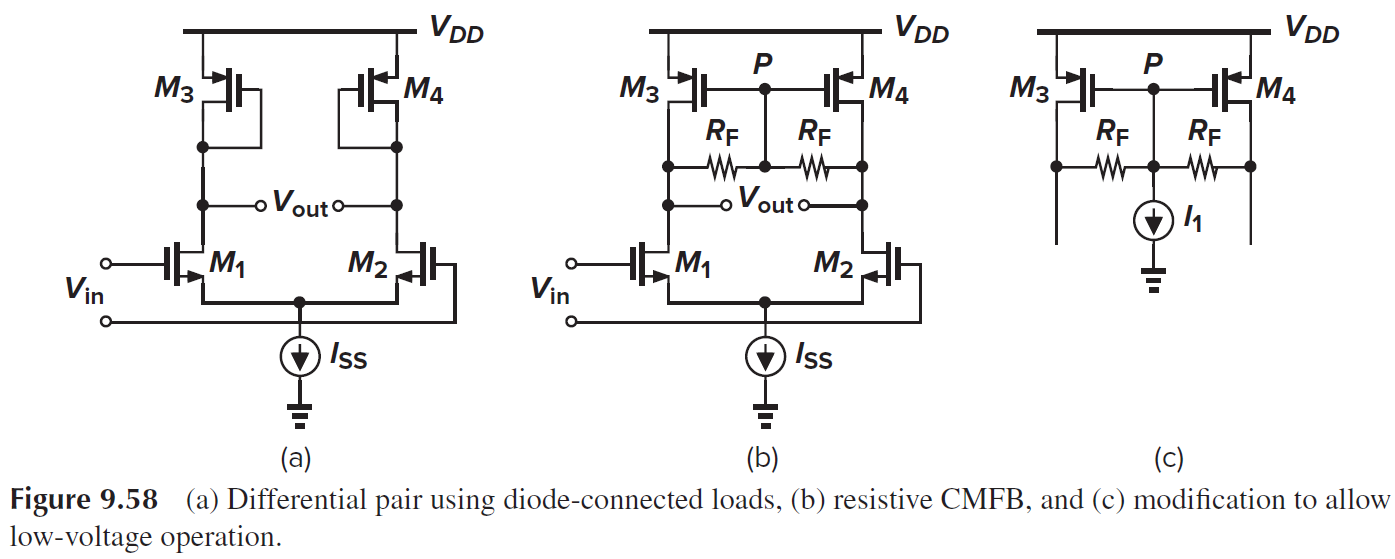

还有一种简单的CMFB的方式如下图所示

PMOS M3和M4为类似diode连接方式. 这个电路在低增益应用中很有用.

a) 输出共模电压: VDD-Vsg3,4较高. 电压增益较小. b) 添加RF, P点为"虚拟地", gain为gm1,2(rO1,2 * rO3,4 * RF). 选择RF >> rO1,2||rO3,4.

c) 通过电流I1进一步降低Vout,cm.

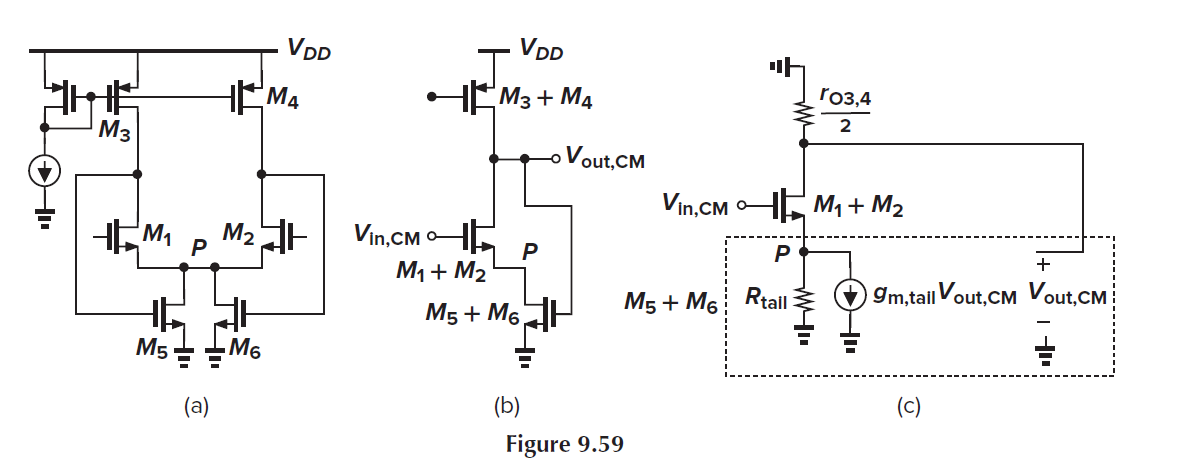

如果把 triode M5,M6的共模反馈直接接到VP, 如下图所示

其CM小信号模型为下式, 其中每一项都小于1, 因此CMFB gain很小, error很大, Vout,cm不太能影响Vin,cm

9.7.4 CMFB in Two-Stage Op Amps

两级运放的优点是轨到轨输出, 因此应用更加广泛.

我们以上图为例, a)为两级运放

b)为采样第二级Vout_cm, 反馈到第二级. 但问题是当第一级Iss变小时, X和Y上升, 导致M3和M4进入线性区. 这样的设计不好.

c)为采样第二级Vout_cm, 反馈到第一级控制Iss. 当Vout1,2上升时 , Ae输出减小Iss, 导致Vx和Vy上升, 导致Vout 1,2下降. 这个结构的问题是, 这个CMFB的极点较多, X,Y处一个极点, Vout处一个极点, 加上Ae的极点, 稳定性很难调.

为了避免稳定性问题, 考虑下面结构. R1和R2提供第一级的CMFB, R3和R4提供第二级的CMFB,

9.8 Input Range Limitations

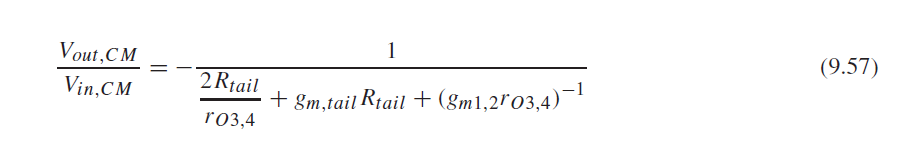

考虑输入电压范围, 我们以下图unity gain buffer为例

输出范围=输入范围, Vin,min ≈ Vout,min = VGS1,2 + VISS. 如果输入电压小于这个最低值, Iss会变小, 从而减小输入gm.

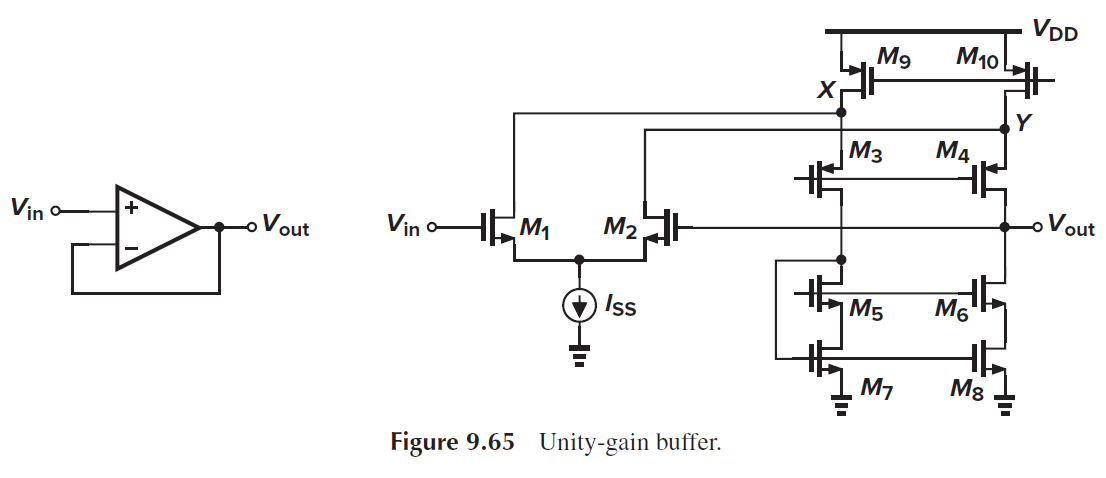

解决办法采用轨到轨电路如下图所示, 当NMOS或者PMOS死的时候, 另外一路还"活着". 但随着输入电压变化在0-VDD之间, gm是变化的, 如下图所示.

9.9 Slew Rate

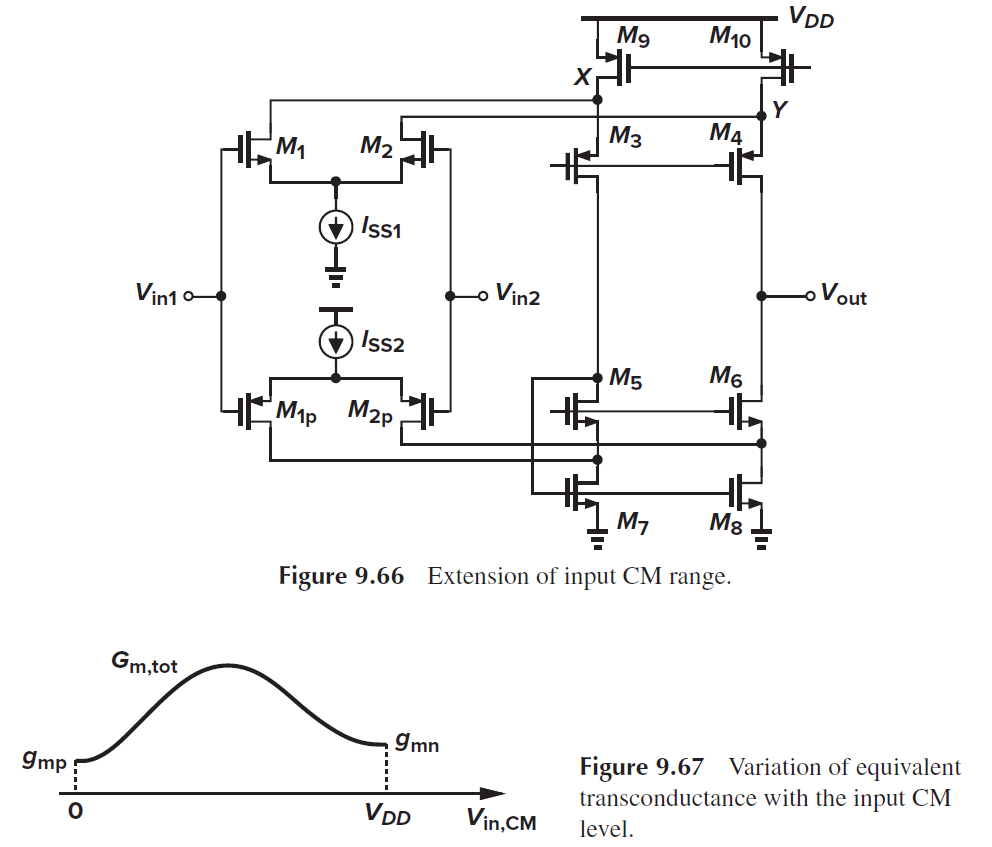

slew rate考虑在大信号输入Vin发生跳变时, 输出Vout的变化.

考虑下图当V1>>V2时或者V1<<V2, 环路断了, 全部Iss电流去充电CL或者去放电CL, 电路处于线性区.

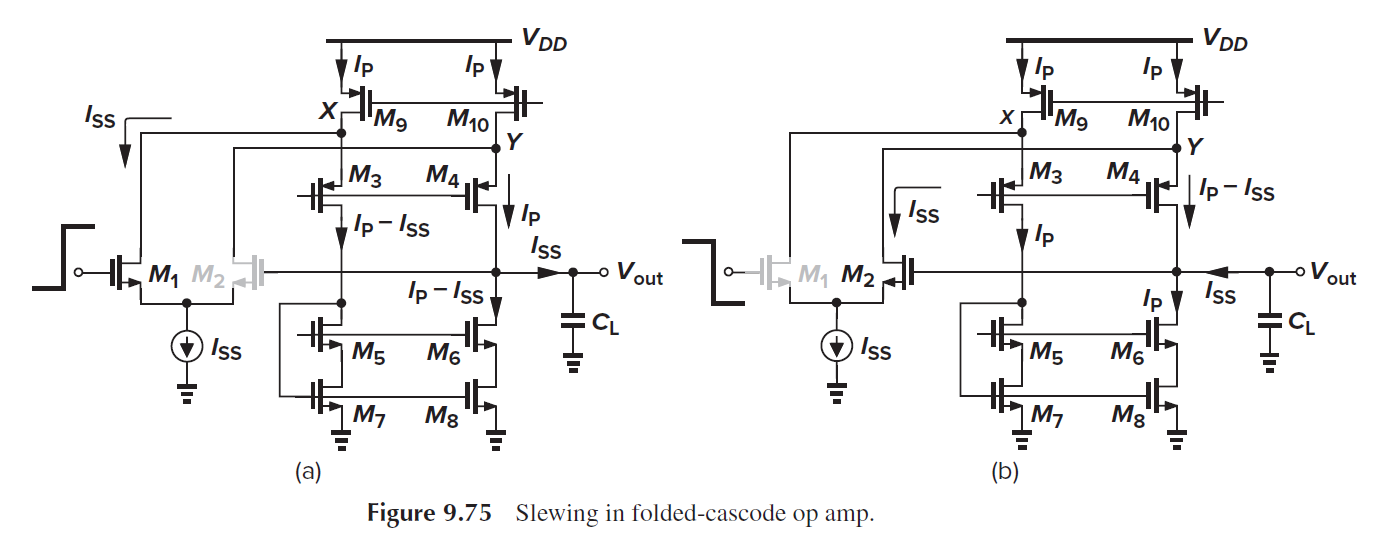

对于folded-cascode slew rate分析如下. 在实际电路中取IP≈Iss, 因此 Slew rate=Iss/CL,

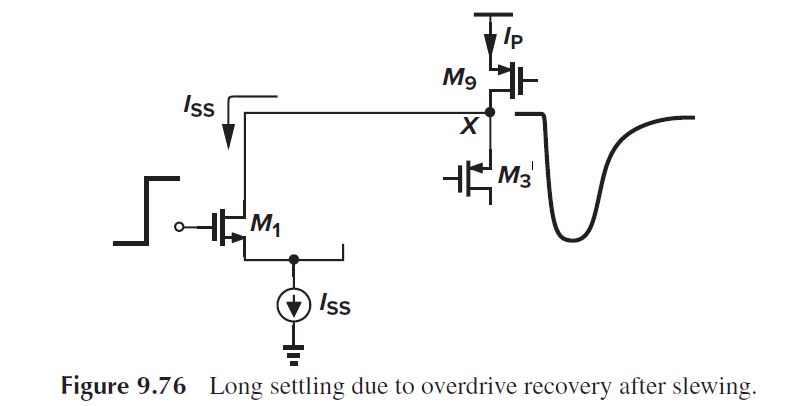

如果设计Iss>Ip, 在slew阶段, X点会先下降再上升

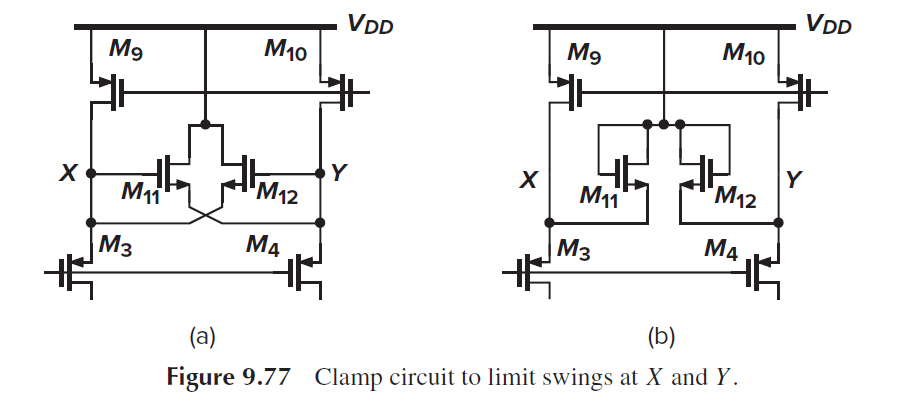

解决办法可以加clamp电路来限制X和Y点的最低值.

如何增加slew rate呢?

在不改变负载电容CL情况下, Iss需要增加. 为了保持相同的输出摆幅, 所有管子的W/L需要增加. 功耗增加了, 但是gm*ro, 即开环增益保持不变.

9.10 High-Slew-Rate Op Amps

为了提高slew rate, 可以增加电流.

9.10.1 One-Stage Op Amps

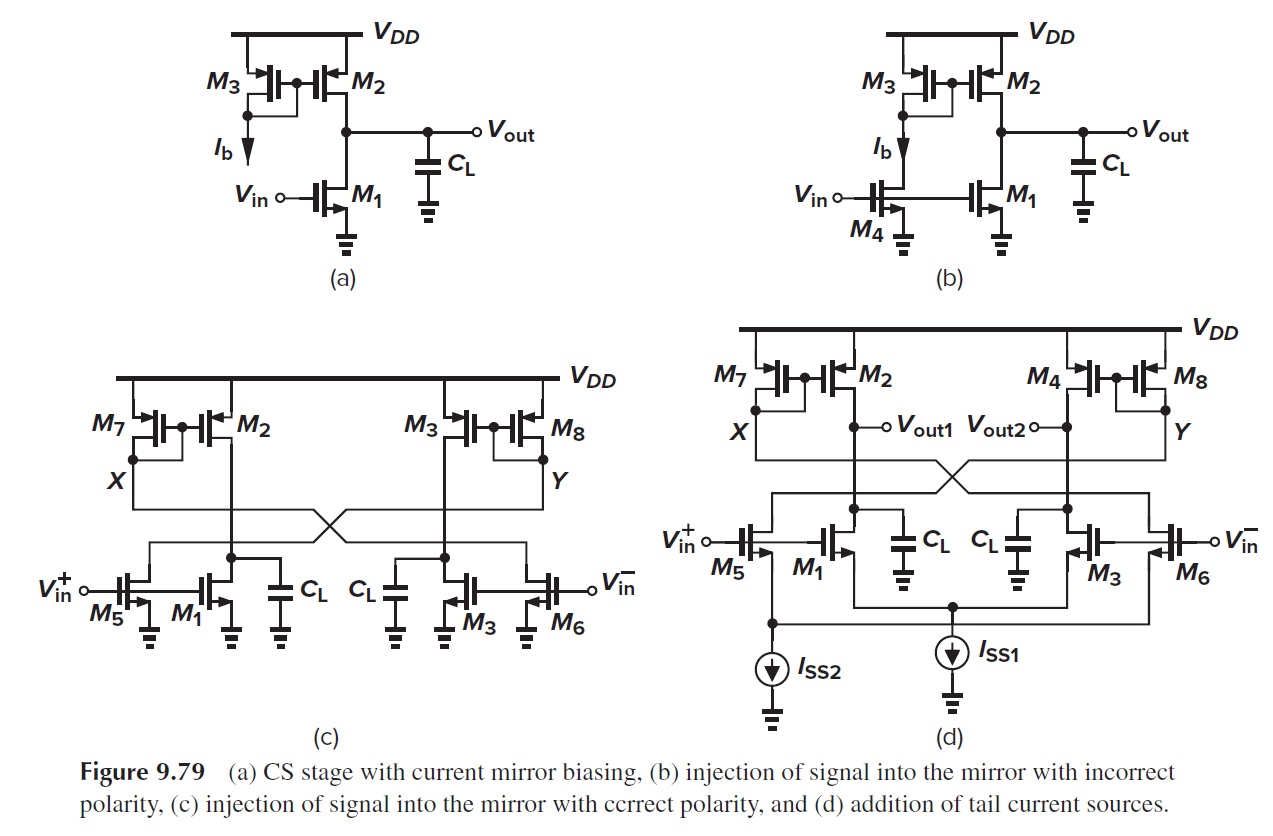

考虑上图, 对于c)当Vin+上升, 对应Vin-下降, 这样 CL充电/放电更快.

d) 通过添加尾电流源, 提高输入共模抑制比, Vin+上升, Vout1下降速率 Iss1/CL, Vout2上升速率为Iss2 (W4/W8) /CL. 因此Vout1-Vout2差分速率为Iss1/CL+Iss2 (W4/W8) /CL.

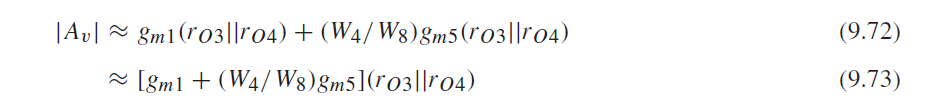

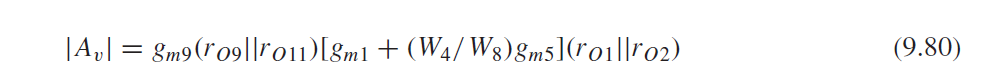

d)小信号增益为

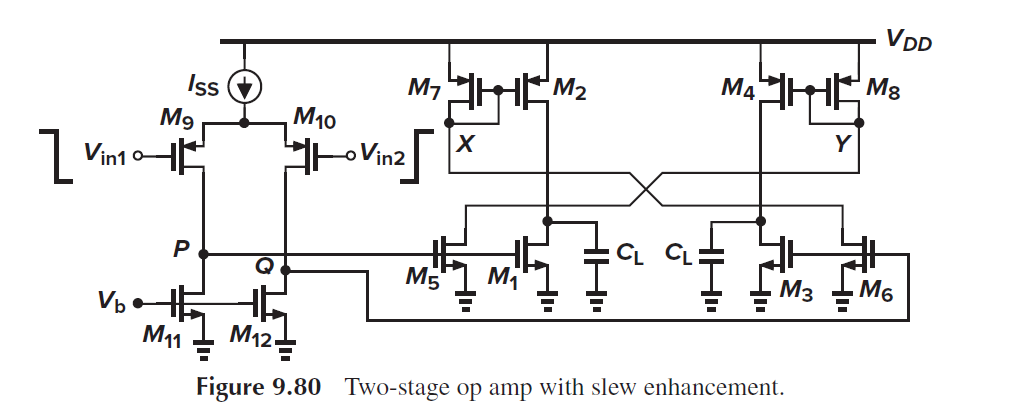

9.10.2 Two-Stage Op Amps

两级高slew rate结构参考下图

小信号增益为

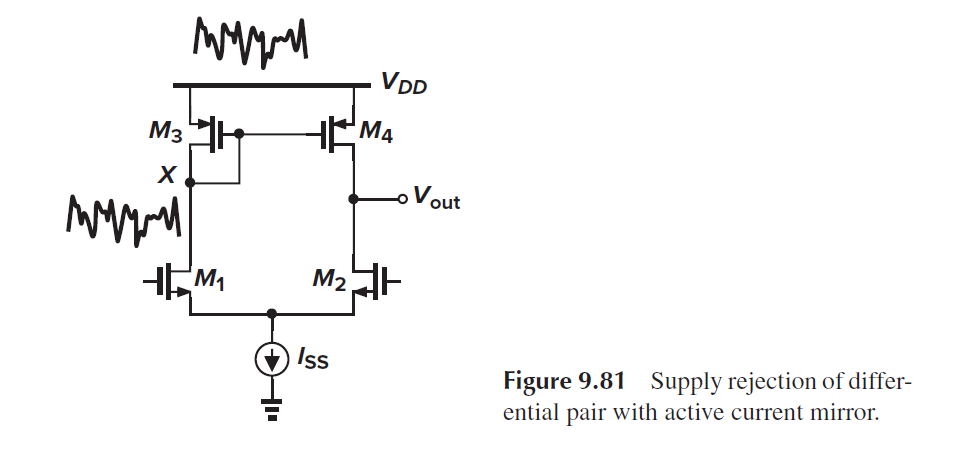

9.11 Power Supply Rejectio

PSRR 定义为输出到输入的Gain / supply到输出的Gain.

对于下图的五管运放, 其Vout=X=VDD-Vsg, 因此supply到输出的Gain=1, 因此 PSRR=gmN (rOP || rON)

9.12 Noise in Op Amps

对于低噪声应用, 我们关心输入噪声.

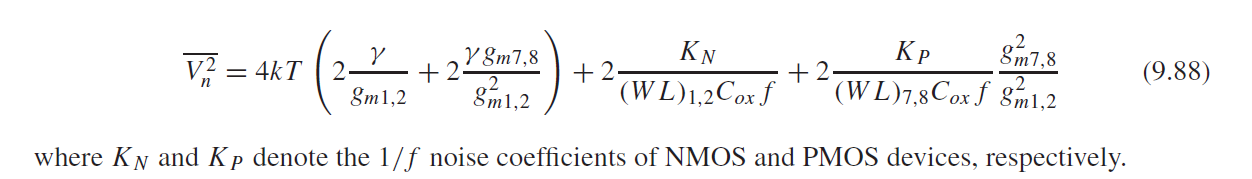

对于telescopic运放, 输入噪声来源主要是输入对管M1-M2, 和负载管M7-M8

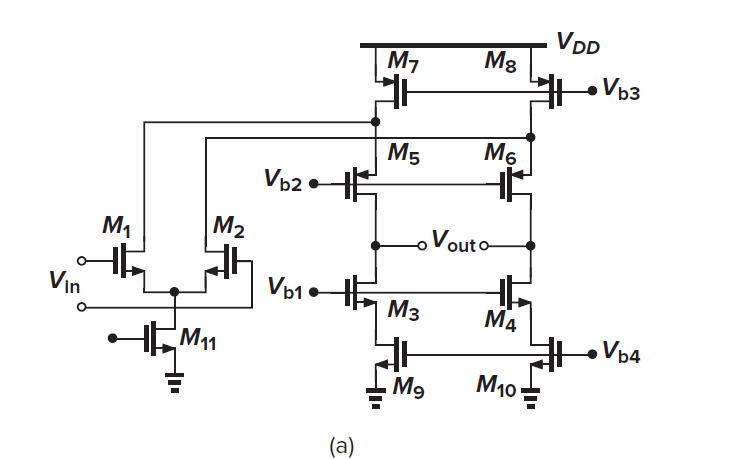

对于folded casecode

输入噪声

为了减小噪声, 需要降低M7,M8的gm, 增加M1,M2的gm.

![[Java]面向对象-抽象类/方法接口适配器设计模式](https://i-blog.csdnimg.cn/direct/4104db4399254460a555f2d696c86daf.png)