【RISC-V设计-04】- RISC-V处理器设计K0A之架构

文章目录

- 【RISC-V设计-04】- RISC-V处理器设计K0A之架构

- 1. 简介

- 2. 主要特点

- 3. 结构框图

- 4. 指令列表

- 5. CSR指令集

- 6. 中断返回指令

- 7. 总结

1. 简介

在前几篇文章中,介绍了RISC-V处理器的结构和指令集,从本篇文章开始,介绍一个最简单的RISC-V内核,仅支持RV32E(和RV32I指令一致,但支持16个通用寄存器),并命名为RISCV-K0A。RISCV-K0A是一个超轻量级的RISCV CPU内核,采用冯诺依曼结构,两级流水线,指令集为RV32E指令集(即整数指令集,16个通用寄存器),支持16个中断源。内核较为精简,面积极小、功耗低。

2. 主要特点

- RV32E+Zicsr指令集;

- 16个通用寄存器;

- 仅支持机器模式;

- 支持特权指令MRET;

- 实现了44条指令的处理;

- 两级流水线,取指、执行两个阶段;

- 冯诺依曼结构,指令总线和数据总线共享;

- 20位地址总线,最大支持1MByte地址空间;

- 支持16个外部中断源,支持晚到中断、咬尾中断;

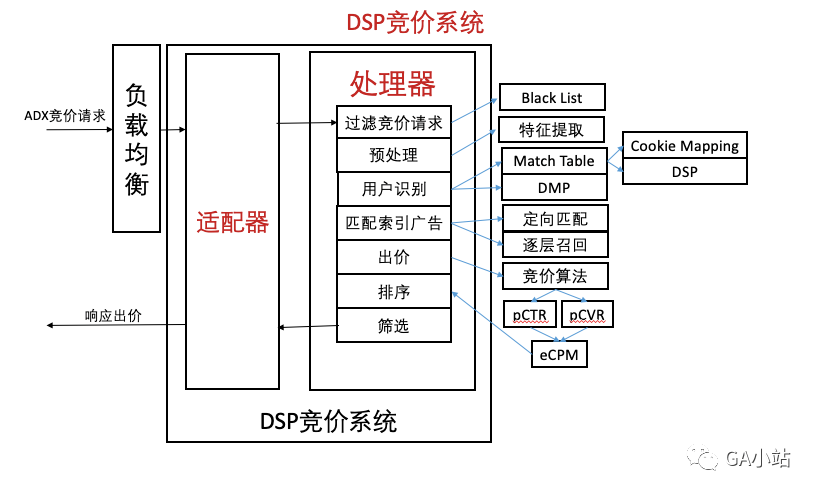

3. 结构框图

BMU :总线管理单元(Bus Management Unit)

IDU :指令译码单元(Instr Decoder Unit)

ALU :算术逻辑单元(Arithmetic and Logic Unit)

GPR :通用寄存器(General Purpose Register)

CIC :核内中断控制器(Core Interrupt Contoller)

CSR :控制与状态寄存器(Control and Status Register)

4. 指令列表

| 序号 | 类型 | 指令 | 周期 | 功能 | 说明 |

|---|---|---|---|---|---|

| 1 | RV32I | ADDI | 1 | Rd = Rs + imm | 立即数加法 |

| 2 | RV32I | SLTI | 1 | Rd = Rs < imm ? 1’b1 : 1’b0 | 立即数有符号小于 |

| 3 | RV32I | SLTIU | 1 | Rd = Rs < imm ? 1’b1 : 1’b0 | 立即数无符号小于 |

| 4 | RV32I | XORI | 1 | Rd = Rs ^ imm | 立即数异或 |

| 5 | RV32I | ORI | 1 | Rd = Rs | imm | 立即数逻辑或 |

| 6 | RV32I | ANDI | 1 | Rd = Rs & imm | 立即数逻辑与 |

| 7 | RV32I | SLLI | 1 | Rd = Rs << imm[4:0] | 立即数逻辑左移 |

| 8 | RV32I | SRLI | 1 | Rd = Rs >> imm[4:0] | 立即数逻辑右移 |

| 9 | RV32I | SRAI | 1 | Rd = Rs >>> imm[4:0] | 立即数算术右移 |

| 10 | RV32I | ADD | 1 | Rd = Rs1 + Rs2 | 寄存器加法 |

| 11 | RV32I | SUB | 1 | Rd = Rs1 - Rs2 | 寄存器减法 |

| 12 | RV32I | SLL | 1 | Rd = Rs1 << Rs2 | 寄存器逻辑左移 |

| 13 | RV32I | SLT | 1 | Rd = Rs1 < Rs2 ? 1’b1 : 1’b0 | 寄存器有符号小于 |

| 14 | RV32I | SLTU | 1 | Rd = Rs1 < Rs2 ? 1’b1 : 1’b0 | 寄存器无符号小于 |

| 15 | RV32I | XOR | 1 | Rd = Rs1 ^ Rs2 | 寄存器异或 |

| 16 | RV32I | SRL | 1 | Rd = Rs1 >> Rs2 | 寄存器逻辑右移 |

| 17 | RV32I | SRA | 1 | Rd = Rs1 >>> Rs2 | 寄存器算术右移 |

| 18 | RV32I | OR | 1 | Rd = Rs1 | Rs2 | 寄存器逻辑或 |

| 19 | RV32I | AND | 1 | Rd = Rs1 & Rs2 | 寄存器逻辑与 |

| 20 | RV32I | LB | 2 | Rd = M[Rs1 + imm] | 加载字节,有符号扩展 |

| 21 | RV32I | LBU | 2 | Rd = M[Rs1 + imm] | 加载字节,无符号扩展 |

| 22 | RV32I | LH | 2 | Rd = M[Rs1 + imm] | 加载半字,有符号扩展 |

| 23 | RV32I | LHU | 2 | Rd = M[Rs1 + imm] | 加载半字,无符号扩展 |

| 24 | RV32I | LW | 2 | Rd = M[Rs1 + imm] | 加载字 |

| 25 | RV32I | SB | 1 | M[Rs1+imm] = Rs2 | 存储字节 |

| 26 | RV32I | SH | 1 | M[Rs1+imm] = Rs2 | 存储半字 |

| 27 | RV32I | SW | 1 | M[Rs1+imm] = Rs2 | 存储字 |

| 28 | RV32I | JAL | 1 | Rd = PC + 4; PC = PC + imm | 带返回的PC跳转 |

| 29 | RV32I | JALR | 1 | Rd = PC + 4; PC = Rs + imm | 带返回的寄存器跳转 |

| 30 | RV32I | BEQ | 1 | if(Rs1 == Rs2) PC = PC + imm | 相等跳转 |

| 31 | RV32I | BNE | 1 | if(Rs1 != Rs2) PC = PC + imm | 不等跳转 |

| 32 | RV32I | BLT | 1 | if(Rs1 < Rs2) PC = PC + imm | 小于跳转 |

| 33 | RV32I | BGE | 1 | if(Rs1 >= Rs2) PC = PC + imm | 大于等于跳转 |

| 34 | RV32I | BLTU | 1 | if(Rs1 < Rs2) PC = PC + imm | 无符号,小于跳转 |

| 35 | RV32I | BGEU | 1 | if(Rs1 >= Rs2) PC = PC + imm | 无符号,大于等于跳转 |

| 36 | RV32I | LUI | 1 | Rd = imm << 12 | 加载立即数 |

| 37 | RV32I | AUIPC | 1 | Rd = PC + (imm<<12) | 根据PC加载立即数 |

| 38 | Zicsr | CSRRW | 1 | Rd = CSR; CSR = Rd | CSR寄存器读、写 |

| 39 | Zicsr | CSRRS | 1 | Rd = CSR; CSR = CSR | Rd | CSR寄存器读、置1 |

| 40 | Zicsr | CSRRC | 1 | Rd = CSR; CSR = CSR & ~Rd | CSR寄存器读、清0 |

| 41 | Zicsr | CSRRWI | 1 | Rd = CSR; CSR = imm | CSR立即数读、写 |

| 42 | Zicsr | CSRRSI | 1 | Rd = CSR; CSR = CSR | imm | CSR立即数读、置1 |

| 43 | Zicsr | CSRRCI | 1 | Rd = CSR; CSR = CSR & ~imm | CSR立即数读、清0 |

| 44 | Priv | MRET | 1 | PC = mepc | 中断返回指令 |

5. CSR指令集

| I型指令:CSR指令 | ||||||

|---|---|---|---|---|---|---|

| 序号 | 指令 |

31

20

|

19

15

|

14

12

|

11

7

|

6

0

|

| 1 | CSRRW | csr | rs | 001 | rd | 1110011 |

| 2 | CSRRS | csr | rs | 010 | rd | 1110011 |

| 3 | CSRRC | csr | rs | 011 | rd | 1110011 |

| 4 | CSRRWI | csr | rs | 001 | rd | 1110011 |

| 5 | CSRRSI | csr | rs | 010 | rd | 1110011 |

| 6 | CSRRCI | csr | rs | 011 | rd | 1110011 |

CSRRW:

指令形式:csrrw rd, csr, rs1

指令功能:CSR寄存器读后写。记csr值为t,将rs1写入csr,再将t写入rd。

CSRRS:

指令形式:csrrs rd, csr, rs1

指令功能:CSR寄存器读后置位。记csr值为t,将t和rs1的按位或结果写入csr,再将t 写入rd。

CSRRC:

指令形式:csrrc rd, csr, rs1

指令功能:CSR寄存器读后清位。记csr值为t,将rs1的反码和t按位与,结果写入csr,再将t写入rd。

CSRRWI:

指令形式:csrrwi rd, csr, zimm[4:0]

指令功能:CSR寄存器读后写立即数。将csr 的值复制到rd 中,再将5 位立即数zimm 的零扩展结果写入csr。

CSRRSI:

指令形式:csrrsi rd, csr, zimm[4:0]

指令功能:CSR寄存器读后置位立即数。记csr 的值为t,将5 位立即数zimm 零扩展后,和t 按位或,结果写入csr,再将t 写入rd(csr 中的第5 及更高的位不变)。

CSRRCI:

指令形式:csrrci rd, csr, zimm[4:0]

指令功能:CSR寄存器读后清位立即数。记csr 的值为t,将5 位立即数zimm 零扩展后的反码和t 按位与,结果写入csr,再将t 写入rd(csr 中的第5 及更高的位不变)。

6. 中断返回指令

| 特殊型指令:中断返回指令 | ||||||||

|---|---|---|---|---|---|---|---|---|

| 序号 | 指令 |

31

28

|

27

24

|

23

20

|

19

15

|

14

12

|

11

7

|

6

0

|

| 1 | MRET | 0011 | 0000 | 0010 | 00000 | 000 | 00000 | 1100111 |

7. 总结

本文重点阐述了 RISCV-K0A 的基本特性、整体架构以及所支持的指令集。RISCV-K0A 致力于打造一个最为简单的 RISC-V 处理器,其在面积和功耗方面有着强烈的追求,正因如此,并不支持在线调试这一功能。在后续的几篇文章中,将会对各个子模块分别进行介绍。