文章目录

前言

背景介绍

SCI通信

Transmitter

Receiver

SCI中断

分析和应用

总结

参考资料

前言

见《【研发日记】嵌入式处理器技能解锁(一)——多任务异步执行调度的三种方法》

背景介绍

近期使用TI C2000 DSP做的一个嵌入式系统开发项目中,在使用它的SCI(serial communication interface)通信时,遇到了挺多费时费力的事情。所以利用周末时间,在这些方面深入研究了一下,解锁了一些新技能。把它总结出来,以备将来翻看。

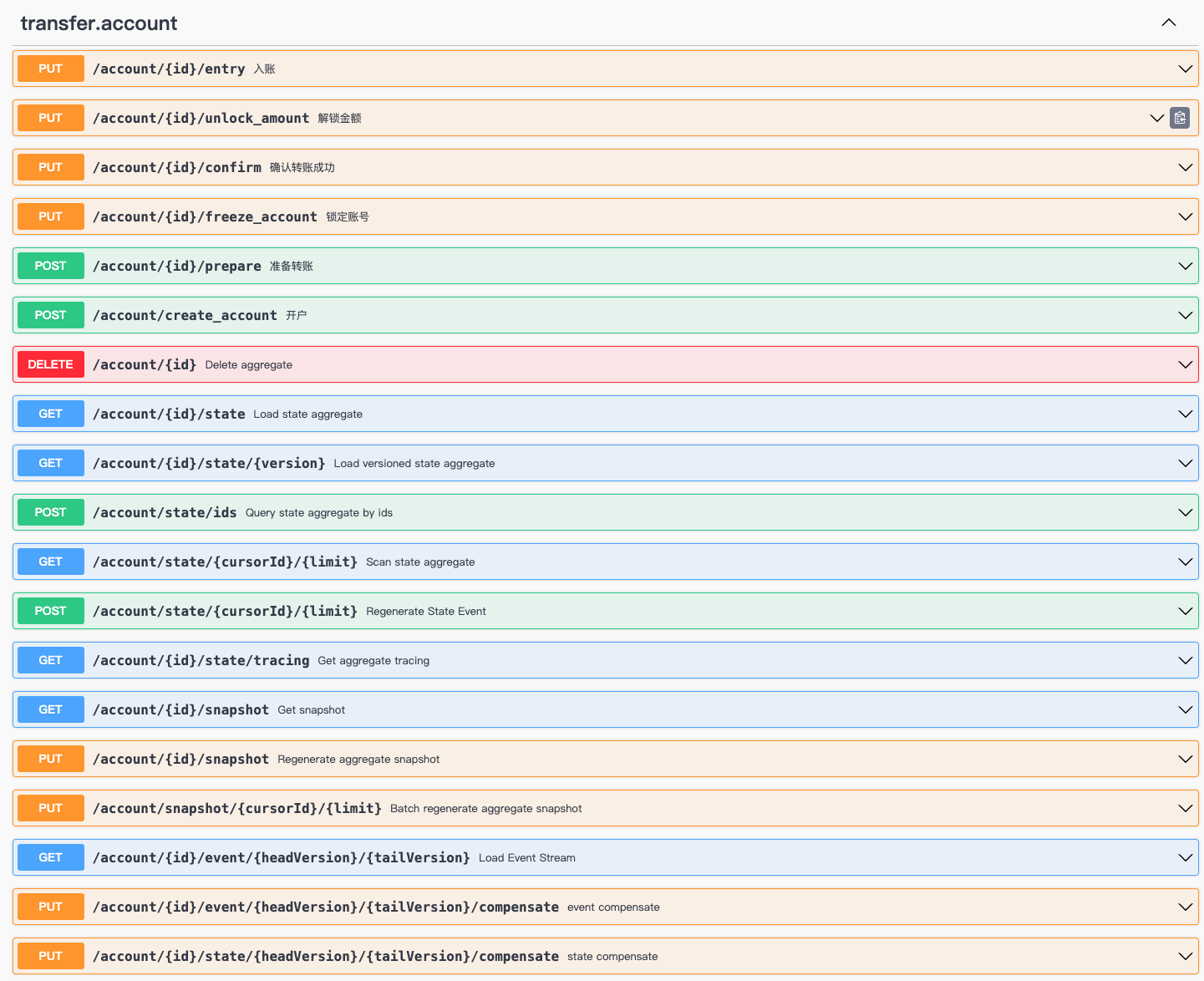

SCI通信

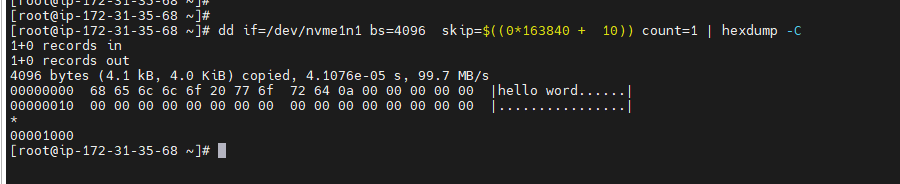

TI C2000 DSP中的SCI(serial communication interface)通信,跟常见的UART(Universal Asynchronous Receiver/Transmitter)非常类似,大部分内容都是相同的。由于这个芯片的DSP定位,所以SCI相比UART多了一些增强的功能,比如SCI支持多处理器之间以总线的方式寻址通信,并具备专门的地址匹配功能。再比如transmitter和receiver都有16-level deep FIFO,可以16 frame统一处理一次,能够减轻CPU的负荷。SCI在芯片中的工作原理如下图所示:

Tips:CPU和SCI通信接口之间的数据传递有两条路径可选,分别是经过FIFO和不经过FIFO,通过上图中的寄存器SCIFFENA即可配置。

Transmitter

SCI的数据发送过程如下:

第一步,CPU将Bytes到移SCITXBUF。如果是非FIFO模式,一次只能移一个Byte,等着发送完了才能移下一个。如果是FIFO模式,最多可以依次移入16个Bytes,然后他们在FIFO中排队往外发送。

第二步,shift register (TXSHF)逐个将SCITXBUF或FIFO中的Byte包装上头、尾和奇偶校验位,组成完整Frame。

第三步,Tx line上以串行0和1的形式发送出去。

发送应用的代码示例如下:

//*****************************************************************************

// SCI_writeCharArray

//*****************************************************************************

void

SCI_writeCharArray(uint32_t base, const uint16_t * const array,

uint16_t length)

{

// Check the arguments.

ASSERT(SCI_isBaseValid(base));

uint16_t i;

// Check if FIFO enhancement is enabled.

if(SCI_isFIFOEnabled(base))

{

// FIFO is enabled.

// For loop to write (Blocking) 'length' number of characters

for(i = 0U; i < length; i++)

{

// Wait until space is available in the transmit FIFO.

while(SCI_getTxFIFOStatus(base) == SCI_FIFO_TX15)

{

}

// Send a char.

SCI_O_TXBUF = array[i];

}

}

else

{

// FIFO is not enabled.

// For loop to write (Blocking) 'length' number of characters

for(i = 0U; i < length; i++)

{

// Wait until space is available in the transmit buffer.

while(!SCI_isSpaceAvailableNonFIFO(base))

{

}

// Send a char.

SCI_O_TXBUF = array[i];

}

}

}

Receiver

SCI的数据接收过程如下:

第一步,Rx line上由0和1组成的串行数据到达Rx pin,

第二步,RXSHF把包含头、尾和校验位的完整Frame转换成有效的Byte,然后分两种路径,要么直接放入receiver buffer register (SCIRXBUF),要么依次压入RX FIFO,同时产生一个RX interrupt送到CPU。

第三步,CPU得到interrupt request后就可以执行一个ISR(中断服务程序),把SCIRXBUF(1 Byte)中的Byte移到可用的变量或数组中。如果芯片配置的是FIFO模式,那么FIFO(16 Byte)中的Byte会以先进先出的顺序逐个自动进入SCIRXBUF,直至FIFO拿空为止。

接收应用的代码示例如下:

//*****************************************************************************

// SCI_readCharArray

//*****************************************************************************

void SCI_readCharArray(uint32_t base, uint16_t * const array, uint16_t length)

{

// Check the arguments.

ASSERT(SCI_isBaseValid(base));

uint16_t i;

// Check if FIFO enhancement is enabled.

if(SCI_isFIFOEnabled(base))

{

// FIFO is enabled.

// For loop to read (Blocking) 'length' number of characters

for(i = 0U; i < length; i++)

{

// Wait until a character is available in the receive FIFO.

while(SCI_getRxFIFOStatus(base) == SCI_FIFO_RX0)

{

}

// Return the character from the receive buffer.

array[i] = (uint8_t)SCI_O_RXBUF;

}

}

else

{

// FIFO is not enabled.

// For loop to read (Blocking) 'length' number of characters

for(i = 0U; i < length; i++)

{

// Wait until a character is available in the receive buffer.

while(!SCI_isDataAvailableNonFIFO(base))

{

}

// Return the character from the receive buffer.

array[i] = (uint8_t)SCI_O_RXBUF;

}

}

}

SCI中断

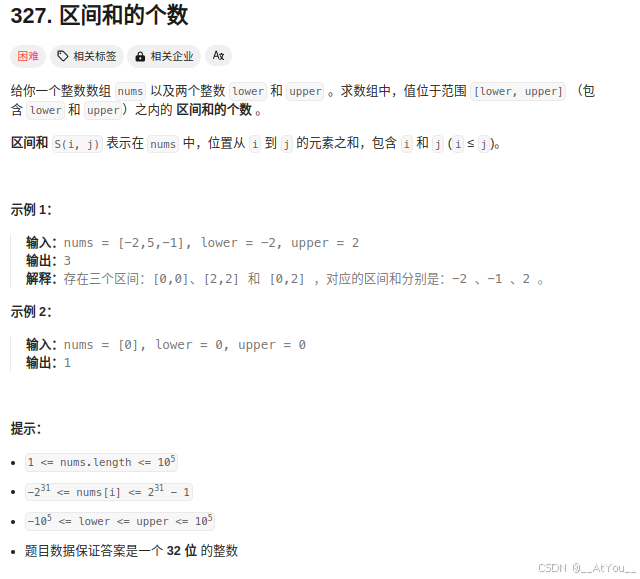

在TI C2000 DSP的中断向量表中有两个SCI相关的中断,分别是TXINT和RXINT。这两个中断各自都有多个触发源,每个触发源都有自己的Flag寄存器和Enable寄存器,使能寄存器用来配置该触发源是否触发CPU中断。下面以接收中断为例来进行讲解:

RX FIFO Interrupt可以配置为0~16 Level,Level 0表示不使能RX FIFO Interrupt,Level 1表示RX FIFO中的Bytes个数是1的时候触发中断,Level 2示RX FIFO中的Bytes个数是2的时候触发中断,以此类推。FIFO的中断Level可以配置成各种值,但是实际可压入的Bytes空间不会变。这里的Level设置越小就会越频繁的触发CPU中断,软件对SCI的相应速度也越快,但是CPU的负荷也会越高,需要开发人员根据自己的应用设计一个合适的Level。

Break Detect Interrupt是指在Frame中出现了bit间隔,芯片是以Start位和Stop位作为判定的条件。如果一个Frame定义的是11bit,那么收到Start位之后如果10个bit时间过去了还没收到Stop位,那就判定为Break Detect Error,寄存器BRKDT就会置1。

这些寄存器通常以SCIRXBUF接收到完整Frame为时间点进行update,一旦置1后不会自动清0,需要在RXINT的ISR(中断服务程序)写代码处理。ISR执行完之前,又有新的Frame进来时会出错,官方建议ISR的执行时间要小于0.125 bit time。

分析和应用

TI C2000 DSP的SCI通信具有协议简洁,易于调试和快速开发的特点,因此被广泛应用于物联网的嵌入式系统中。这些特点决定了它适用于数据量不大,通信速率要求不高,传输距离较近的应用场景,并且对刚入门的开发人员非常友好。

总结

以上就是本人在研发中使用嵌入式处理器的SCI通信时,一些个人理解和分析的总结,主要介绍了SCI通信的工作原理,展示了具体的使用方法,并对比分析了它的特点和适用场景。

后续还会分享另外几个最近解锁的嵌入式处理器新技能,欢迎评论区留言、点赞、收藏和关注,这些鼓励和支持都将成文本人持续分享的动力。

另外,上述例程使用的Demo工程,可以到笔者的主页查找和下载。

参考资料

TMS320F28003x Real-Time Microcontrollers datasheet.pdf

版权声明,原创文章,转载和引用请注明出处和链接,侵权必究!