前言

VGA接口是一个很有历史的接口,全称为Video Graphics Array(VGA)视频图形阵列,是IBM公司在1987年随着PS/2一起推出的使用模拟信号的一种视频传输标准。时至今日,这个接口依然还在大量使用,因为这个接口具有成本低、结构简单、应用灵活的优点。VGA接口是一种广泛应用于计算机显示系统的标准模拟视频接口

正文

一、VGA接口驱动设计验证

1.项目需求

进行vga接口驱动设计验证(软件测试),使得图像数据通过VGA接口在显示器上显示一种颜色。

2.技术介绍

首先我们看一下 VGA 接口的电路原理图

VGA_VS是场脉冲信号,VGA_HS是行脉冲信号,VGA_R/G/B对应颜色数据。FPGA芯片直接与 VGA 接口相连,并没有特殊的外部芯片,也就是说,唯一要关注的可能就是它的显示原理和时序了。那么接下来我们具体来看一下 VGA 的扫描原理是什么。

VGA 扫描方式 显示器扫描方式分为逐行扫描和隔行扫描:逐行扫描是扫描从屏幕左上角一 点开始,从左向右逐点扫描,每扫描完一行,电子束回到屏幕的左边下一行的起 始位置,在这期间,CRT 对电子束进行消隐,每行结束时,用行同步信号进行同 步;当扫描完所有的行,形成一帧,用场同步信号进行场同步,并使扫描回到屏 幕左上方,同时进行场消隐,开始下一帧。隔行扫描是指电子束扫描时每隔一行 扫一线,扫完一屏后再返回来扫描剩下的线,隔行扫描的显示器闪烁快速,可能 会使使用者眼睛疲劳(本实验采用逐行扫描的方式)

扫描原理清楚以后,紧接着大家再来看看 VGA 的行、列同步时序

列同步时序

行同步时序

VGA 中定义行时序和列时序都需要同步脉冲(a 段),显示后沿(b 段)、显 示时序段(c 段)和显示前沿(d 段)四部分。VGA 工业标准显示模式要求:行 同步、列同步都为负极性,即同步脉冲要求是负脉冲。

由 VGA 行时序可知:每一行都有一个负极性行同步脉冲(a 段),是数据行 的结束标志,同时也是下一行的开始标志。在同步脉冲之后为显示后沿(b 段), 在显示时序段(c 段)显示器为亮的过程,RGB 数据驱动一行上的每一个像素点, 从而显示一行。在一行的最后为显示前沿(d 段)。在显示时间段之外没有图像 投射到屏幕,而是插入消隐信号。同步脉冲、显示后沿和显示前沿都是在行消隐 间隔内,当消隐有效时,RGB 信号无效,屏幕不显示数据。

以本实验的显示标准 800*600*60Hz 为例。(800 为列数,600 为行数, 60Hz 为刷新一屏的频率)

行时序:屏幕对应的行数为 628(a+b+c+d=e 段),其中 600(c 段)为 显示行;每行均有行同步信号(a 段),为 4 个行周期的低电平;

列时序:每个显示行包括 1056 列(a+b+c+d=e 段),其中 800(c 段) 为有效显示区,每一行有一个行同步信号(a 段),为 128 个行周期的低电 平。

如何确定将一行扫描完?

需要根据显示标准规定的扫描时钟控制产生一个列计数器cnt_hs,扫描时钟为扫描一个像素点时钟;刷新时钟表示扫描完所有像素点的时间作为该时钟的周期。当列计数器计数到最大值时,表示当前行所有的像素点扫描完成。

如何确定将所有行扫描完成或者说将所有像素点扫描完?

可以产生一个行计数器cnt_vs,其变化一次的条件为:列计数器计数到最大值,当列计数器等于最大值且行计数器等于最大值时,将所有的像素点扫描完成。

以显示标准为:640*480*60为例进行设计验证

640表示有效显示区域的列数,480表示有效显示区域的行数,60hz表示刷新时钟,包含的像素点个数为:800*525,扫描一个像素点的时间为:(1/60)/(800*525),那么扫描一个像素点时钟频率为:800*525*60=25_200_000hz;

行计数器的最大值为:524,列计数器的最大值为:799

通过列计数器cnt_hs控制产生行同步信号vga_hs,当列计数器cnt_hs小于96时,行同步信号vga_hs等于0,其余值时等于1;

通过行计数器cnht_vs控制产生列同步信号vga_vs,将列同步信号称为场同步信号,,当行计数器cnt_vs小于2时,场同步信号vga_vs等于0,其余值时等于1;

3.顶层架构

调用锁相环产生时钟,vga_ctrl产生对应的场脉冲信号行脉冲信号,颜色数据。

4.端口描述

| clk | 板载时钟(50Mhz) |

| rst_n | 复位按键(低电平有效) |

| vga_hs | 行脉冲信号 |

| vga_vs | 场脉冲信号 |

| [7:0] vga_rgb | 颜色数据信号,高三位表示红色, 中间三位表示绿色,低两位表示蓝色 |

二、代码验证

vga_ctrl模块:产生对应的场脉冲信号行脉冲信号,颜色数据。

module vga_ctrl(

input clk,

input rst_n,

output vga_hs,

output vga_vs,

output [7:0] vga_rgb

);

reg [9:0] cnt_hs;//列计数器

reg [9:0] cnt_vs;//行计数器

wire hs_en;//列有效显示区域

wire vs_en;//行有效显示区域

wire volid_en;//有效显示区域

always @(posedge clk,negedge rst_n)

begin

if(rst_n == 0)

cnt_hs <= 10'd0;

else

if(cnt_hs < 799)//行扫描

cnt_hs <= cnt_hs + 10'd1;

else

cnt_hs <= 10'd0;

end

always @(posedge clk,negedge rst_n)

begin

if(rst_n == 0)

cnt_vs <= 10'd0;

else

if(cnt_hs == 799)

if(cnt_vs < 524)//列扫描,每行扫描完加1

cnt_vs <= cnt_vs + 10'd1;

else

cnt_vs <= 10'd0;

else

cnt_vs <= cnt_vs;

end

assign vga_hs = (cnt_hs < 96)?1'b0:1'b1;//同步信号经过后拉低

assign vga_vs = (cnt_vs < 2)?1'b0:1'b1;//同步信号经过后后拉低

assign hs_en = ((cnt_hs > 143)&&(cnt_hs < 784))?1'b1:1'b0;

assign vs_en = ((cnt_vs > 34)&&(cnt_vs < 515))?1'b1:1'b0;

assign volid_en = hs_en & vs_en;//显示的有效区域

assign vga_rgb = (volid_en == 1)?8'b111_000_00:8'd0;

endmodule vga_driver模块:顶层连线

module vga_driver(

input clk,

input rst_n,

output vga_hs,//行脉冲信号,由列计数器控制产生

output vga_vs,//场脉冲信号,由行计数器控制产生

output [7:0] vga_rgb/*颜色数据信号,高三位表示红色,

中间三位表示绿色,低两位表示蓝色*/

);

wire vga_clk;//25.2mhz

wire locked;

vga_pll vga_pll_inst (

.areset ( ~rst_n ),

.inclk0 ( clk ),

.c0 ( vga_clk ),

.locked ( locked )

);

vga_ctrl vga_ctrl_inst(

.clk(vga_clk),

.rst_n(locked),

.vga_hs(vga_hs),

.vga_vs(vga_vs),

.vga_rgb(vga_rgb)

);

endmodule 仿真代码:

`timescale 1ns/1ps

module vga_driver_tb;

reg clk;

reg rst_n;

wire vga_hs;

wire vga_vs;

wire [7:0] vga_rgb;

vga_driver vga_driver_instx(

.clk(clk),

.rst_n(rst_n),

.vga_hs(vga_hs),//行脉冲信号,由列计数器控制产生

.vga_vs(vga_vs),//场脉冲信号,由行计数器控制产生

.vga_rgb(vga_rgb)/*颜色数据信号,高三位表示红色,

中间三位表示绿色,低两位表示蓝色*/

);

initial clk = 0;

always #10 clk = ~clk;

initial begin

rst_n = 0;

#200

rst_n = 1;

#1000

$stop;

end

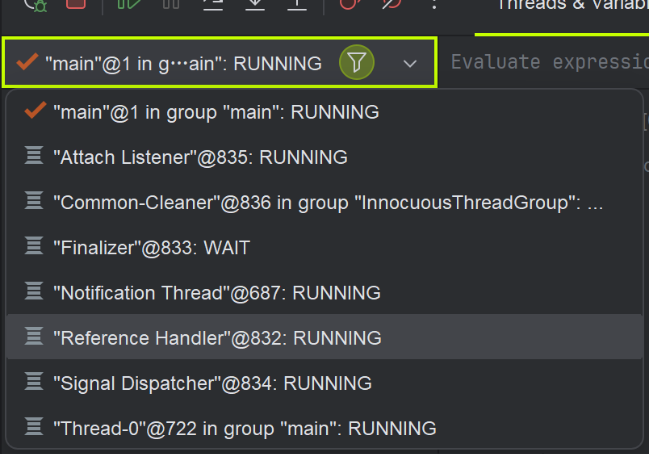

endmodule 三、仿真验证

观察仿真波形图,在显示数据扫描完消隐区后,数据正常显示

参考资料

VGA接口

VGA显示原理