一、概述

在使用了这么久的FPGA之后,才发现前面光发了各个设计的设计文件和测试问价,还没有发过怎么利用我们编写的代码进行仿真和使用软件进行工程建立和下载验证的过程,今天就补发一篇Quartus的工程建立以及下载仿真全过程。

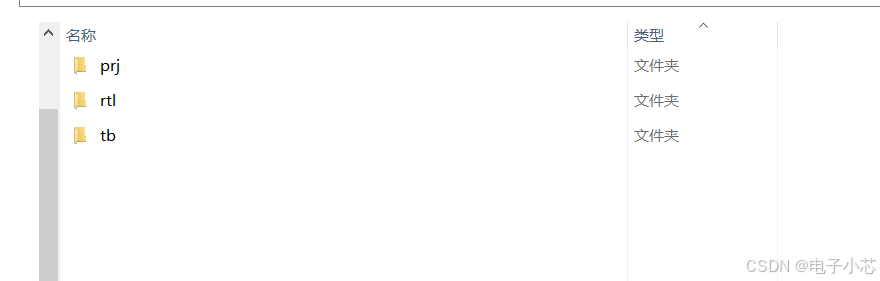

二、文件夹建立

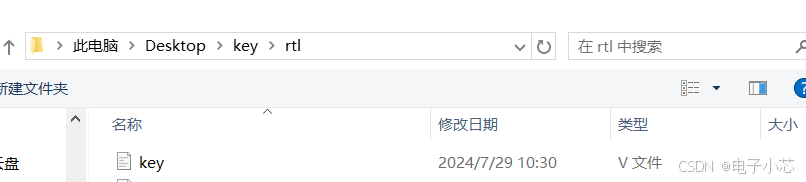

首先新建一个文件夹,根据设计对其进行重命名(不能使用中文),接着在此目录之下新建三个基础文件夹prj、rtl(src)、tb,用于存放我们的工程,设计文件和测试文件。如图:

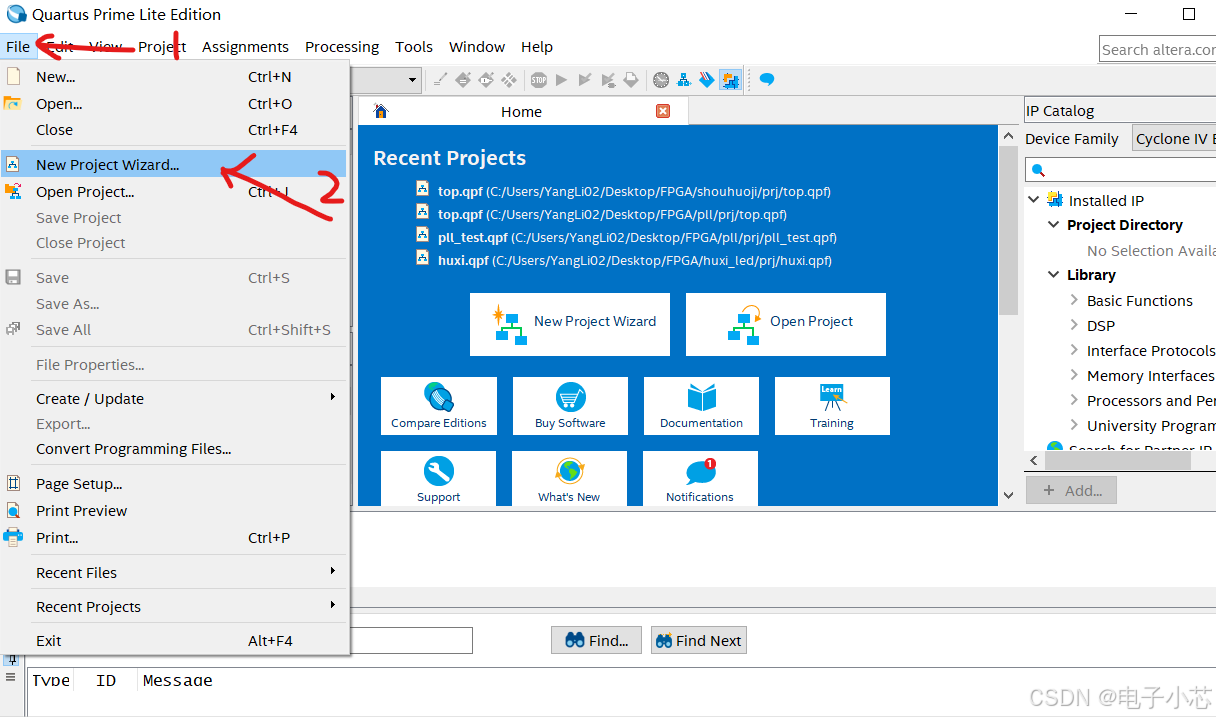

三、建立工程

1、打开Quartus软件,点击file—>New Project Wizard。

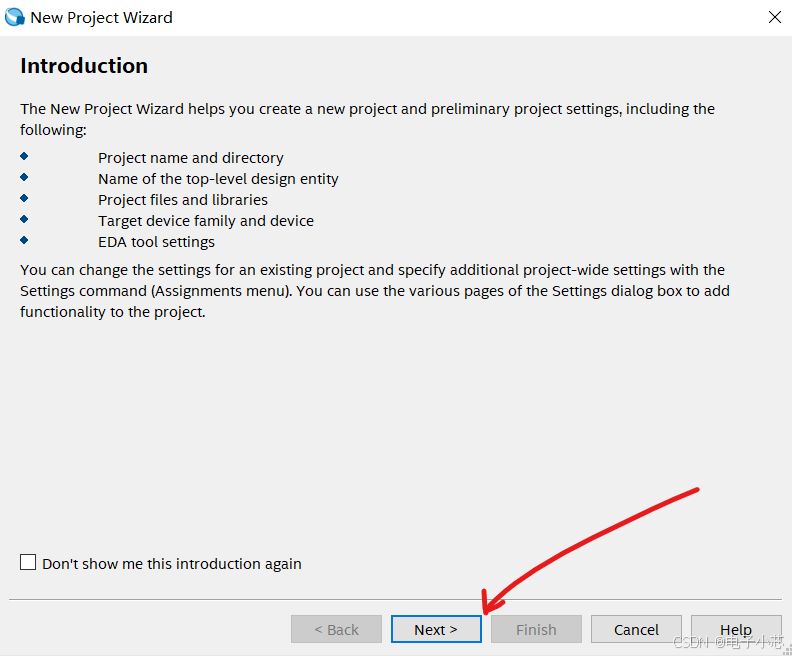

2、在introduction 界面直接点击next

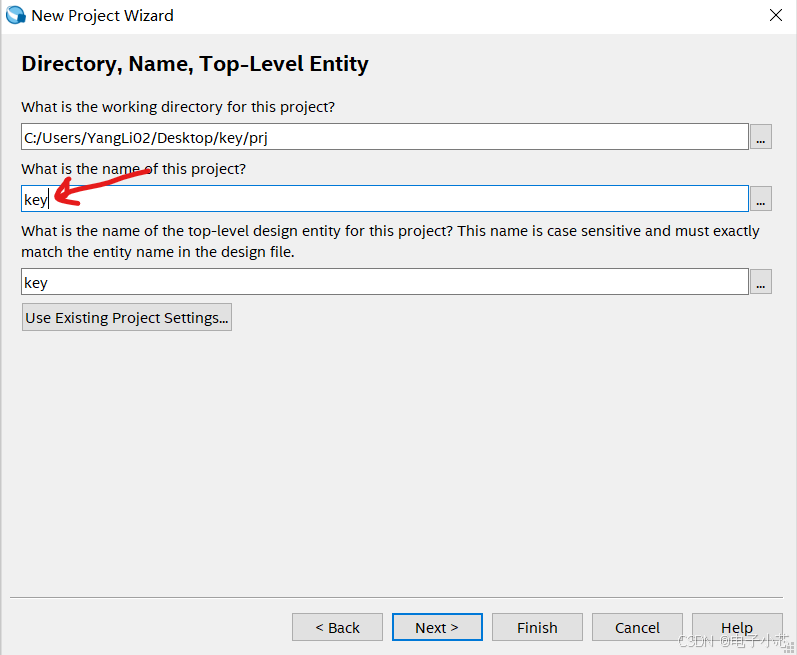

3、在Directory,Name,Top-Level Entity界面先点击“...”浏览,选择我们前面建立的文件的prj里面进行保存。

在下面这行里面是本次工程的顶层文件的名字(这里一般就按照我们编写代码时顶层文件的名字一致,不然会报错,后面如果顶层文件改变时也可以直接进行顶层文件的设置)。这里我就直接命名为key,之后点击next。

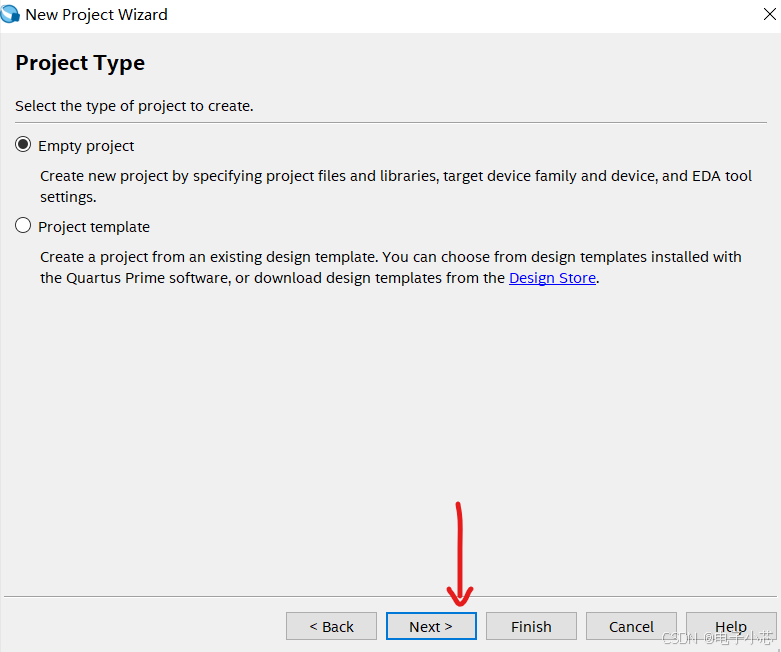

4、 在Project Type界面默认就行,点击next。

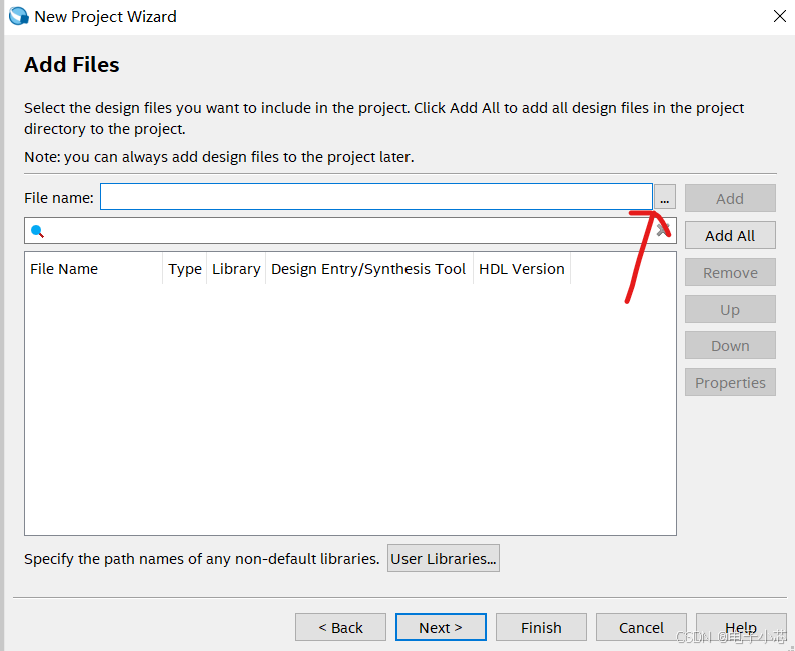

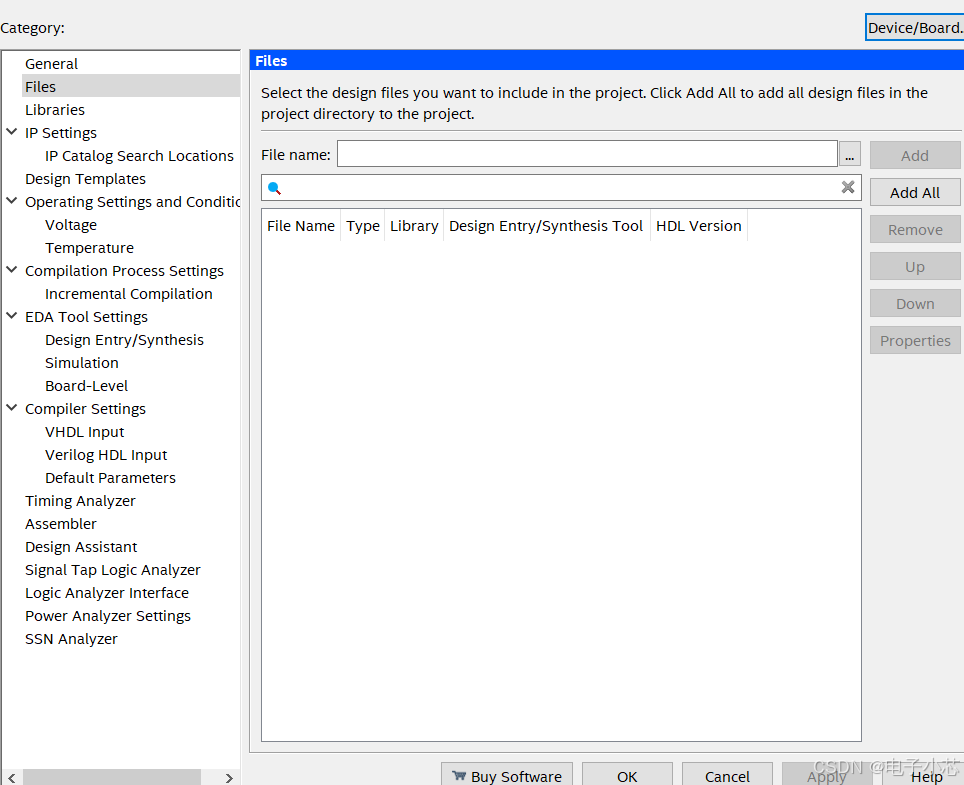

5、在addFile界面是添加我们编写的设计文件,这里如果在之前就已经编写好所需要的设计文件的话,就可以在这里进行添加,如果没有就直接跳过,在后面编写好之后添加即可。这里说一下添加设计文件过程:点击浏览-->选择我们建立的文件下的rtl(src)文件存放的设计文件,选择相应的设计文件即可。

下图中画圈的就是我们添加的设计文件,之后点击next。

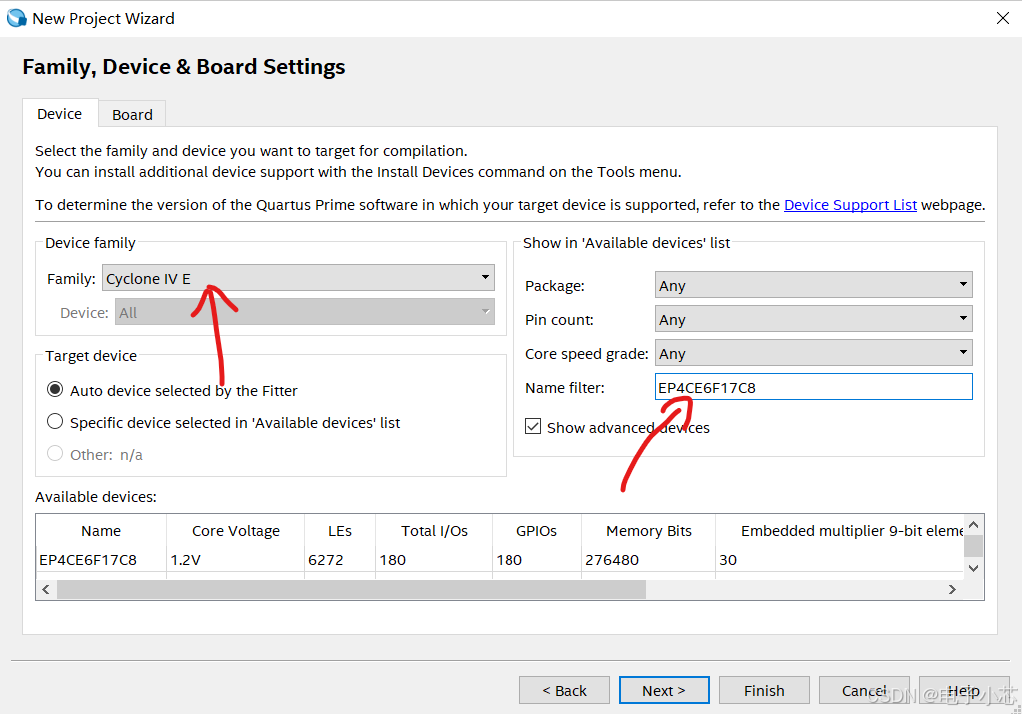

6、接着就是芯片型号的选择,在family选择芯片包,在Name filter填写芯片型号,我们使用的芯片信息就会出现在下面的devices界面。

6、接着就是芯片型号的选择,在family选择芯片包,在Name filter填写芯片型号,我们使用的芯片信息就会出现在下面的devices界面。

7、仿真类型的选择

这里我使用的是Altera型号的芯片,可以根据用户的芯片类型进行仿真类型选择(这里就是前面文章说过的联合仿真,如果是使用独立仿真的用户,这里就可以不用进行选择)。点击next。

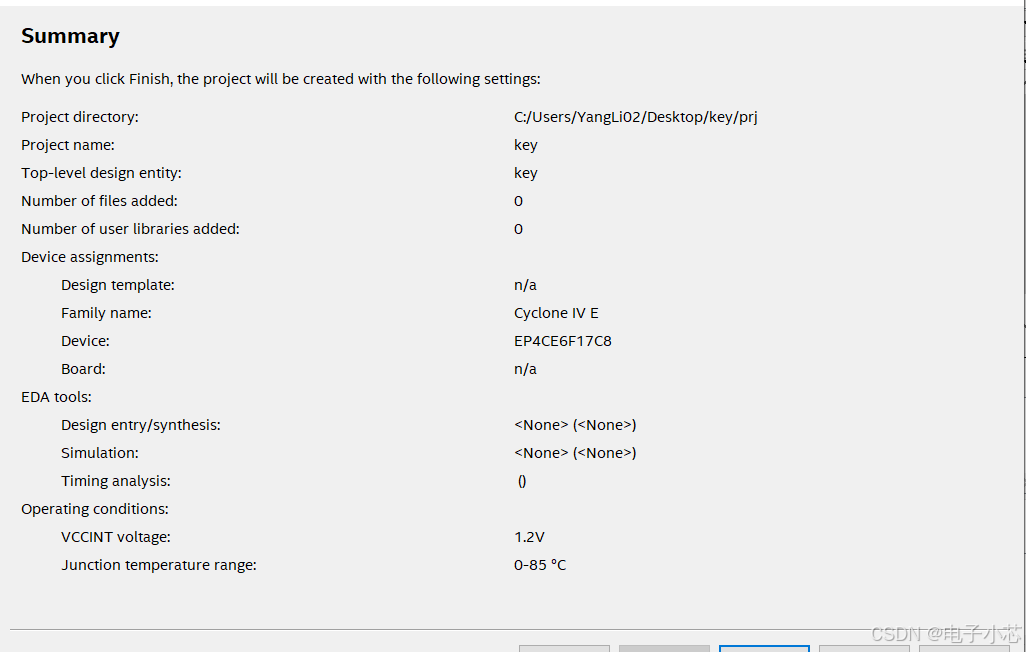

8、最后在Summary界面可以看到芯片的资源使用情况,直接点击finish工程就创建完成了。

8、最后在Summary界面可以看到芯片的资源使用情况,直接点击finish工程就创建完成了。

四、下载调试

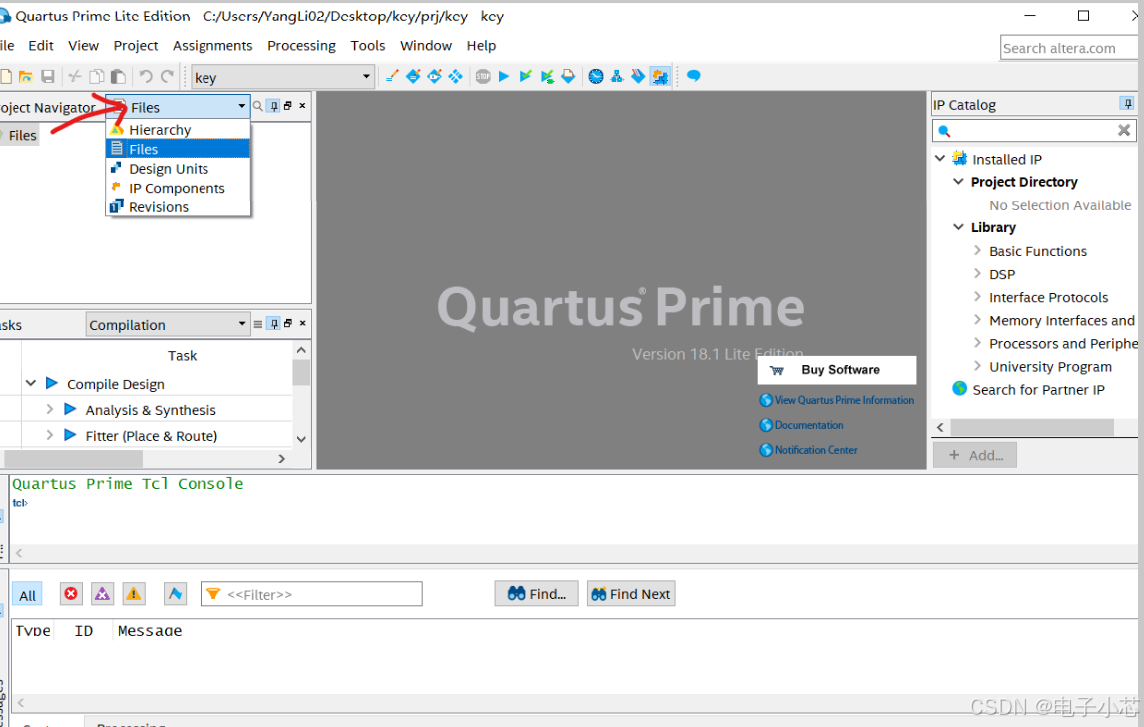

1、设计文件的添加

这里只针对在前面创建工程时没有添加设计文件的情况。如果添加过了就可以直接跳过这一步。在object Navigator 里面选择files选项出现一个文件夹。

在这是我们双击文件夹就可以进入添加设计文件的界面。

这里的界面和我们在创建文件时添加设计文件的页面是同一个,操作方法按照前面添加的步骤操作即可。

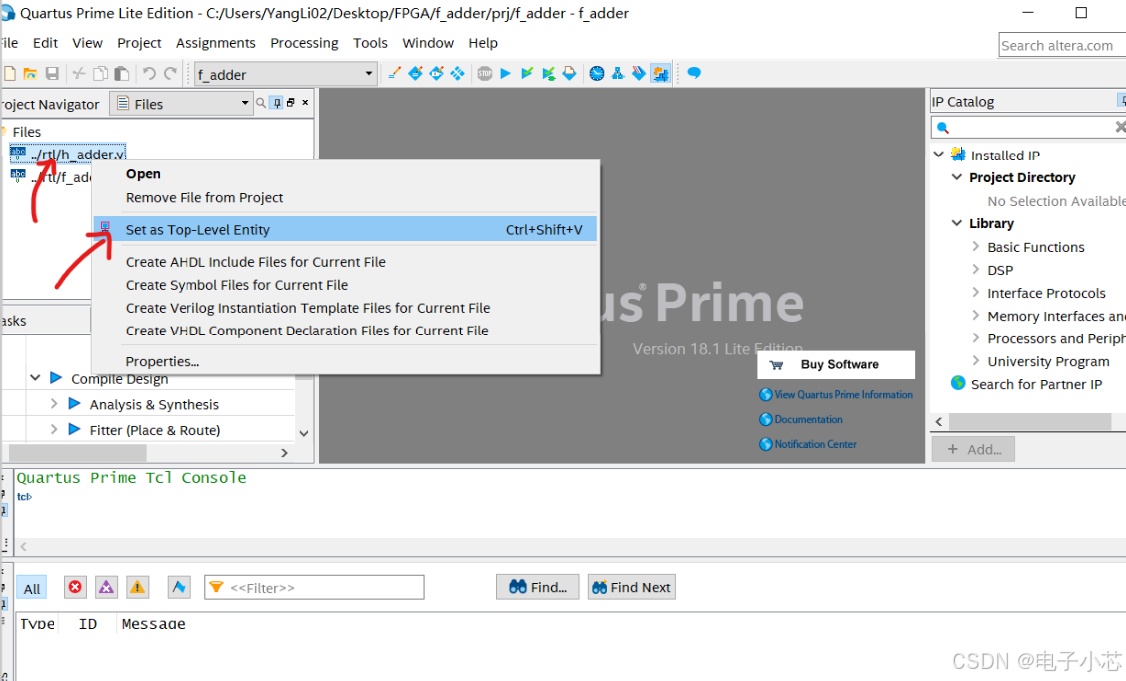

2、顶层文件的选择

这个操作是针对在建立工程师顶层文件名称设置得不合适导致找不到顶层文件的问题操作的,没有问题就跳过这步。同样也是在object Navigator 里面的files这里,右键我们将要设置的顶层文件,选择Set as Top-Level Entity选项就可以设置我们所需要的顶层文件。

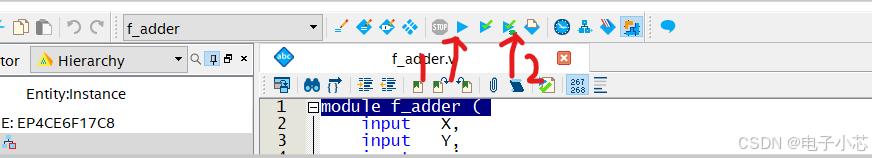

3、下载编译

图中1是全编译,2是分析综合,我们首先选择分析综合,看编写的程序是否有错。

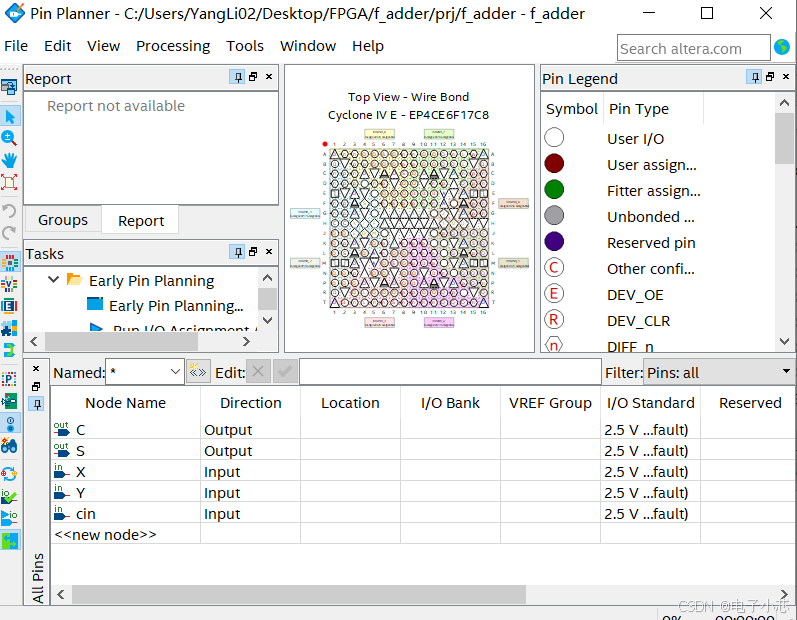

4、引脚配置

我们需要下板进行结果验证,那么就需要进行引脚配置,这里有三种配置方法,我就讲pin planner进行直接配置的方法。在图中我们查看相应的原理图,进行各个引脚的配置就行

5、功能仿真

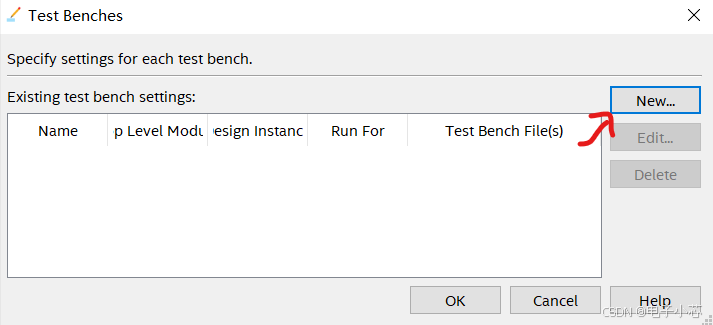

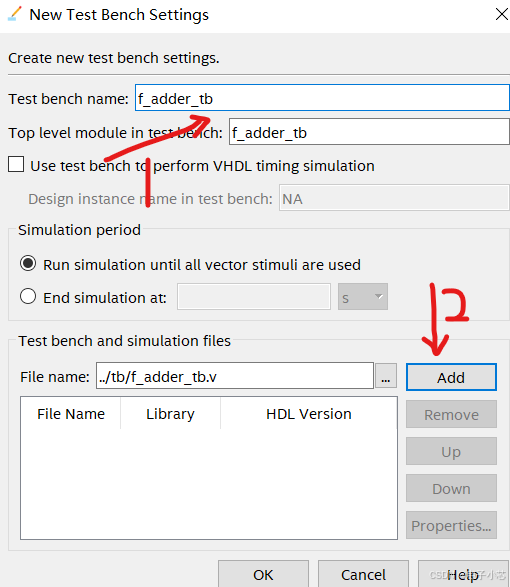

如果这里要在Quartus里面进行联合仿真,我们就要添加测试文件,如果不需要就跳过。

这里点击浏览之后选择我们的文件夹下的tb文件夹的测试文件即可。

这里我们选择好文件之后讲测试文件的名称复制到上面的框里,最后点击添加。

最后一直点击OK知道退出setting界面就可以了。

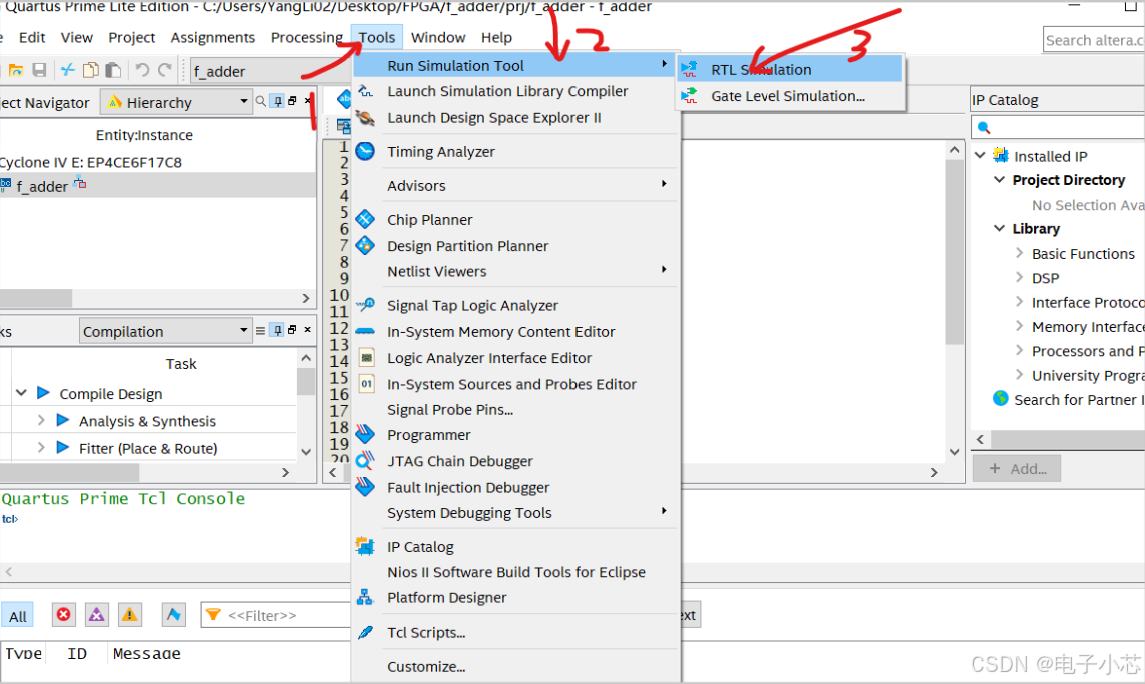

6、功能仿真

最后点击全编译之后等待编译完成,按照图中操作,我们就可以在Quartus进行modelsim仿真了。

7、下板验证

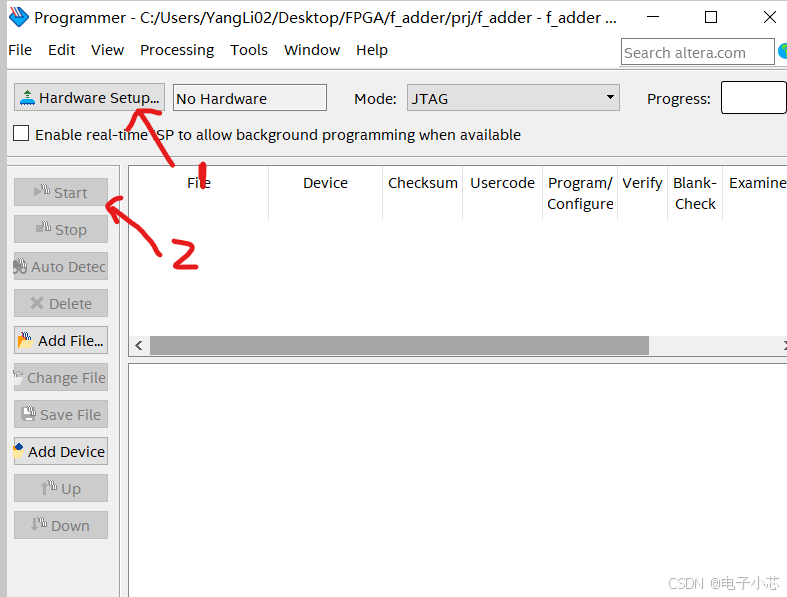

最后需要下载到开发板进行验证的按照此步骤操作(这里默认驱动已经安装好)。

这时我们将开发板接入电脑,一般情况下USB就会自动识别,我们只需要点击2下载即可,如果没有识别到USB,我们就点击1,手动选择USB即可。

这时我们将开发板接入电脑,一般情况下USB就会自动识别,我们只需要点击2下载即可,如果没有识别到USB,我们就点击1,手动选择USB即可。

到这里本次文章就结束了,不足之处欢迎点评。