目录

序言:

🏆🏆人生在世,成功并非易事,他需要破茧而出的决心,他需要永不放弃的信念,他需要水滴石穿的坚持,他需要自强不息的勇气,他需要无畏无惧的凛然。要想成功,你得付出沉重的代价。

触发器的特点

🌈一、基本RS触发器

🌈二、同步RS触发器

🌈三、JK触发器

🌈四、D触发器

🌈五、T触发器

🌈 六、同步RS触发器、JK触发器、D触发器、T触发器的共同点

序言:

本文章仅粉丝可见,望谅解🙏🙏

从本篇文章开始就进行电子笔记的一个汇总,属于个人的权限文章,所以设置为粉丝可见,再次望谅解🙏🙏

🏆🏆人生在世,成功并非易事,他需要破茧而出的决心,他需要永不放弃的信念,他需要水滴石穿的坚持,他需要自强不息的勇气,他需要无畏无惧的凛然。要想成功,你得付出沉重的代价。

时序逻辑电路是具有记忆功能的触发器及构成组合逻辑电路的门电路构成的。

时序逻辑电路的特点:任何时刻电路的输出状态不仅与当时的输入状态有关,还与电路的前一个状态有关(具有记忆功能)

触发器是构成时序逻辑电路的基本单元。

触发器按照结构可以分为:基本触发器和时钟触发器。

触发器按照逻辑功能可以分为:RS触发器、JK触发器、D触发器和T触发器。

触发器的特点

①具有两个稳定状态,0态和1态。

②基本触发器没有时钟控制。

③时钟触发器接收输入信号时,输出相应状态的时间受时钟脉冲的控制。

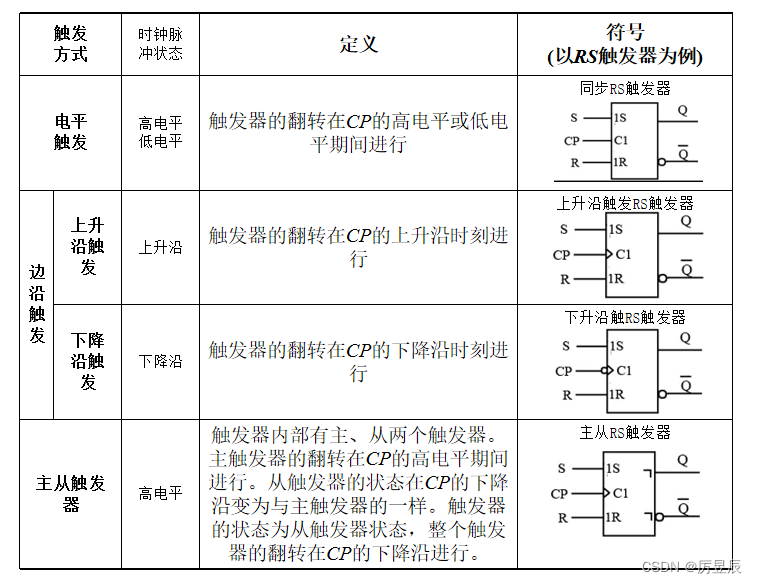

④触发方式有电平触发、边沿触发、主从触发。

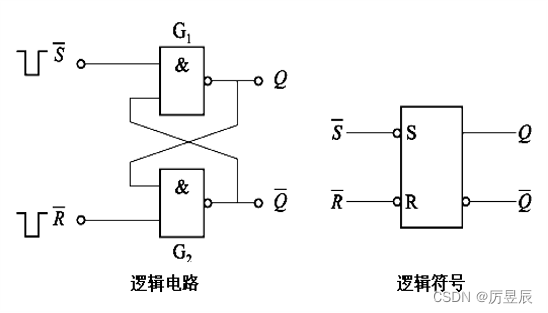

一、基本RS触发器

其逻辑功能见表:

注意:

①电路的初始状态用表示;电平触发后的状态用

表示。

②:置0端;

:置1端。非号表示低电平触发有效。

③基本RS触发器不受时钟的控制。

④避免,

端同时为0。

⑤或非门构成的基本RS触发器和与非门构成的基本RS触发器的特点相反。

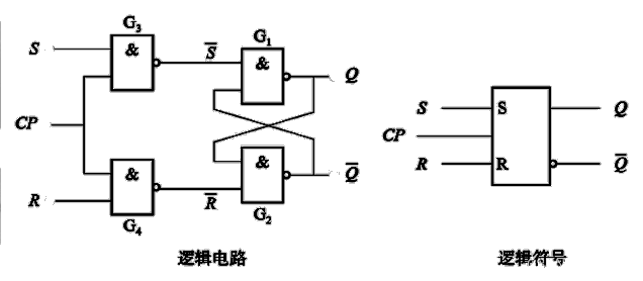

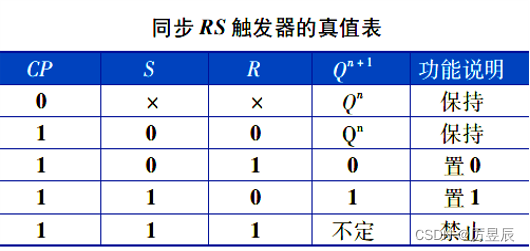

二、同步RS触发器

同步RS触发器是在基本RS触发器的基础上,增加了两个与非门G3,G4和一个时钟脉冲端CP。

其逻辑功能见表:

由时钟脉冲信号控制的基本RS触发器称为同步RS触发器。

注意:

①同步RS触发器为高电平触发方式;

②应避免R,S两端同时为1时出现的不定状态;

③同步RS触发器有两个缺点:输出有不定状态和空翻现象。

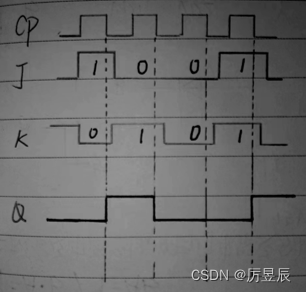

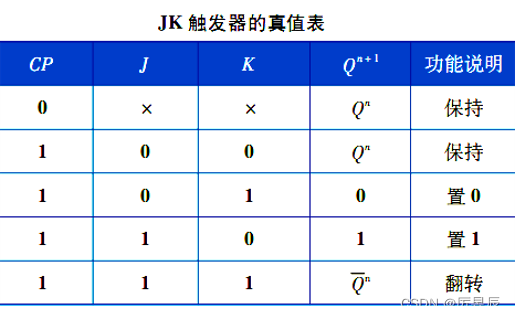

三、JK触发器

其逻辑功能见表:

注意:

①JK触发器的触发方式分为电平触发、上升沿触发、下降沿触发和主从触发。

②JK触发器能够克服不定状态及空翻现象。

③时钟CP端不带小圆圈,为上升沿触发。反之,则为下降沿触发。

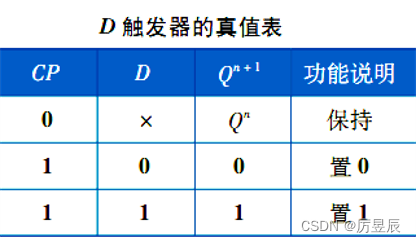

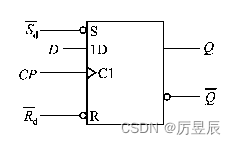

四、D触发器

其逻辑功能见表:

注意:

①常用集成D触发器为上升沿触发(74LS74)

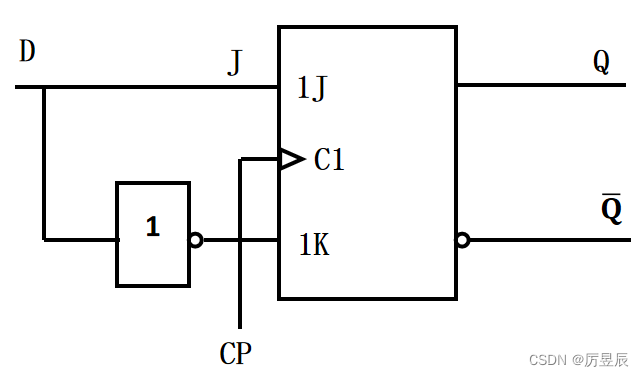

②在K端串联一非门后和J端连接,JK触发器→D触发器(相当于JK触发器J≠K的电路状态)。

eg:

上图是由JK触发器改造的D触发器。

:异步置1端(直接置1端)

:异步置0端(直接置0端)

*异步不受CP脉冲的控制。

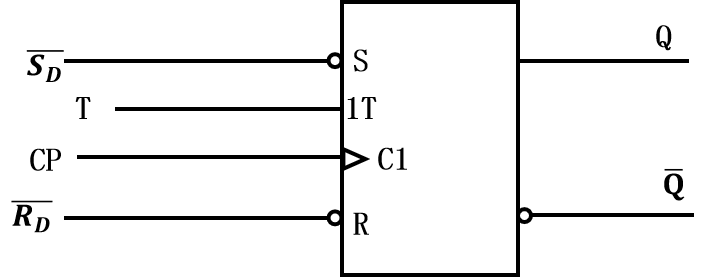

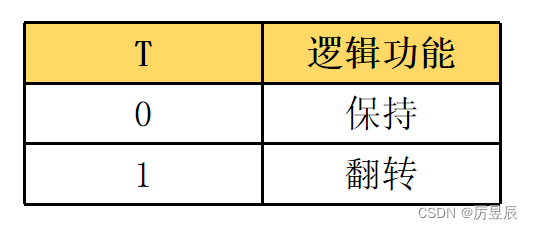

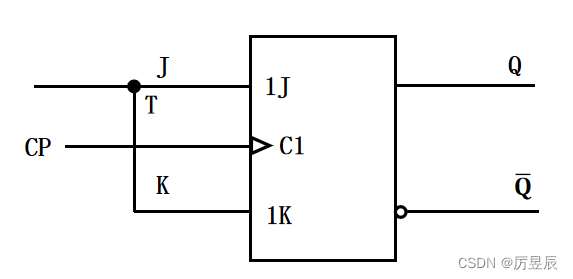

五、T触发器

其逻辑功能见表:

注意:

①常用集成T触发器为上升沿触发;

②将K端和J端并连,JK触发器可作T触发器使用(相当于JK触发器J=K的电路状态)

eg:

六、同步RS触发器、JK触发器、D触发器、T触发器的共同点

(1)都受CP脉冲的控制;

(2)通过在和

端加低电平都可使触发器直接置1或置0。

(3)JK、D、T触发器都可避免同步RS触发器的不定状态和空翻现象。

【小重点】

JK触发器的状态翻转发生在CP脉冲的下降沿时刻,而翻转后的状态则由CP下降沿到来前的J、K信号决定。

eg:JK触发器的初态为0,CP下降沿触发。