✨前言:

在CXL的验证测试中,对CXL Port做Link Disable和Hot Reset对比PCie的Port做相同的操作略有不同

✨1.CXL Extensions DVSEC for Ports

协议里我们可以找到CXL协议里的第八张内容里的CXL Extensions DVSEC for Ports里的Port Control Extensions (Offset 0Ch)寄存器中的说明这两个bit位

✨具体解释:

Bit 0: Unmask SBR (RW)

描述:当该位为0时,Bridge Control寄存器中的SBR位对该端口不起作用。当该位为1时,当Bridge Control中的SBR位被设置为1时,该端口会生成热重置(Hot Reset)。

默认值:0。

注意:当端口在PCIe模式或RCD模式下运行时,这字段对SBR功能没有影响,端口将遵循PCIe Base Specification。

Bit 1: Unmask Link Disable (RW)

描述:当该位为0时,Link Control寄存器中的Link Disable位对该端口不起作用。当该位为1时,当Link Control中的Link Disable位被设置为1时,该端口会禁用CXL连接,当Link Disable位被设置为0时,连接会重新启用。

默认值:0。

注意:当端口在PCIe模式或RCD模式下运行时,这字段对Link Disable功能没有影响,端口将遵循PCIe Base Specification。

所以要对CXL Port做hotreset和Link Disable的操作的时候需要将这两个bit位置上,不然做Link Disable和Hot Reset不会生效。

✨2.如何根据PCIe cfg space找到CXL的Port Control Extensions寄存器

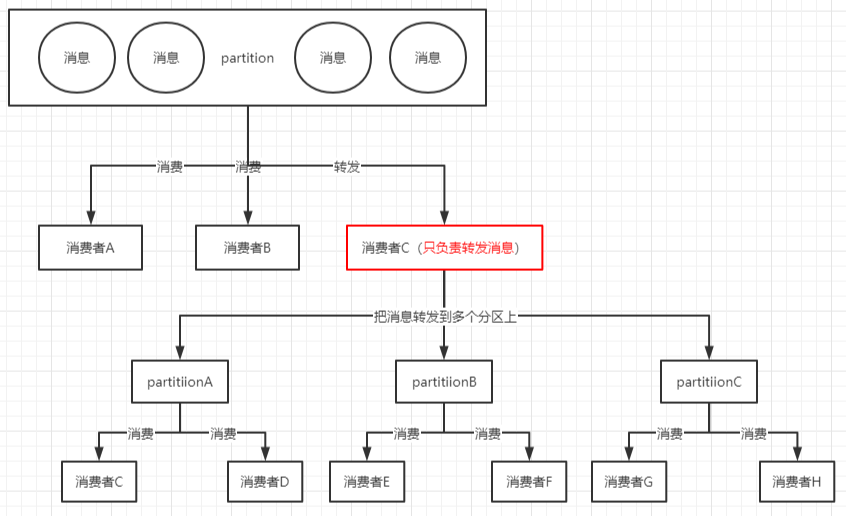

首先根据CXL协议里的Table 8-6指示的DVSEC ID 0003h来定位到CXL Extensions DVSEC for Ports的基地址,通过lspci工具 + rc的BDF号来查询ID-0003的capabilities为这个base addr。

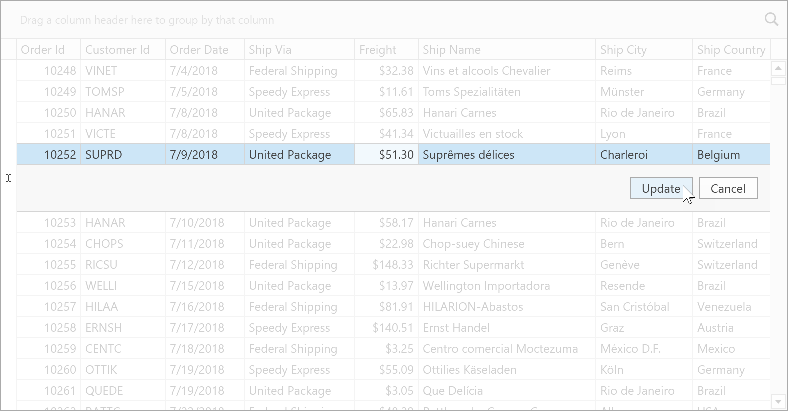

✨3.设置Port Control Extensions的unmask SBR的bit位

这里的寄存器偏移需要加上Port Control Extensions的偏移0xC,来设置即可,即刚刚的base addr 0x454+0xc,设置bit 0为1即可。