0. 测试环境

AC7840官方Demo板;

图莫斯0503

DSlogic U2Basic

使用引脚 输出脚:PB1 时钟:PB2,其他引脚可以不初始化,不接线

1. 数据解析

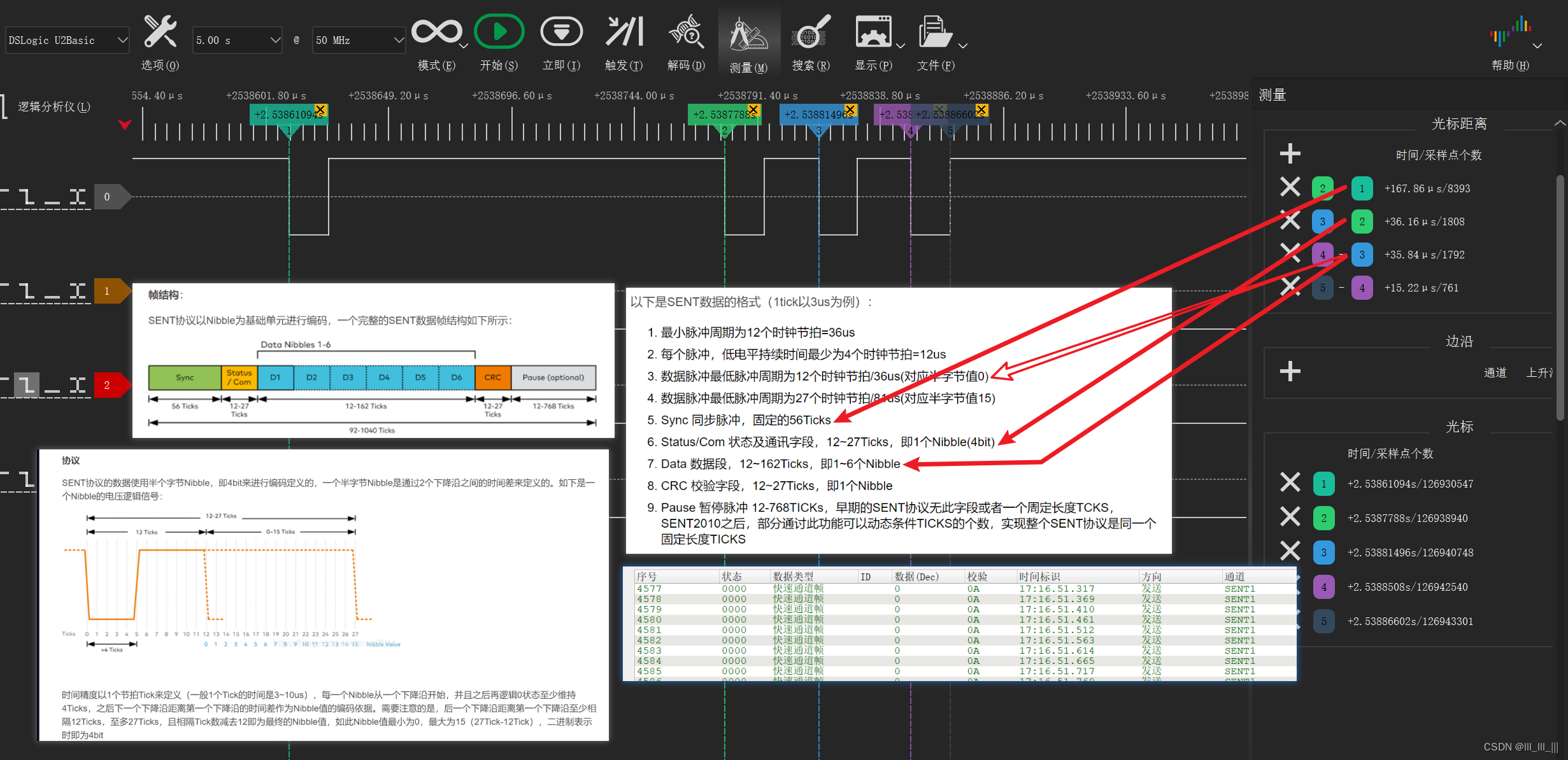

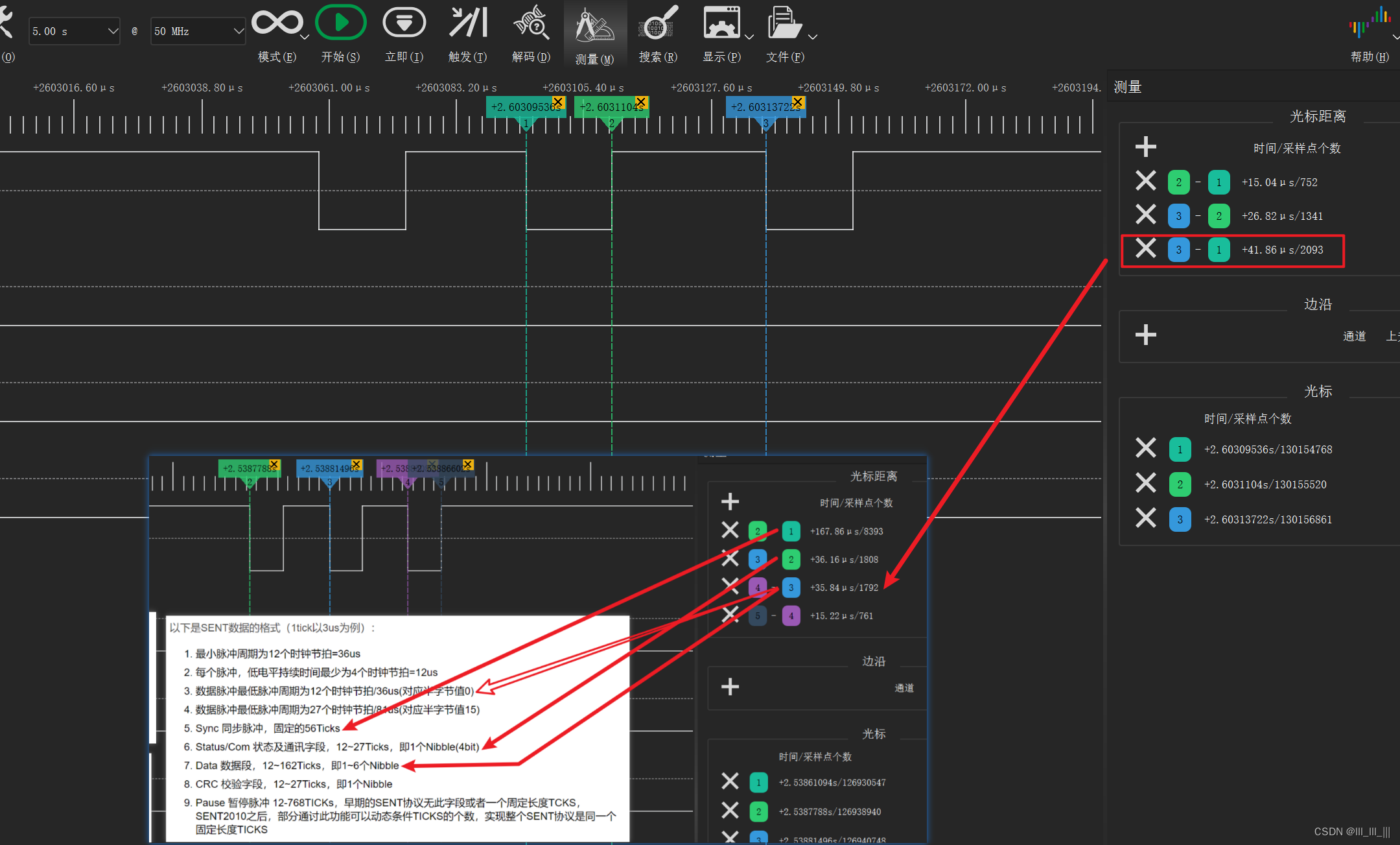

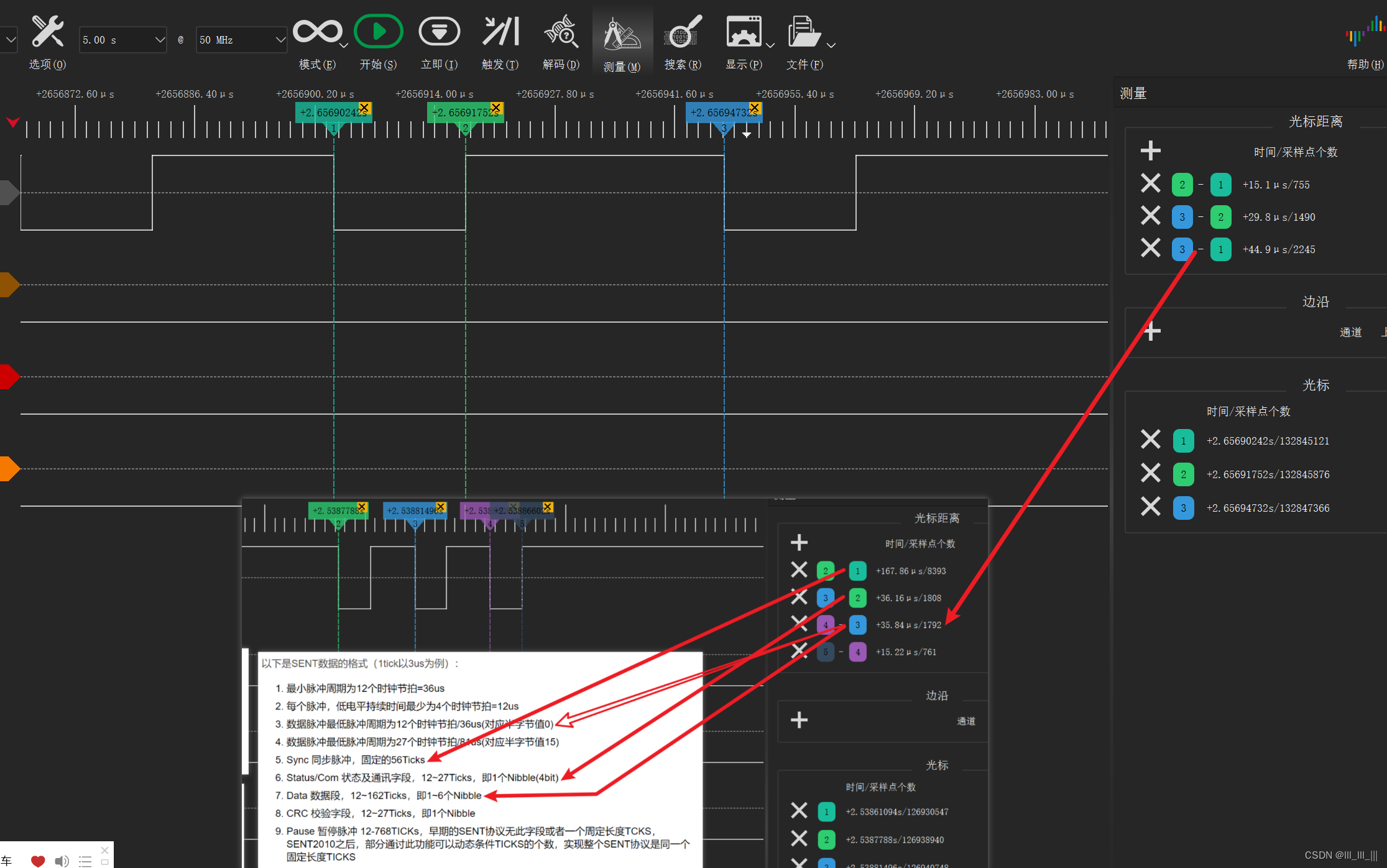

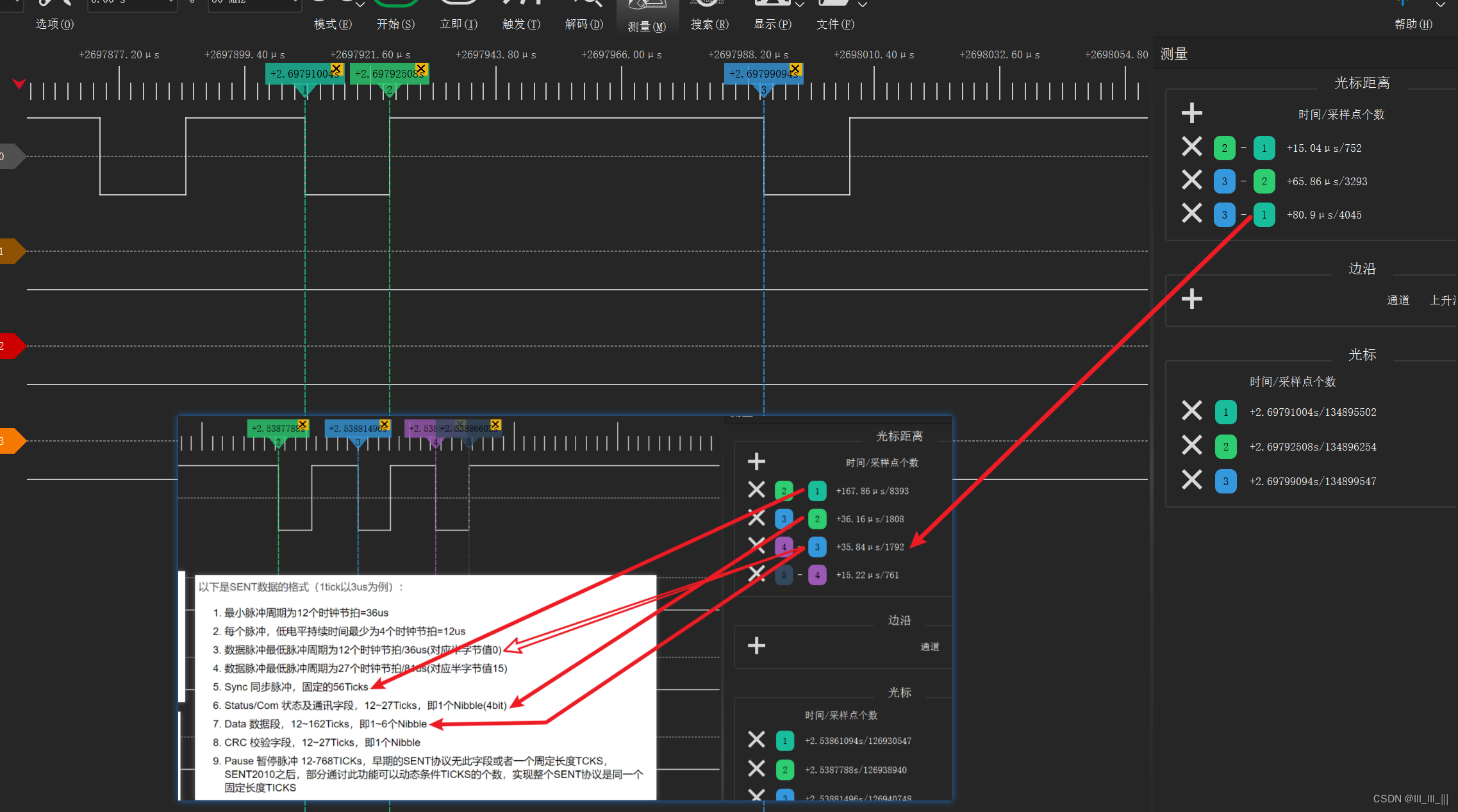

以下是SENT数据的格式(1tick以3us为例):

- 最小脉冲周期为12个时钟节拍=36us

- 每个脉冲,低电平持续时间最少为4个时钟节拍=12us

- 数据脉冲最低脉冲周期为12个时钟节拍/36us(对应半字节值0)

- 数据脉冲最低脉冲周期为27个时钟节拍/81us(对应半字节值15)

- Sync 同步脉冲,固定的56Ticks

- Status/Com 状态及通讯字段,12~27Ticks,即1个Nibble(4bit)

- Data 数据段,12~162Ticks,即1~6个Nibble

- CRC 校验字段,12~27Ticks,即1个Nibble

- Pause 暂停脉冲 12-768TICKs,早期的SENT协议无此字段或者一个周定长度TCKS,SENT2010之后,部分通讨此功能可以动态条件TICKS的个数,实现整个SENT协议是同一个固定长度TICKS

逻辑分析仪测试发送数据0符合上述数据

发送数据1如下所示

发送数据2如下所示

发送数据3如下所示

发送数据15如下所示

综上所述,主要区别在数据帧的高电平长度。

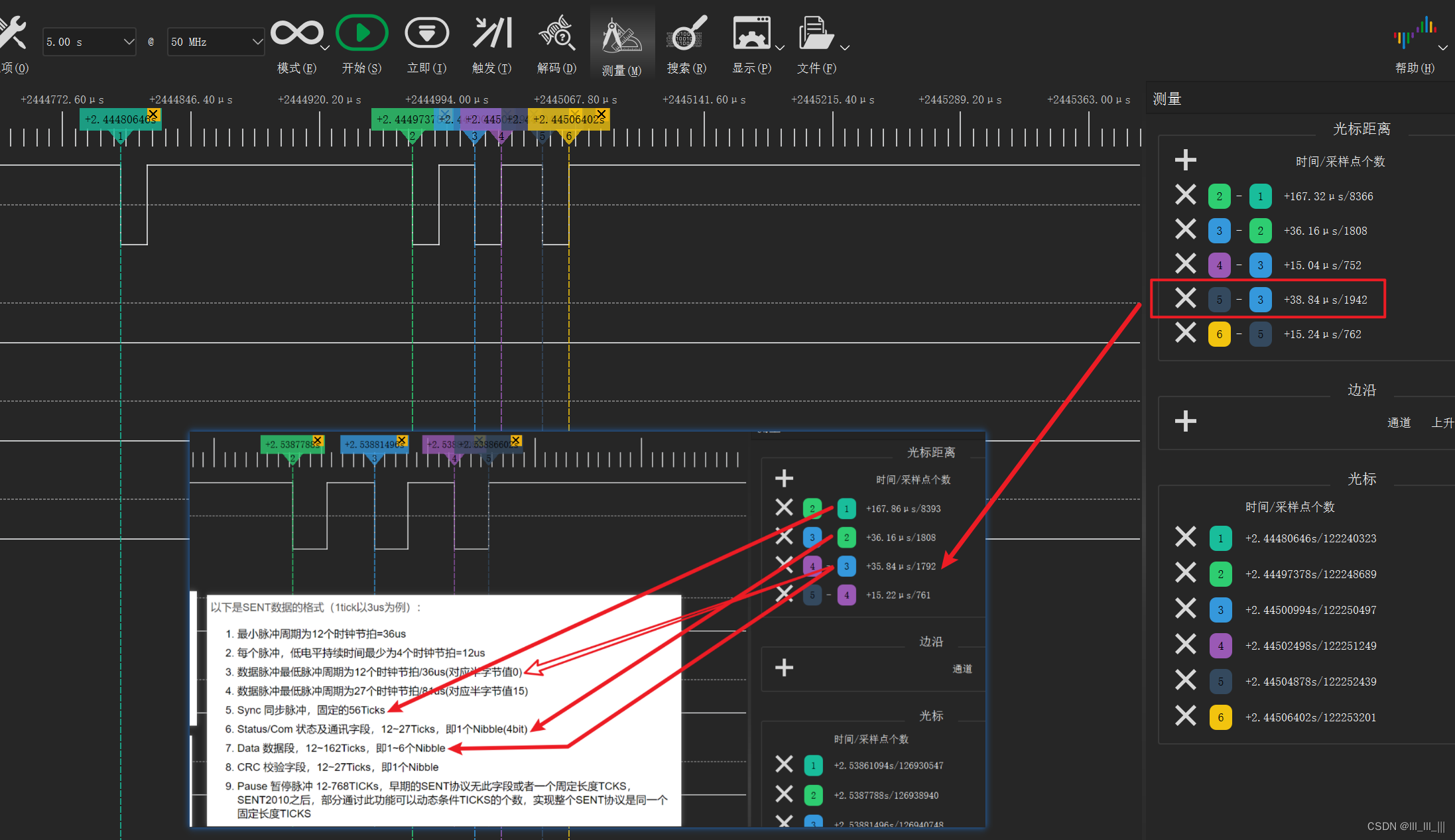

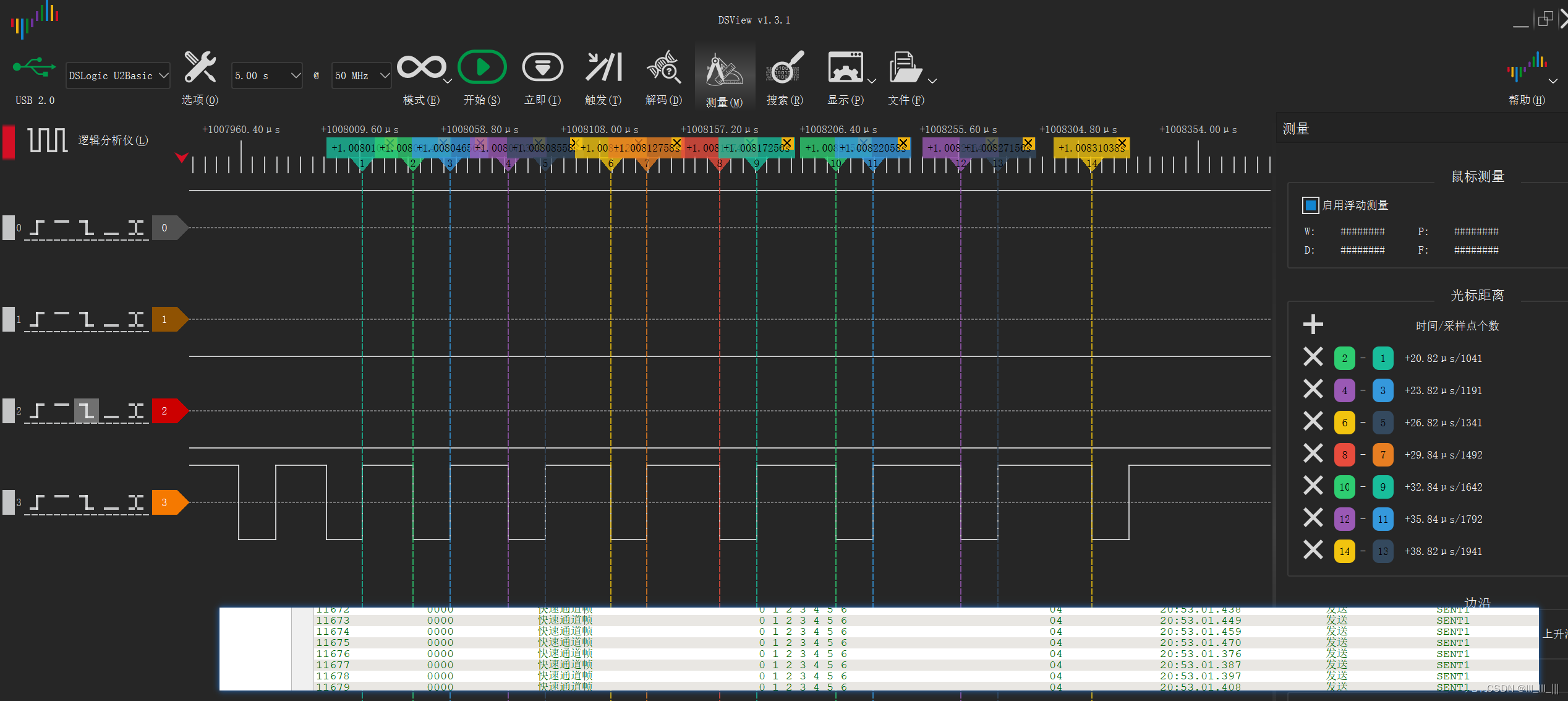

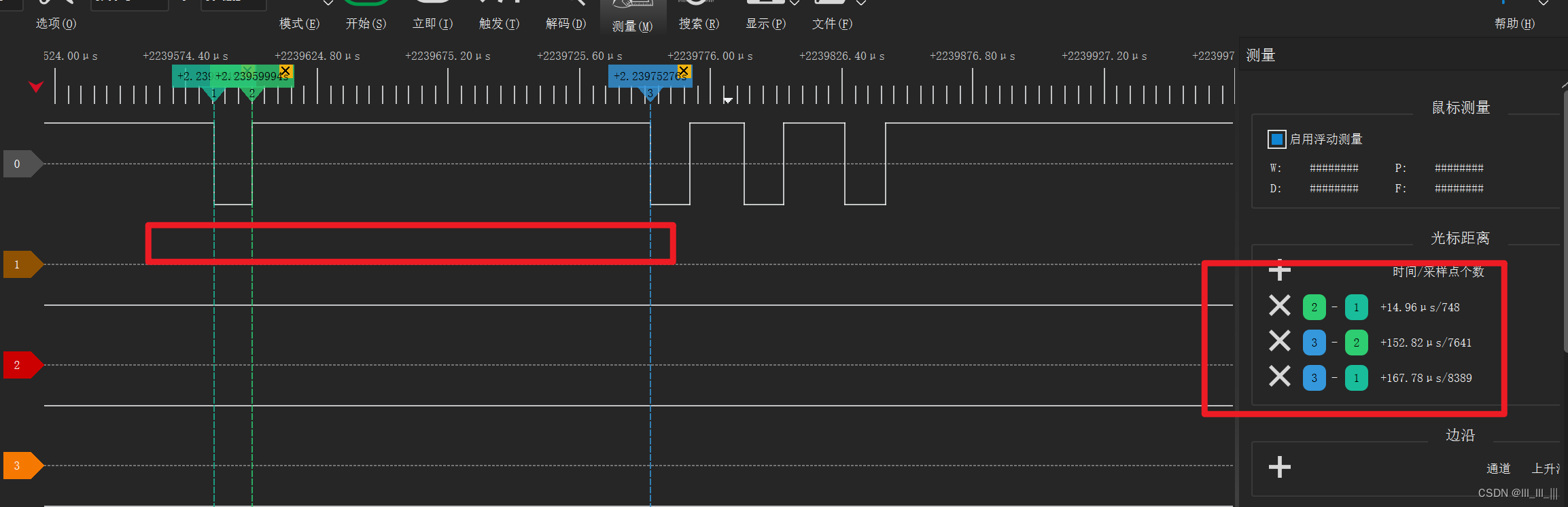

以下是发送0123456的数据格式,可以看到,数据位的长度为(21+3*N)

同步脉冲:格式固定为15uS+152uS=167uS的数据

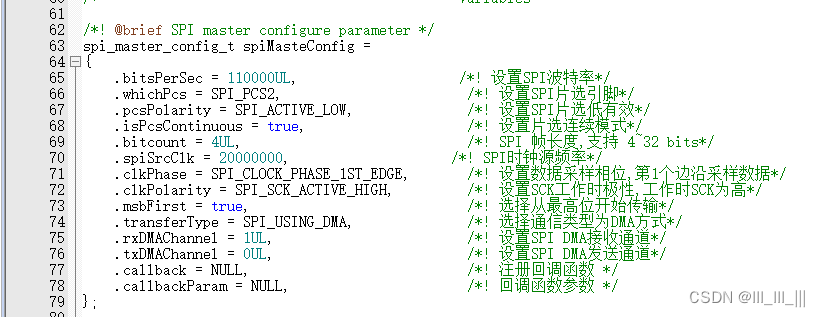

2. SPI数据结构

测试在110K波特率的情况下,SPI发送一个位的时间为1uS。

以此为基准生成Sent的数据帧

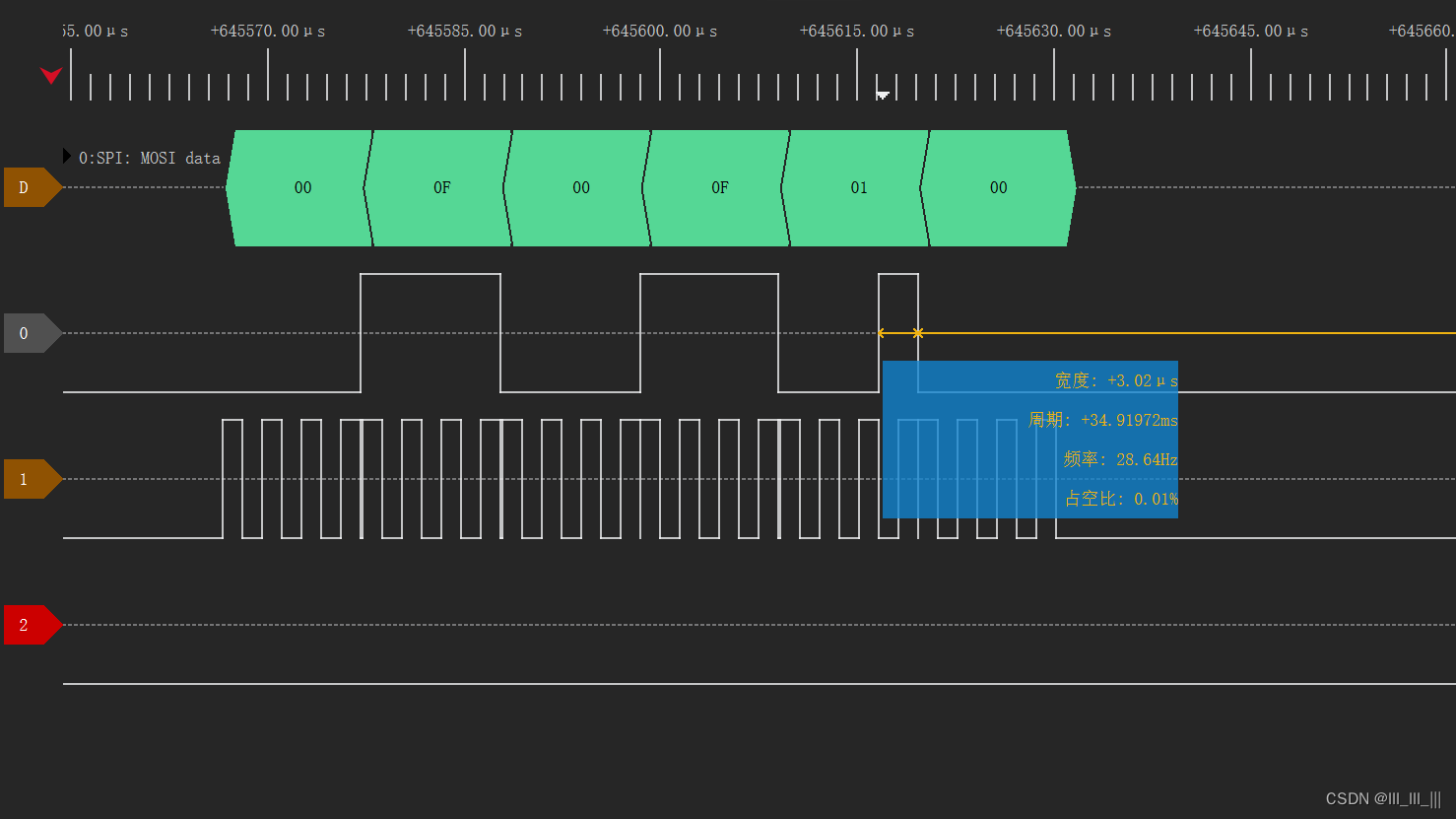

SPI生成Sent数据

可以看到上面和我们用图莫斯发出来的波形一模一样。

最后一个FF是用来拉高电平,否则第一个从高到低的数据出不来。

可以看到,其中从F0开始是数据位,到第28个数据FE是数据位,后面是每个脉冲必须的4个tick的低电平,即12us

以下是0-F的校验码

发送2个字节

while (1)

{

g_spiTxBuff1[0] = 0;

g_spiTxBuff1[1] = 0x3;

for (int i = 0; i < 18; i++)

{

g_spiTxBuff1[i + 2] = 0xff;

}

g_spiTxBuff1[20] = 0;

g_spiTxBuff1[21] = 0x1;

g_spiTxBuff1[22] = 0xff;

g_spiTxBuff1[23] = 0xff;

g_spiTxBuff1[24] = 0xf0;

g_spiTxBuff1[25] = 0;

g_spiTxBuff1[26] = 0x1f; // 00011111后5位参与数据位高电平

g_spiTxBuff1[27] = 0xff; // 参与数据位高电平

g_spiTxBuff1[28] = 0xfe; // 参与数据位高电平

g_spiTxBuff1[29] = 0x00;

g_spiTxBuff1[30] = 0x03;

g_spiTxBuff1[31] = 0xff;

g_spiTxBuff1[32] = 0xff;

g_spiTxBuff1[33] = 0xf8;

g_spiTxBuff1[34] = 0x00;

g_spiTxBuff1[35] = 0x0f;

g_spiTxBuff1[36] = 0xff;

SPI_DRV_MasterTransfer(SPI_INSTANCE, g_spiTxBuff1, g_spiRxBuff1, 37); /*! SPI通信 */

OSIF_TimeDelay(100);

}

能识别到,就是校验码还需要再优化下