QSpice-(4) 层次化电路设计

在电路规模日渐庞大的现在,单靠一个人把整个电路做完可能还有点麻烦,但也不是不可能,还是要怀揣着那种热情把电路做好,在电路规模比较大的时候我们通常会将电路放到子电路里面去,这个子电路相当于C代码里面的子程序,当我们要用这个电路的时候去调用ta就好了,在英语里面是hierarchy-层次。

Qspice和大多数EDA软件一样是支持层次化电路设计的,Simplis层次化设计 可以点击超链接查看。

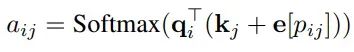

首先我们先在QSpice里面构建一个最为基本的电路图然后保存,保存图纸以后在右键选择Draw Hierarchy Entry 如图1所示。

图1:设置层次化原理图入口

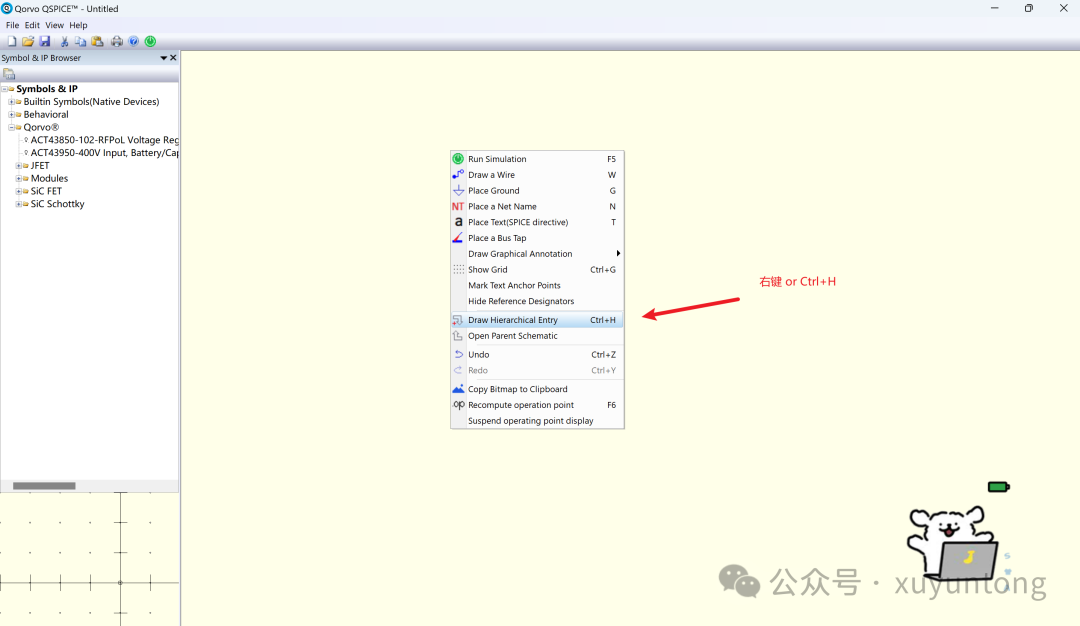

设置完层次化原理图入口以后,再在这个Entry设置Port,就是你这个小原理图需要有几个网络要被外面使用的,那你就画几个Port,画完Port后左键就可以改这个Port的名字。具体设置如下图2所示。

图2:放置Port

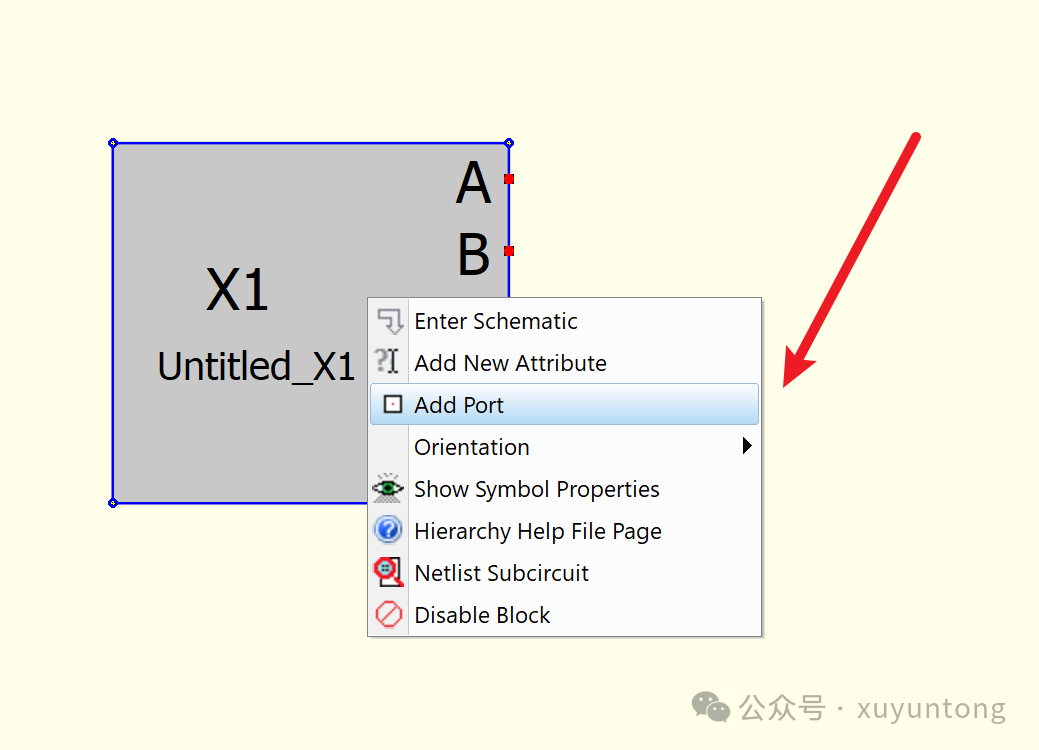

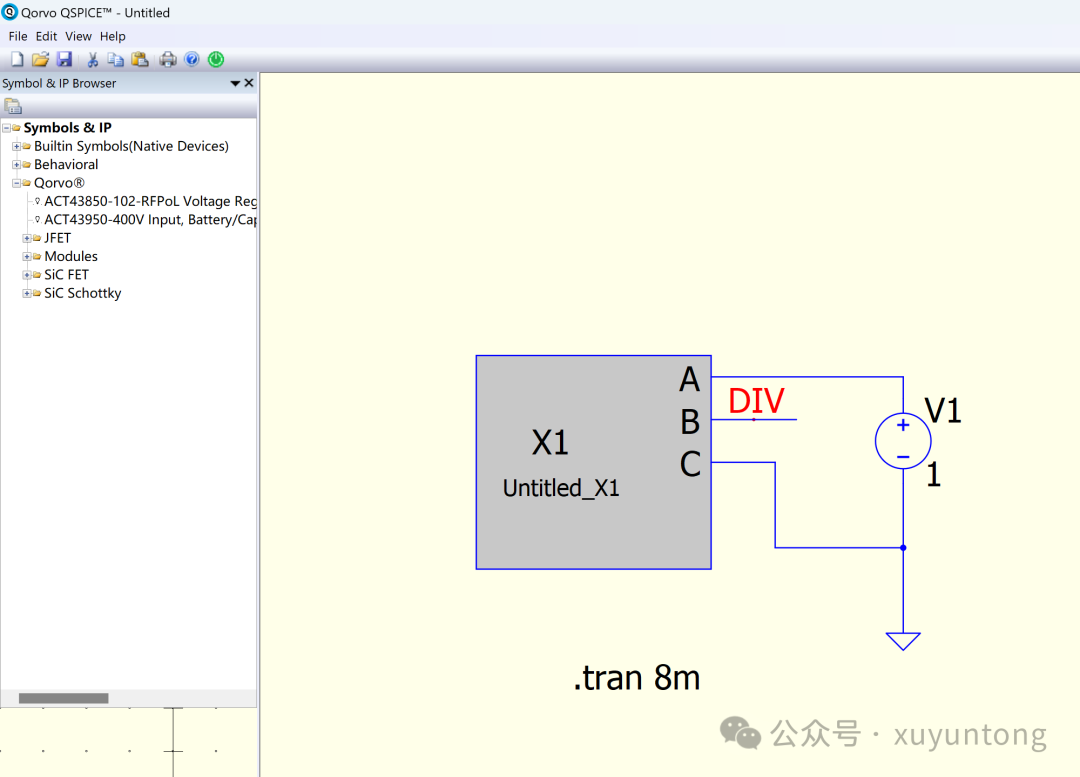

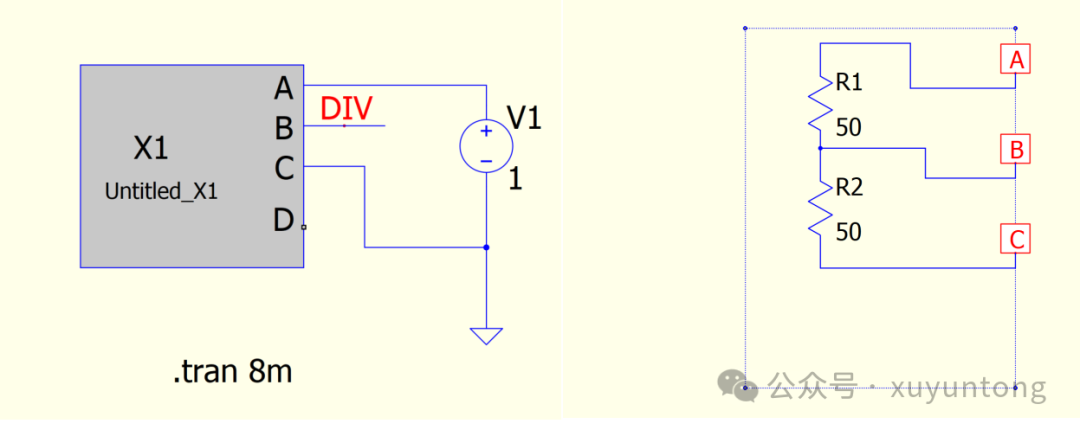

放置完Port以后双击Entry 就是这个X1就可以进子原理图绘制电路了,咱们绘制一个分压电路如下图3所示。放置完分压电路再返回主电路供给电源如图4所示。

图3:基本分压电路

图4:分压电路

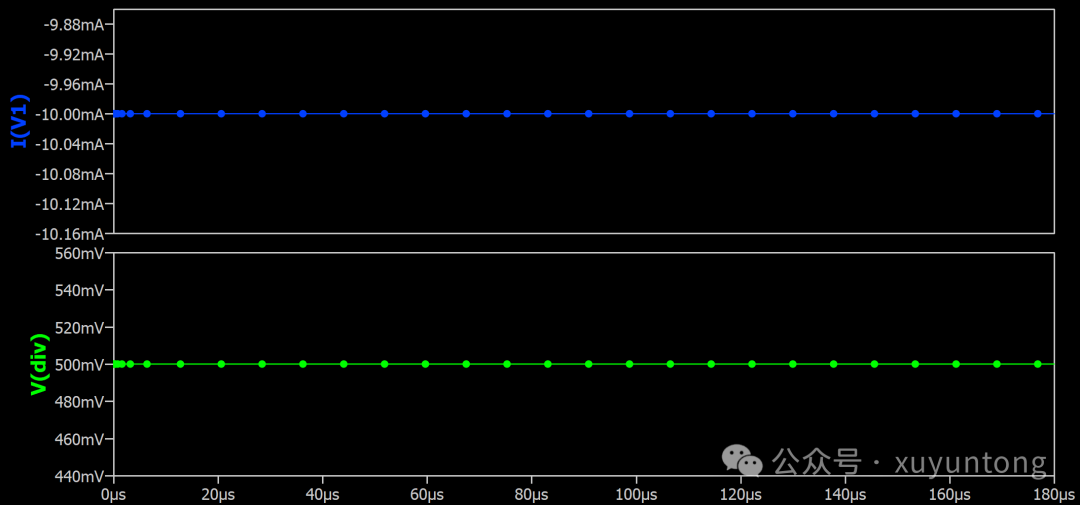

图5:仿真结果

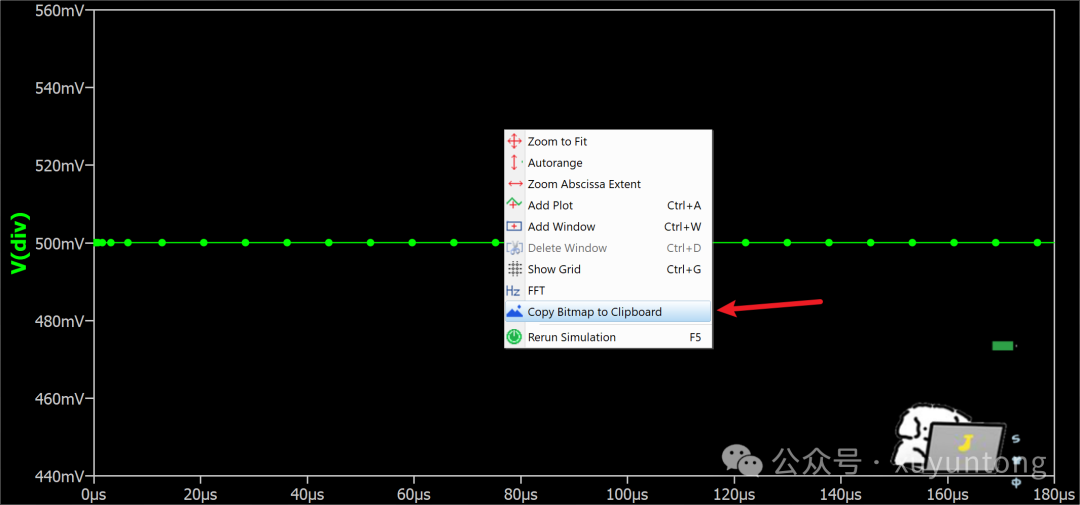

另外值得注意的是,QSpice的仿真结果无法直接CTRL + C直接复制,需要使用右键 copy bitmap to clipboard如下图6所示。

图6:复制图片到剪切板

另外还有个Bug是我在绘制过层次化原理图后,我再次添加端口就无法更新端口到子电路去了,这个需要注意!如图7所示,稍后我将反馈给作者。

图7:Qspice 小BUG

图8:QSpice 版本

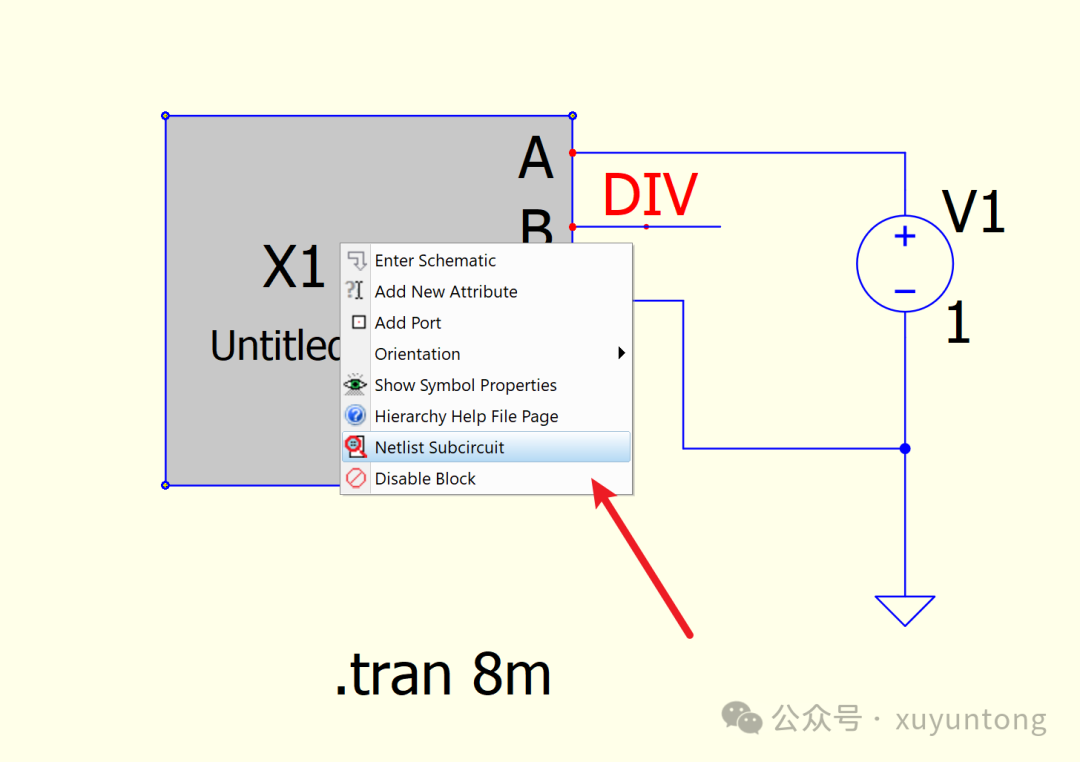

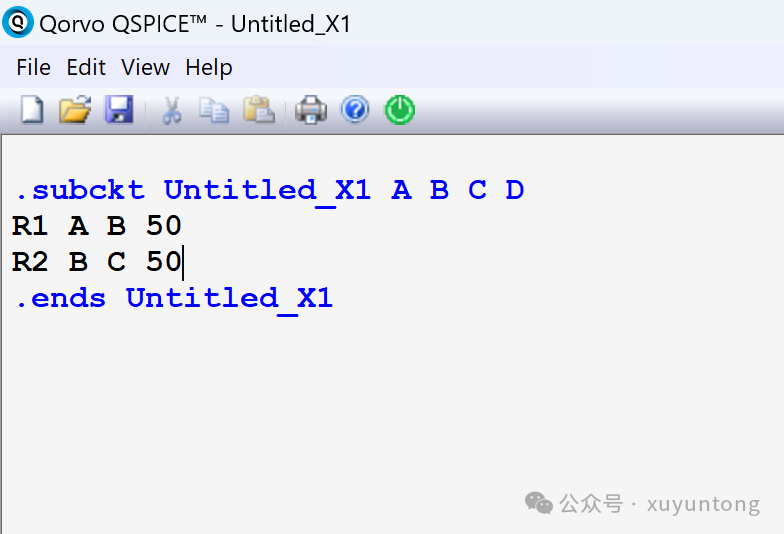

另外层次化原理图可以直接改网表来改变层次化原理图内子电路的参数,在图纸Entry右键点击netlist subcircuit可以查看子电路网表如下图9所示。

图9:Qspice 子电路网表查看

图10:子电路网表

有个小建议,建议可以直接编辑,这样可能会提高仿真的效率,到时候我也一并提交给Mike。

今天就先聊到这里了,拜拜~

无论如何,我都热爱电路,热爱电路架构的探索与设计!加油UU们!

笔者简介:许同,8.5年工作经验,电路系统架构专家,在电路领域有14年的积累,精通应用电路系统架构设计,有10项以上电路架构专利,掌握多项电路设计技能,电路Spice仿真,C语言,Python,Verilog等。

![[Spring] Spring Web MVC案例实战](https://i-blog.csdnimg.cn/direct/67dc72fef8b849c7b4cb4cfa552c0ead.png)

![[WUSTCTF2020]level4题解 入土为安的第三天](https://i-blog.csdnimg.cn/direct/f2868503c9a54caab950a19343be8179.png)