#工作记录#

原本希望使用CCI自带的验证脚本来验证修改过后的address map decoder,但是发现需要使用JasperGold或者Cadence家的IFV的工具,我们公司没有,只能搜搜资料做一下科普了解,希望以后能用到吧。这个虽然跟ARM没啥关系不过在ARM的文档中提到了姑且归到一类吧。

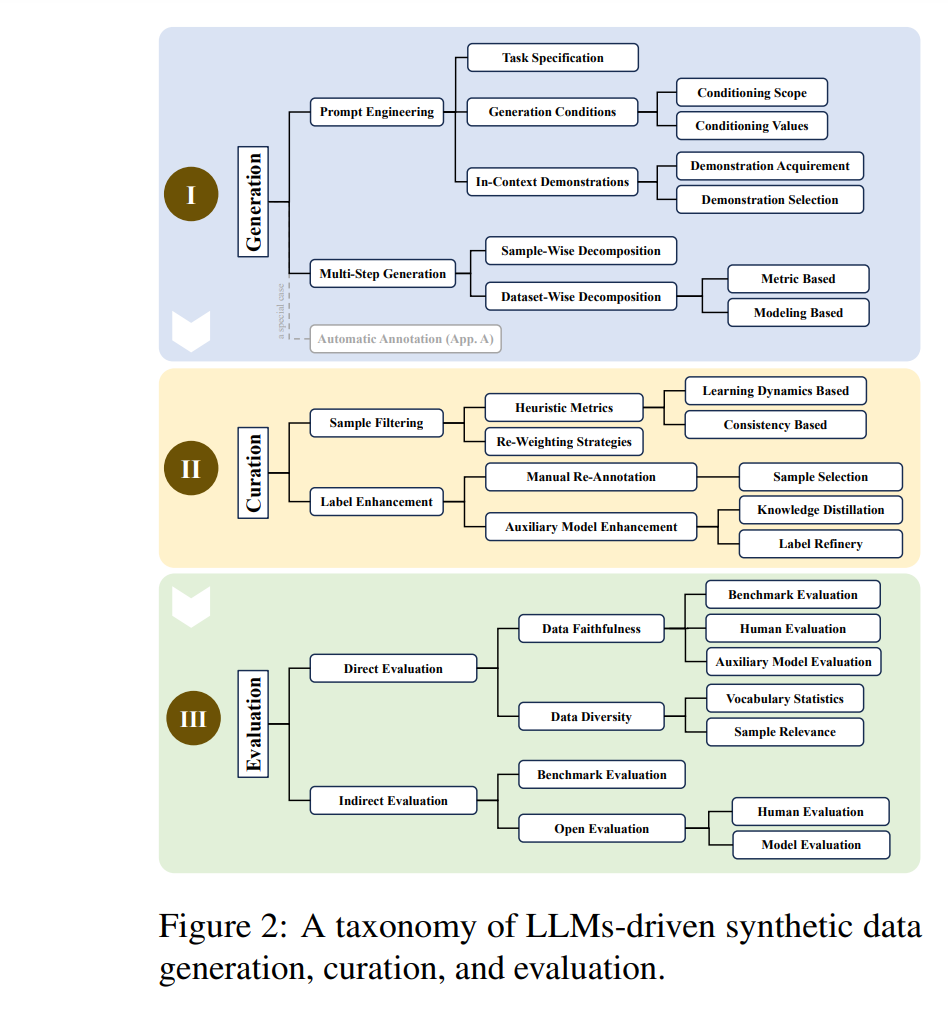

JasperGold 是 Cadence 设计系统公司开发的一种形式化验证工具平台。它主要用于在集成电路设计和验证过程中,通过数学建模和算法分析,来验证设计是否满足预定的规范和属性。形式化验证是一种补充传统的仿真验证的方法,它可以在不运行仿真的情况下,通过逻辑和数学方法来证明设计的正确性或找出潜在的错误。

JasperGold 支持多种验证应用,包括但不限于等价性检查、属性检查、安全性分析等。它使用智能验证技术和机器学习算法来提高验证的效率和准确性。例如,它可以自动选择最合适的算法并对其进行参数化配置,以提高一次性证明的成功率 。

JasperGold 的应用场景包括 RTL 设计的功能验证、综合前后的等价性检查等。它适用于规模较小、功能独立、时序较短、接口清晰的场景,并且与随机仿真验证相辅相成,分别适用于系统级和模块级的功能验证 。

Cadence 公司不断更新和增强 JasperGold 的功能,包括提供新一代的云就绪平台,集成了机器学习技术,以及对核心证明能力的改进 。JasperGold 还提供了丰富的学习资源和技术支持,帮助用户更快地上手并解决使用过程中的问题 。

此外,JasperGold 还具备形式化覆盖率分析功能,支持工程师在平台内完成 IP 级别的签核,并且与 Cadence 的其他验证工具如 Xcelium 仿真器和 Palladium 硬件仿真加速器等集成,提供全面的验证解决方案 。

https://www.cadence.com/zh_CN/home/tools/system-design-and-verification/formal-and-static-verification/jasper-gold-verification-platform.html![]() https://www.cadence.com/zh_CN/home/tools/system-design-and-verification/formal-and-static-verification/jasper-gold-verification-platform.htmlCadence推出全新智能JasperGold形式化验证平台楷登电子(美国Cadence公司,NASDAQ:CDNS)今日发布了第三代Cadence® JasperGold® 形式化验证平台,采用机器学习技术,提升了核心证明能力,旨在提高验证吞吐量,解决当今先进SoC设计容量和复杂性上的挑战。

https://www.cadence.com/zh_CN/home/tools/system-design-and-verification/formal-and-static-verification/jasper-gold-verification-platform.htmlCadence推出全新智能JasperGold形式化验证平台楷登电子(美国Cadence公司,NASDAQ:CDNS)今日发布了第三代Cadence® JasperGold® 形式化验证平台,采用机器学习技术,提升了核心证明能力,旨在提高验证吞吐量,解决当今先进SoC设计容量和复杂性上的挑战。![]() https://cn.design-reuse.com/news/46082/cadence-smart-jaspergold-formal-verification-platform.html

https://cn.design-reuse.com/news/46082/cadence-smart-jaspergold-formal-verification-platform.html

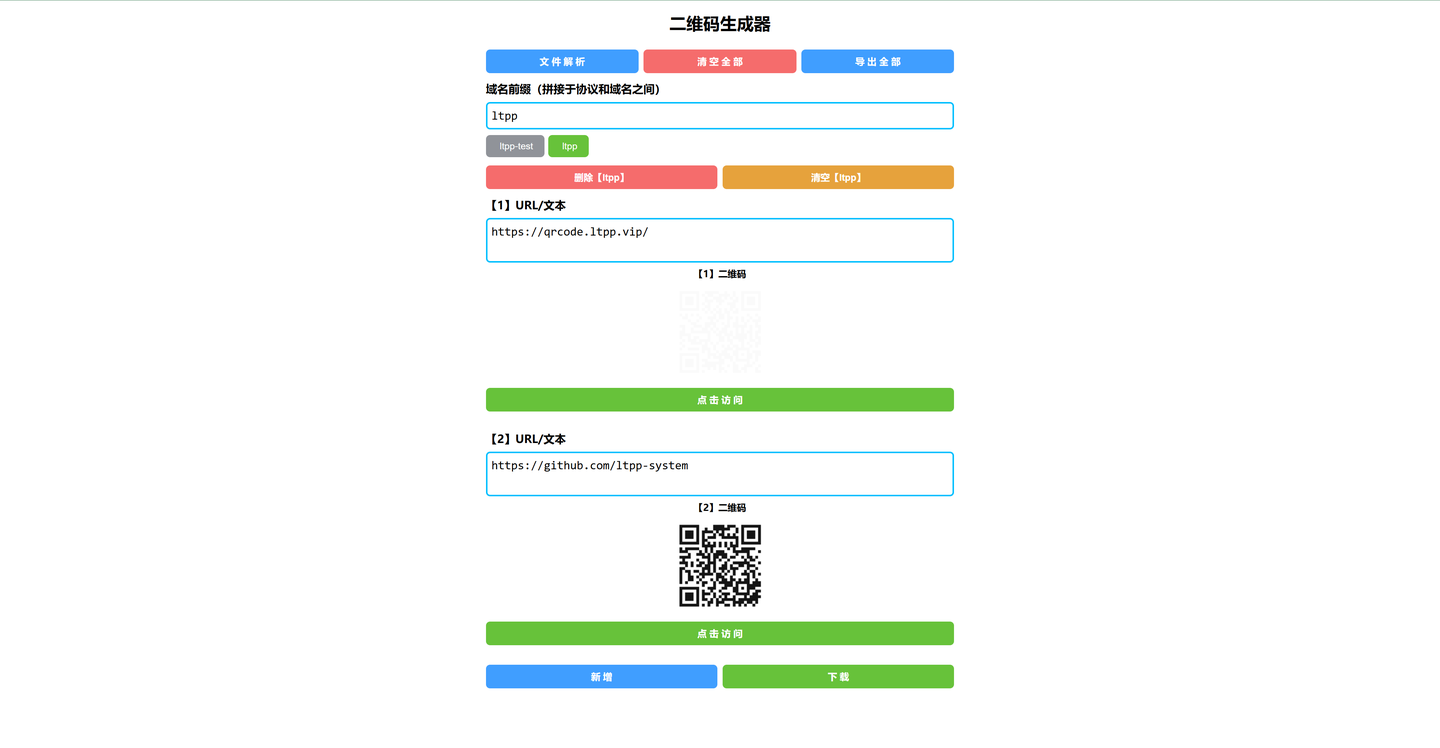

Cadence的IFV,即Incisive Formal Verifier,是一种形式化验证工具,它通过在测试台架可用之前检测错误,使得设计周期的验证阶段可以非常早期地开始,并缩短了设计收敛的时间。使用Incisive Formal Verifier,你可以比使用传统的基于仿真的技术更早地开始RTL块验证。它的形式化、基于断言的方法和穷尽分析能力通过确定错误源头和检测其他方法经常遗漏的边缘情况错误,确保了验证的质量。该工具通过支持行业标准语言,容易集成到现有的设计和基于断言的验证流程中。它还优化了数据和覆盖度量,以进一步加速基于度量的系统级芯片(SoC)和硅设计流程 。

形式化验证的应用,如SoC连通性检查和基于断言的验证IP,提供了数学上穷尽的自动化验证过程,这可能打破仅使用仿真的方法。Incisive Formal Verifier使用与Incisive仿真、加速和仿真技术相同的断言,用于SoC和硅设计。该工具支持所有行业标准的断言格式,包括SystemVerilog Assertions (SVA)、Property Specification Language (PSL)、Open Verification Library (OVL)和Incisive Assertion Library 。

此外,形式化验证在SoC连通性验证方面的应用也被详细描述,它提供了一种可扩展的解决方案,可以在过程中更早地发现更多的连通性问题,并且使用的验证资源更少。形式化验证本质上是穷尽的,因此解决了测试的质量。在案例研究中,使用了Cadence的Incisive® Formal Verifier (IFV)来实现连通性验证流程 。形式化验证方法在该案例研究中的应用显示,验证更加穷尽,能够发现实际的连通性错误,这些错误在正常操作中可能并不明显,但在特定情况下可能会导致问题 。

Static Formal Verification for System Level Verification

https://www.cadence.com/en_US/home/tools/system-design-and-verification/formal-and-static-verification.html![]() https://www.cadence.com/en_US/home/tools/system-design-and-verification/formal-and-static-verification.html

https://www.cadence.com/en_US/home/tools/system-design-and-verification/formal-and-static-verification.html