一、实验步骤

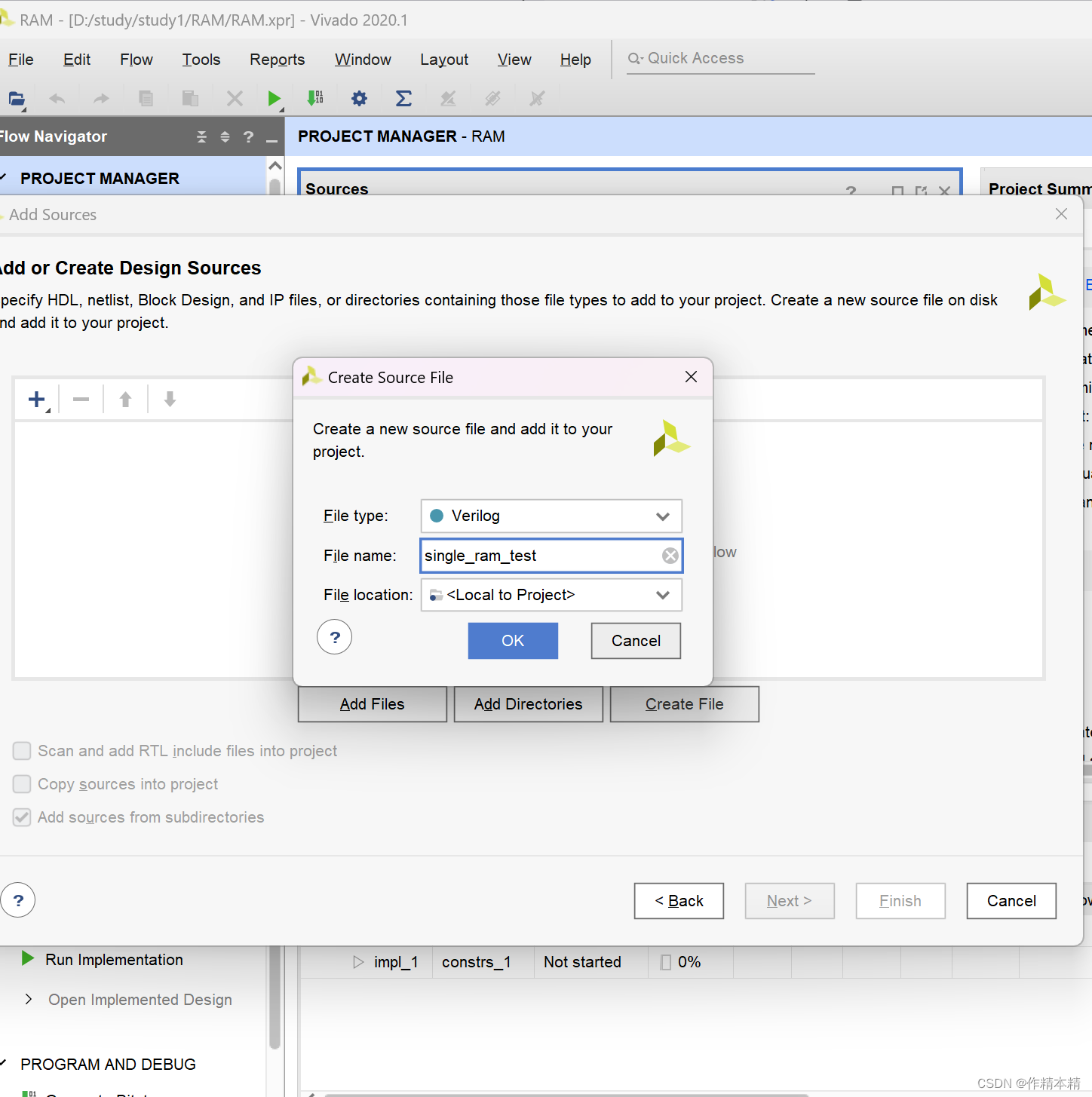

(1)先创建一个工程

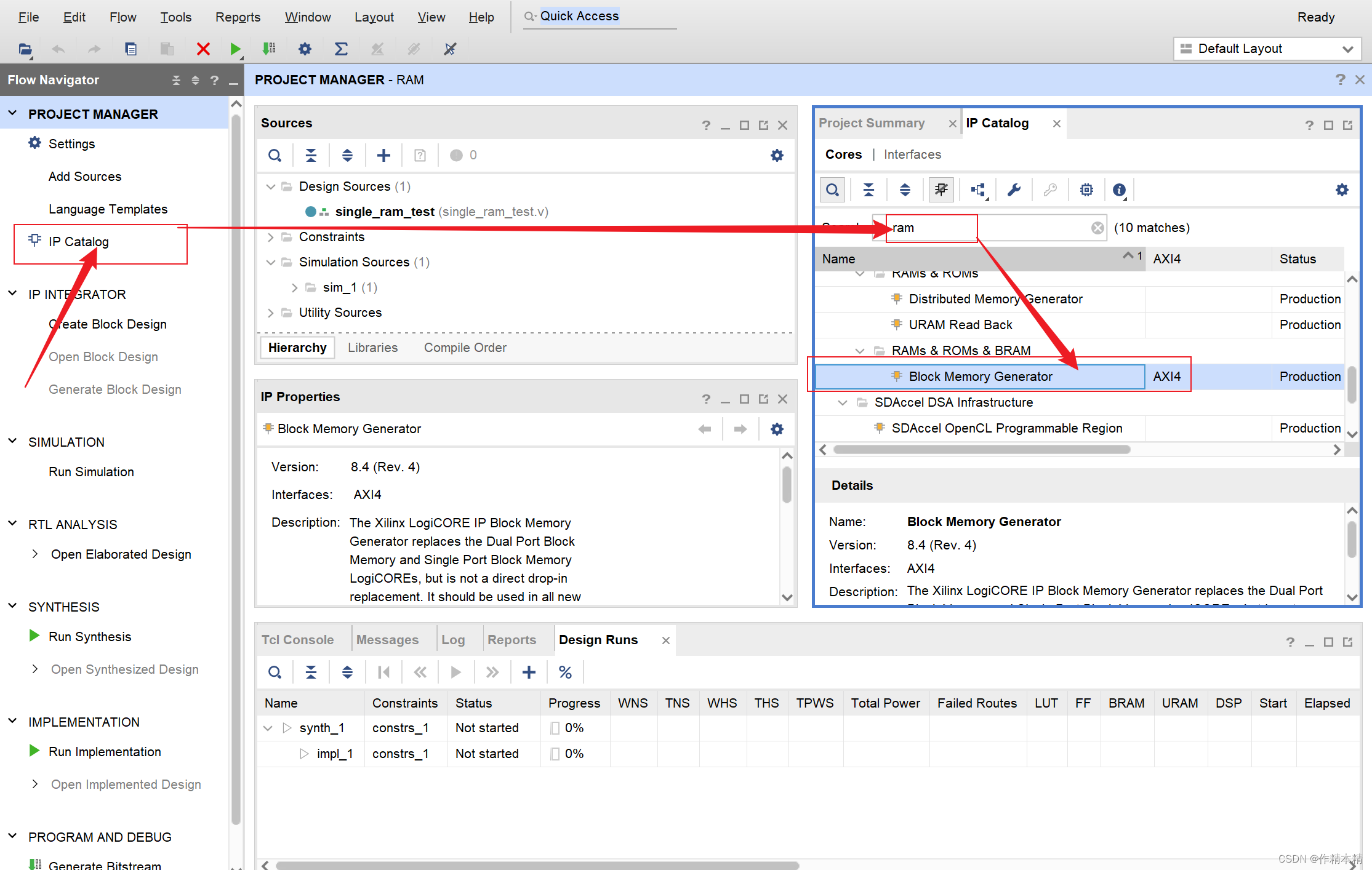

(2)调用IP资源找到RAMs&ROMs&BRAMs,选择其中的块资源

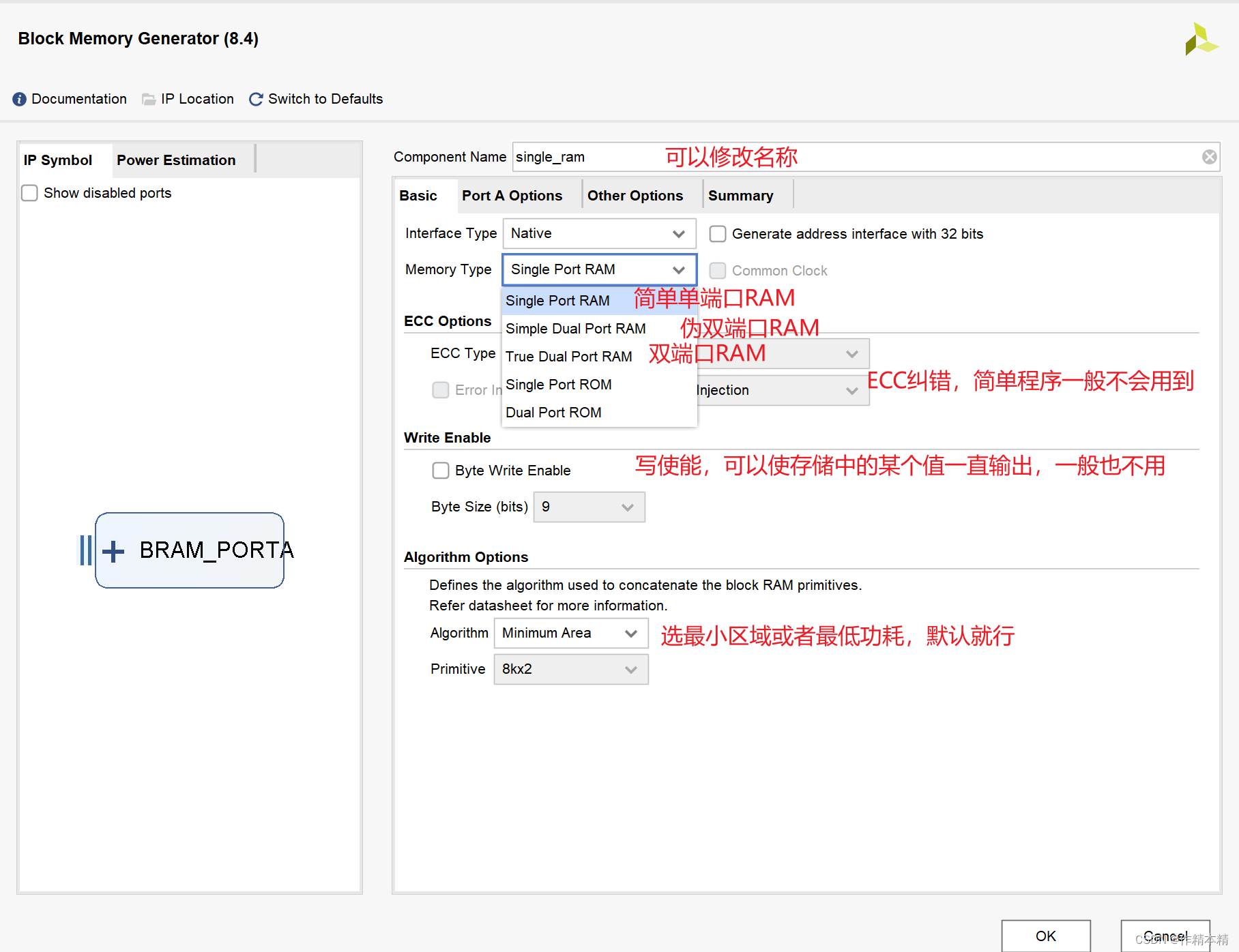

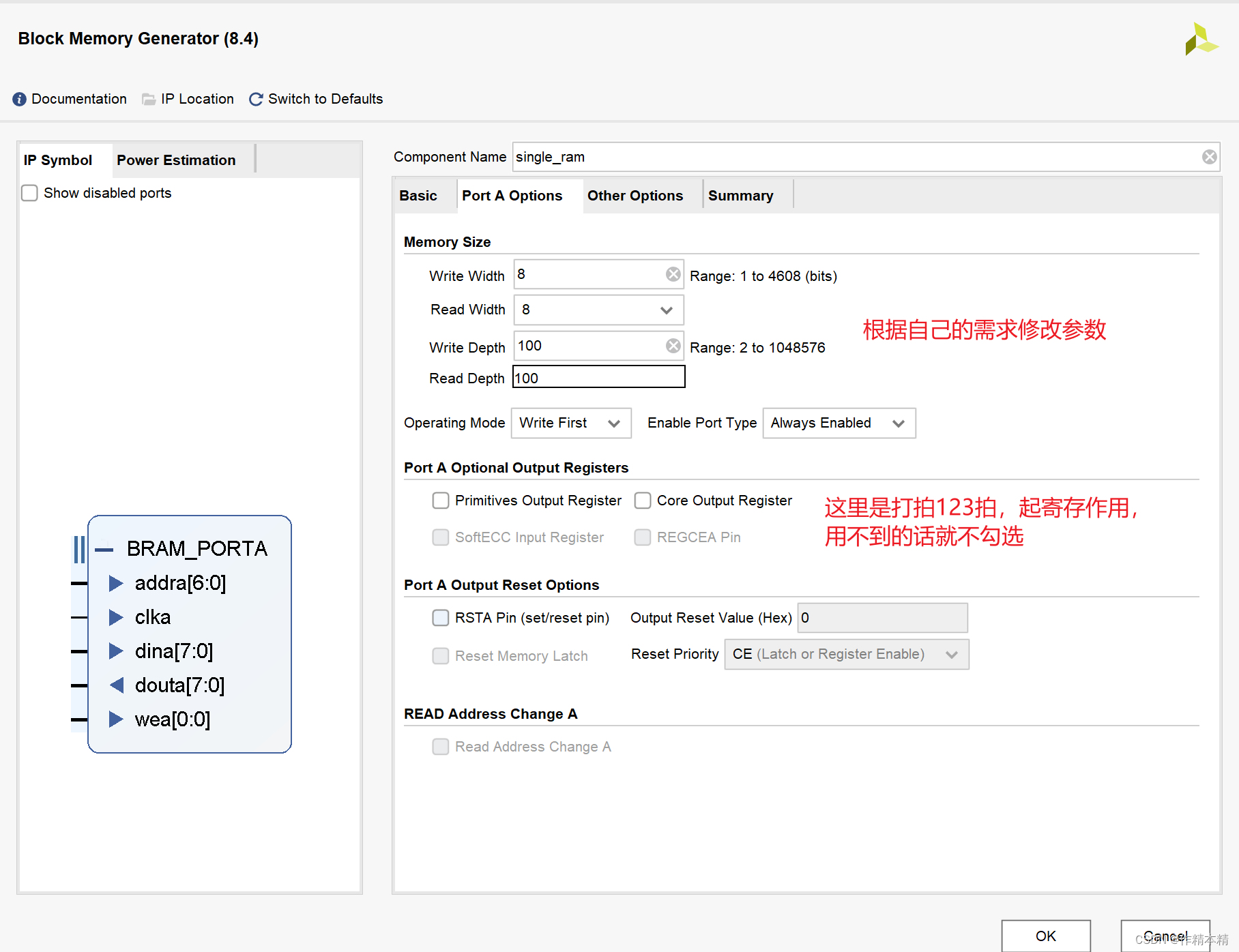

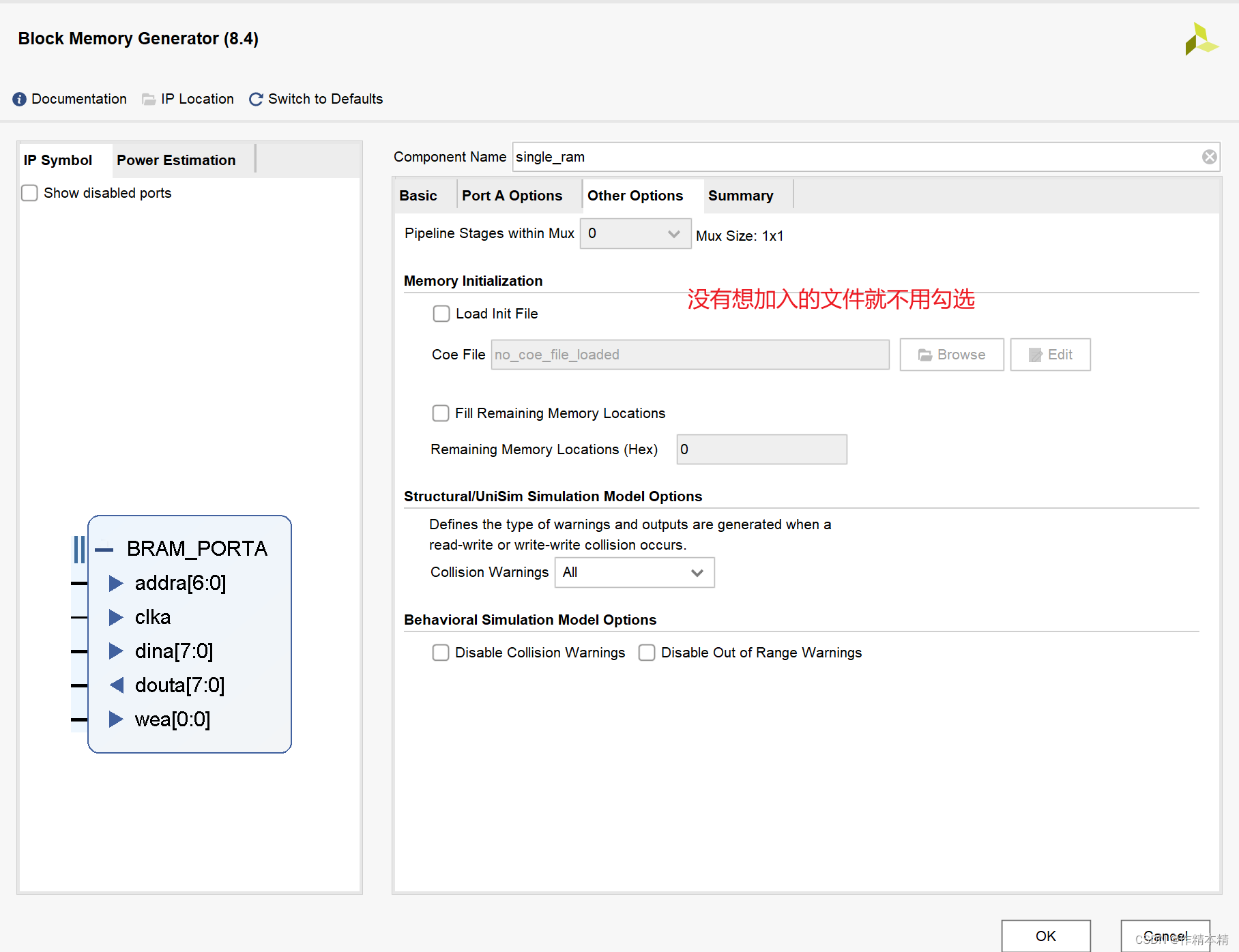

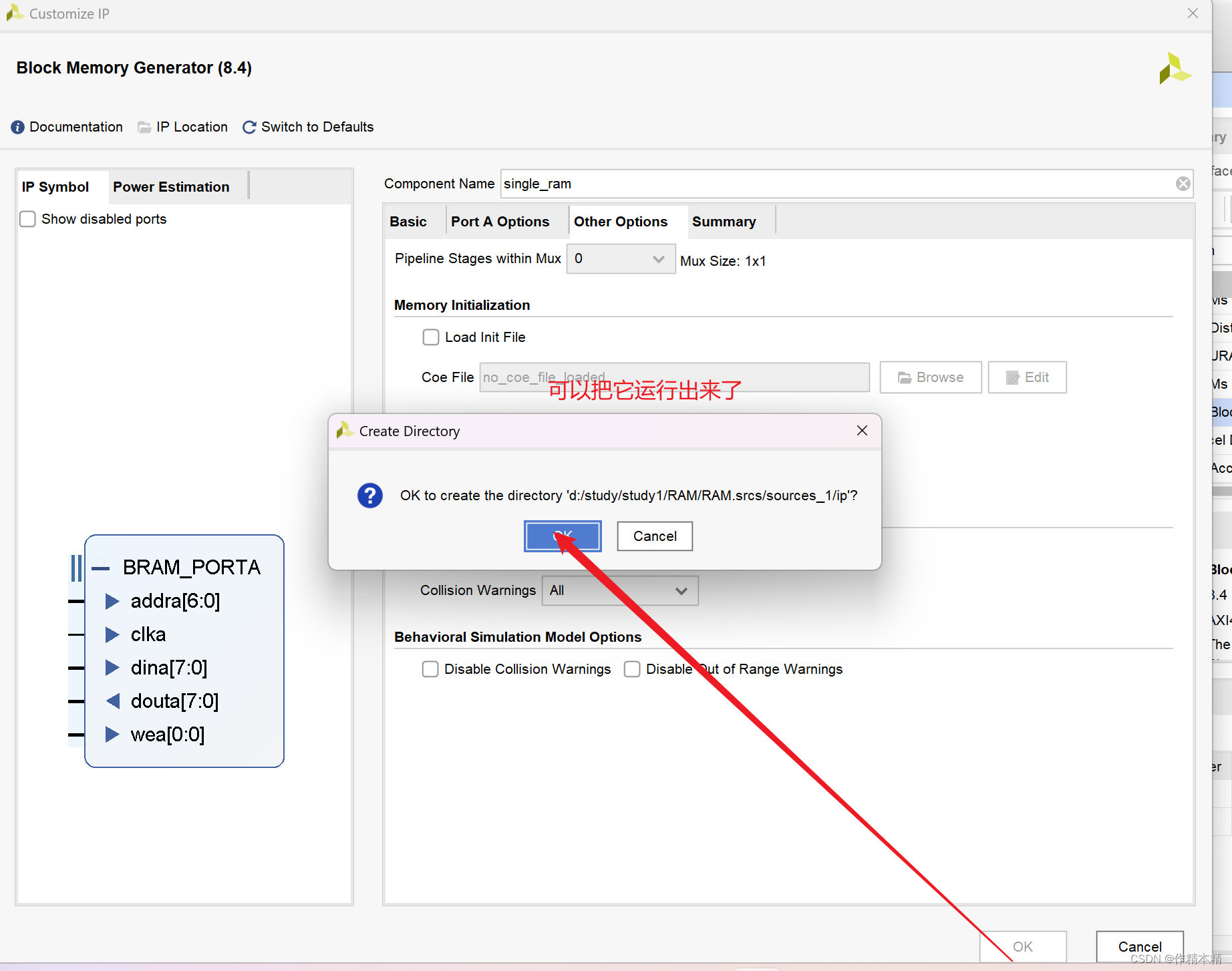

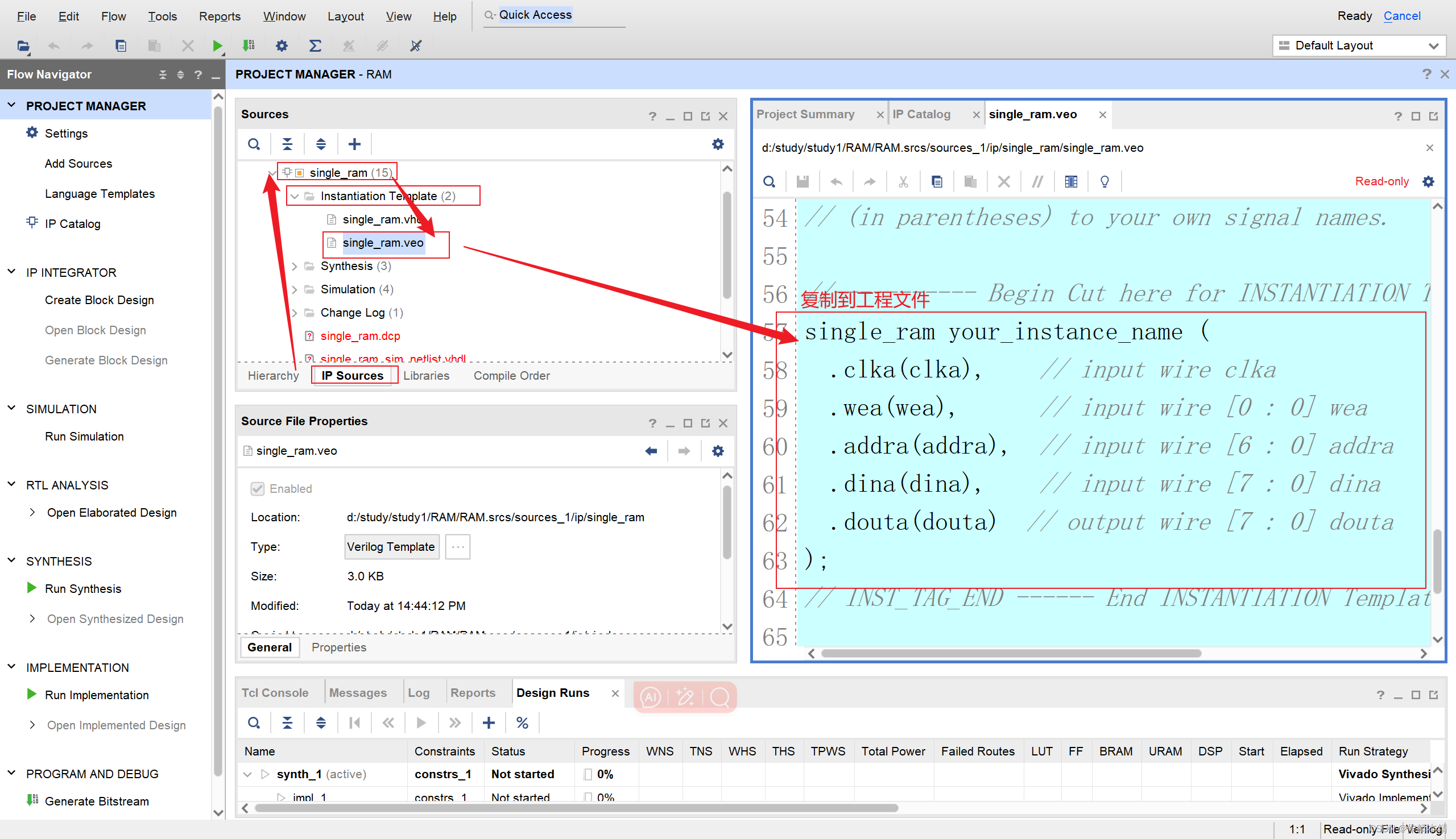

(3)修改配置参数

`timescale 1ns / 1ps

//写入0-99的数据,读出偶数

module single_ram_test(

input sys_clk ,

input rst_n ,

output reg[7:0] ram_out

);

//----------- Begin Cut here for INSTANTIATION Template ---// INST_TAG

wire wea ; //写使能

assign wea = 1 ;

reg[6:0] addra ;

reg[7:0] dina ;

wire[7:0] douta ;

always@(posedge sys_clk)

if(!rst_n)

addra <= 0 ;

else if (addra == 99)

addra <= 0 ;

else

addra <= addra +1 ;

always@(posedge sys_clk )

if(!rst_n)

dina <= 0 ;

else if ( dina == 99 )

dina <= 0 ;

else

dina <= dina +1 ;

always@(posedge sys_clk )

if(!rst_n)

ram_out <= 0 ;

else if ( douta%2 == 0 ) //读出偶数

ram_out <= douta ;

else

ram_out <= 0 ;

single_ram your_instance_name (

.clka(sys_clk), // input wire clka

.wea(wea), // input wire [0 : 0] wea

.addra(addra), // input wire [6 : 0] addra

.dina(dina), // input wire [7 : 0] dina

.douta(douta) // output wire [7 : 0] douta

);

// INST_TAG_END ------ End INSTANTIATION Template ---------

endmodule

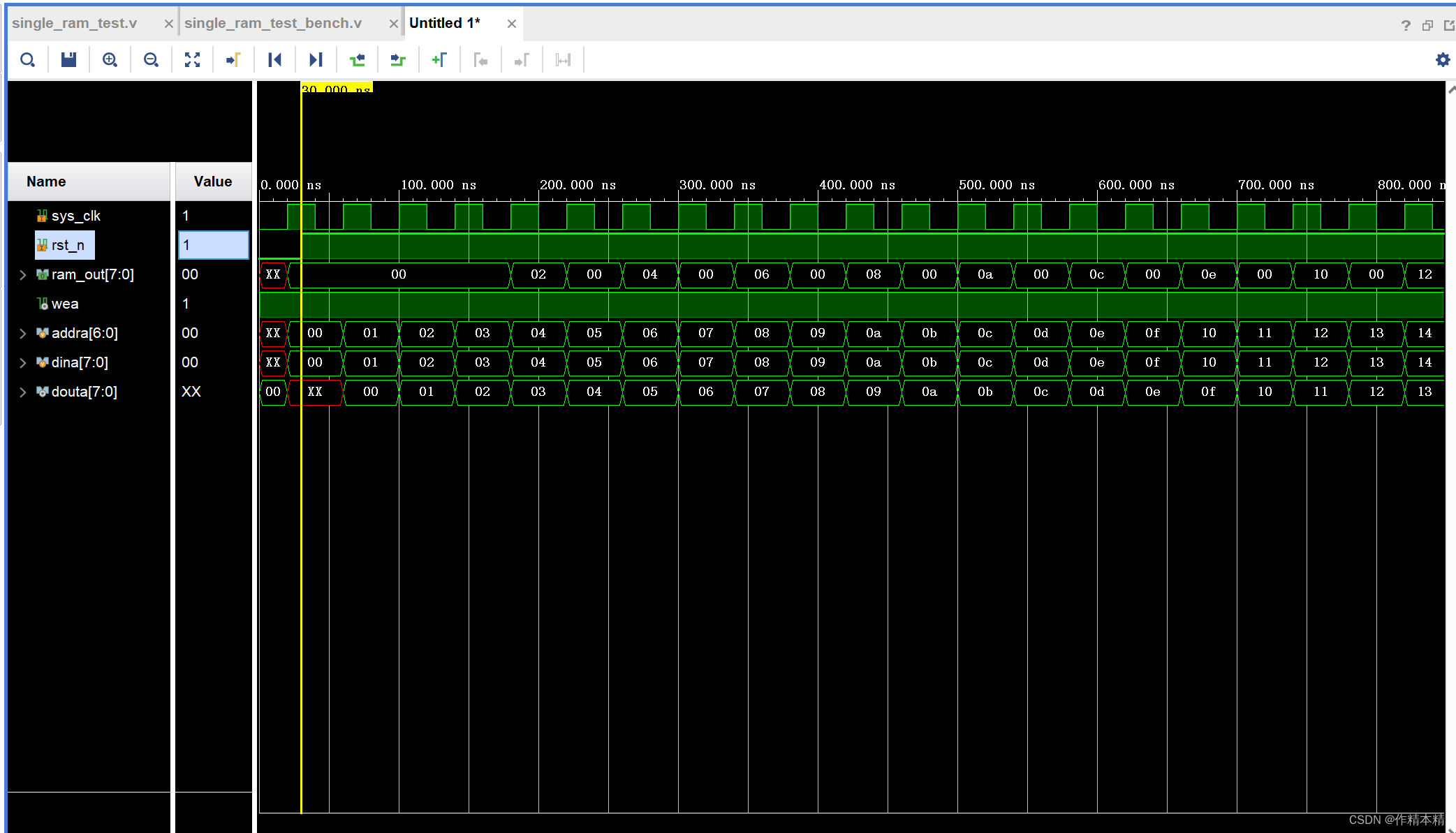

仿真结果:

`timescale 1ns / 1ps

module single_ram_test_bench( );

reg sys_clk ;

reg rst_n ;

wire[7:0] ram_out ;

initial

begin

sys_clk = 0 ;

rst_n = 0 ;

#30 rst_n = 1 ;

end

always #20 sys_clk = ~sys_clk ;

single_ram_test single_ram_test_u1(

. sys_clk (sys_clk) ,

. rst_n (rst_n ) ,

. ram_out (ram_out)

);

endmodule