第2章 寄存器

一个 CPU 由运算器,控制器,寄存器等器件构成,这些器件靠内部总线进行相连。简单的说 CPU 中:

- 运算器进行信息处理

- 寄存器进行信息存储

- 控制器控制各种器件进行工作

- 内部总线连接各个器件,在他们之间进行各种数据的传送

寄存器是 CPU 中程序员可以用指令读写的部件,程序员可以通过改变各种寄存器的内容实现对 CPU 的控制

8086CPU 由14个寄存器:AX,BX,CX,DX,SI,DI,SP,BP,IP,CS,SS,DS,ES,PSW

- 外部总线:相对于 CPU 内部而言是外部总线,实现 CPU 和主板上其他器件的联系。

- 内部总线:实现 CPU 内部各个器件之间的联系。

2.1 同用寄存器

8086CPU 的所有寄存器都是16位,可以存放两个字节。AX,BX,CX,DX 这4个通用寄存器,每一个寄存器可以分为两个可独立使用的8位寄存器来使用。

以 AX 为例:寄存器的逻辑结构如图 2.1 所示:

- AX 可以分为 AH 和 AL

- BX 可以分为 BH 和 BL

- CX 可以分为 CH 和 CL

- DX 可以分为 DH 和 DL

以 AX 为例:8086CPU 的16位寄存器分为两个8位寄存器的情况如图 2.3 所示:

AX 的低8位(0位~7位)构成了 AL 寄存器,高8位(8位~15位)构成了 AH 寄存器。

图2.4 展示16位寄存器及其所分成的两个8位寄存器的数据存储情况:

2.2 物理地址

CPU 访问内存单元,要给出内存单元的地址。每一个内存单元在这个空间中都有一个唯一的地址,我们将这个唯一的地址称之为

物理地址

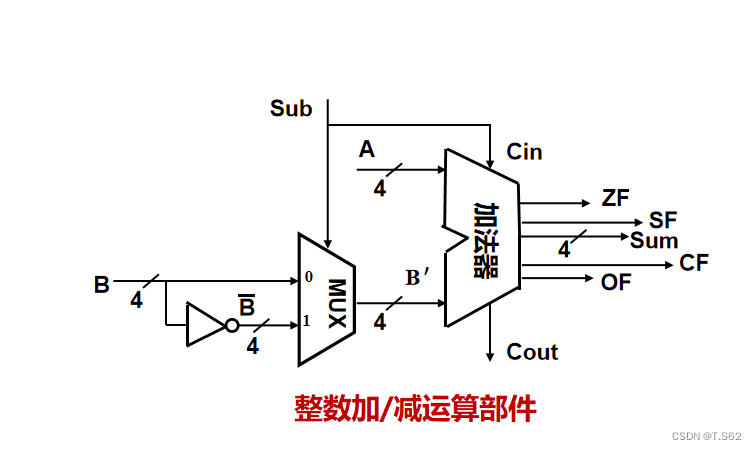

2.3 8086 CPU 给出物理地址的方法

- CPU 中的相关部件提供两个16位地址,一个称之为段地址,一个称之为偏移地址

- 段地址和偏移地址通过内部总线送入一个称之为地址加法器的部件

- 地址加法器将两个16位地址合成一个20位的物理地址

- 地址加法器通过内部总线将20位物理地址送入到输入和输出控制电路

- 输入和输出控制电路将20 位物理地址送上地址总线

- 20位物理地址被地址总线传送到存储器

地址加法器采用:物理地址 = 段地址*16+偏移地址 合成物理地址

例如:8086CPU 要访问地址为 123C8H 的内存单元,地址加法器的工作过程如图2.7所示:

2.4 段的概念

在编程时可以根据需要,将若干地址连续的内存单元看作一个段。偏移地址位16位,16位地址的最大寻址能力位 64KB,所以要给段的长度最大位 64KB

2.5 段寄存器

段寄存器:CS、DS、SS、ES

CS:代码段寄存器

IP:指令指针寄存器

2.6 CS 和 IP

- CS:代码段寄存器;

- IP:指令指针寄存器。

假设 CS 中的内容为 M,IP 中内容为 N,8086CPU 将从内存 M✖16+N 单元开始,读取一条指令并执行

在 8086PC 机中,任意时刻,CPU 将 CS: IP 指向内存单元中的内容看作指令

2.7 总结

- CS 存放指令的段地址,IP 存放指令的偏移地址,任意时刻,CPU 将 CS: IP 指向内容当作指令的执行

- CPU 工作的流程:

- 从 CS: IP 指向内存单元读取指令,读取的指令进入指令的缓冲器

- IP = IP + 所读取指令的长度,从而指向下一条指令

- 执行指令。

2.8 Debug

-

R 命令查看、改变 CPU 寄存器的内容

-

D 命令查看内存中的内容

-

E 命令改写内存中的内容

-

U 命令将内存中的机器指令翻译成汇编指令

-

T 命令执行一条机器指令

g -

R 命令查看、改变 CPU 寄存器的内容

-

D 命令查看内存中的内容

-

E 命令改写内存中的内容

-

U 命令将内存中的机器指令翻译成汇编指令

-

T 命令执行一条机器指令

-

A 命令已汇编指令的格式在内存中写入一条机器指令