仿真

链接:https://pan.baidu.com/s/1N1nR39Gws59laVZY2slzBw

提取码:01ct

一、实验目的

1、通过实验,能熟悉QUARTUS开发环境,能够掌握VHDL设计电路,掌握使用相关仿真工具进行功能和时序仿真的方法;

2、通过实验,加深对计数器等时序逻辑电路的理解,并能使用VHDL完成计数器的设计,并能在QUARTUS中完成相关的仿真验证;

二、实验原理

1、计数器的功能表见教材相关章节;

2、使用VHDL完成计数器的设计,并能在QUARTUS中完成相关的仿真验证;

三、实验设备和器材

电脑、QUARTUS集成开发环境。

四、实验内容和步骤

4.1 VHDL设计

1.分析下列例程,得出其功能(预习时自行完成);

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY CNTM IS

PORT (CLK,RST,EN,LOAD : IN STD_LOGIC;

DATA : IN STD_LOGIC_VECTOR(3 DOWNTO 0);

DOUT : OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

COUT : OUT STD_LOGIC);

END CNTM;

ARCHITECTURE behav OF CNTM IS

BEGIN

PROCESS(CLK,RST,EN,LOAD)

VARIABLE Q : STD_LOGIC_VECTOR(3 DOWNTO 0);

BEGIN

IF RST='0' THEN Q:= (OTHERS=>'0');

ELSIF CLK'EVENT AND CLK='1' THEN

IF EN='1' THEN

IF(LOAD='0') THEN Q:=DATA; ELSE

IF Q<12 THEN Q:=Q+1;

ELSE Q:=(OTHERS=>'0');

END IF;

END IF;

END IF;

END IF;

IF Q="1100" THEN COUT<='1';

ELSE COUT<='0';END IF;

DOUT<=Q;

END PROCESS;

END behav;

功能:模为13的加法计数器

- 在QUARTUS中建立相关工程,并将例程输入其中,并完成相应的功能仿真和时序仿真;

4.2 10进制计数器

修改上述例程,设计模为10 的计算器,并完成相应的功能仿真和时序仿真。

4.3 60位进制计数器

在4.2设计的10进制计数器的基础上,设计模为60的计数器,并完成相应的功能仿真和时序仿真。

五、实验记录和实验结果

5.1 VHDL设计

-

- 给出在QUARTUS中,使用VHDL设计电路的流程和步骤(预习时完成)

- 启动Quartus软件:安装并启动Quartus软件,在主界面选择"Create a New Project",创建一个新的工程。

- 2. 指定项目名称和存储位置:为项目选择一个合适的名称,并指定项目的存储位置。

- 3. 添加源文件:在项目设置界面,点击"Add Files"按钮,将VHDL源文件(.vhd)添加到项目中。可以选择直接编写代码或者导入现有的VHDL文件。

- 4. 设计顶层模块:在VHDL源文件中,编写顶层模块的代码。顶层模块是整个电路的主要组成部分,包含其他子模块的实例化以及输入输出端口的声明。

- 5. 添加并连接子模块:如果需要,可以编写其他子模块的代码,并实例化到顶层模块中。使用适当的连接语法将不同模块之间的输入输出端口连接起来。

- 6. 编译设计:在项目设置界面,选择"Compile Design",Quartus将对代码进行编译,并生成中间文件和报告。

- 选择file,new,university programVWF,建立一个waveform,以便进行波形调试。

- 8. 进行功能仿真:在项目设置界面,选择"Simulate",run functional simulate,Quartus将打开ModelSim仿真器或quartus II仿真器,并加载设计信号和端口信息。

9.进行时序仿真:在项目设置界面,选择"Simulate",run timing simulate,Quartus将打开ModelSim仿真器或quartus II仿真器,并加载设计信号和端口信息。

-

- 给出例程的功能

功能:模为13的加法计数器

-

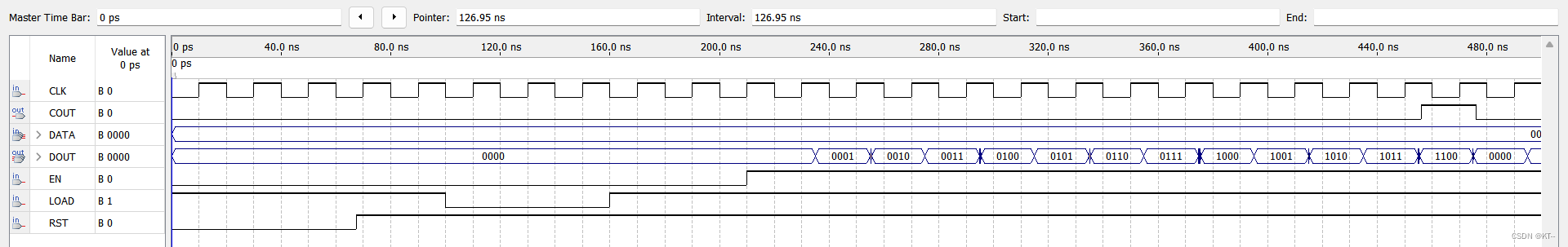

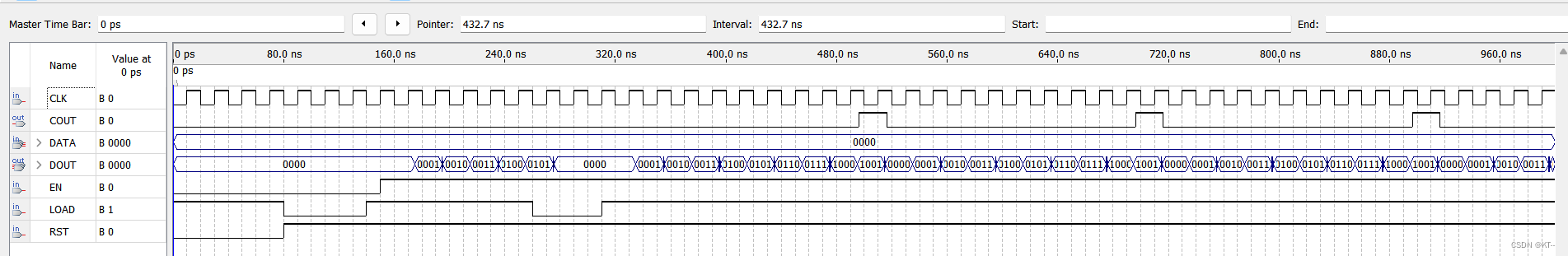

- 完成对例程的功能仿真和时序仿真,记录仿真结果

功能仿真:

时序仿真:

5.2 10进制计数器

- 给出10进制计数器的实现代码(请预习时完成)

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY CNTM10 IS

PORT (CLK,RST,EN,LOAD : IN STD_LOGIC;

DATA : IN STD_LOGIC_VECTOR(3 DOWNTO 0);

DOUT : OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

COUT : OUT STD_LOGIC);

END CNTM10;

ARCHITECTURE behav OF CNTM10 IS

BEGIN

PROCESS(CLK,RST,EN,LOAD)

VARIABLE Q : STD_LOGIC_VECTOR(3 DOWNTO 0);

BEGIN

IF RST='0' THEN Q:= (OTHERS=>'0');

ELSIF CLK'EVENT AND CLK='1' THEN

IF EN='1' THEN

IF(LOAD='0') THEN Q:=DATA; ELSE

IF Q<9 THEN Q:=Q+1;

ELSE Q:=(OTHERS=>'0');

END IF;

END IF;

END IF;

END IF;

IF Q="1001" THEN COUT<='1';

ELSE COUT<='0';END IF;

DOUT<=Q;

END PROCESS;

END behav;

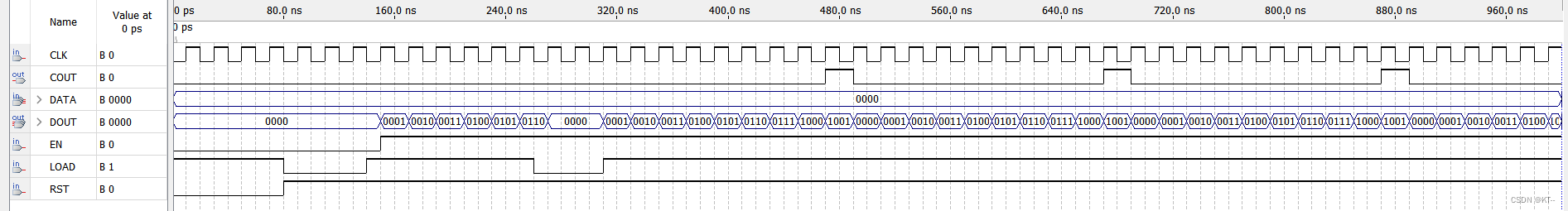

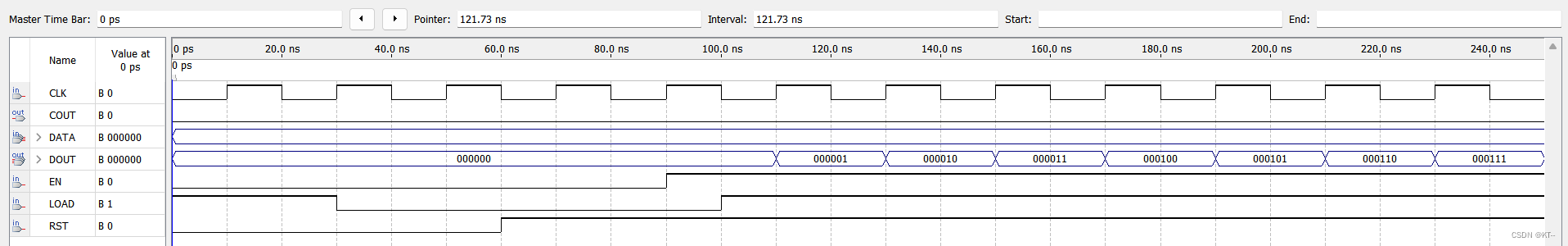

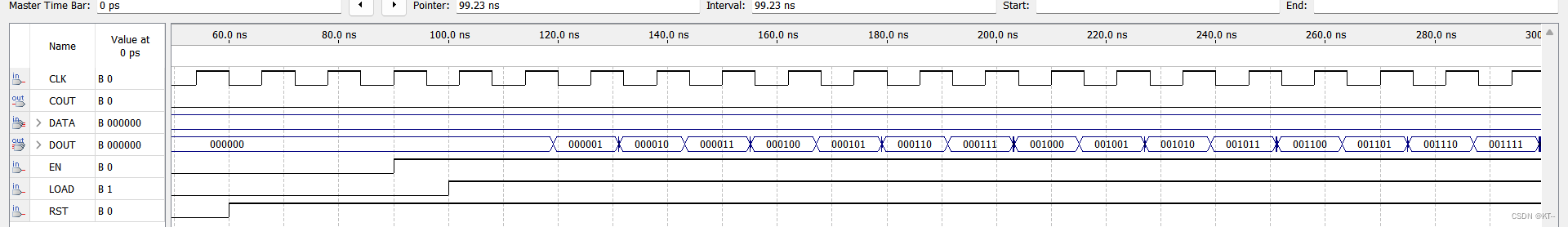

- 完成对所设计10进制计数器的功能仿真和时序仿真,记录仿真结果

功能仿真:

以4位二进制代码表示数字,当计数器计数至9(1001),开始置0(0000)

仿真正确

时序仿真:

仿真正确

5.3 60进制计数器

- 给出60进制计数器的实现代码(请预习时完成)

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY CNTM60 IS

PORT (CLK,RST,EN,LOAD : IN STD_LOGIC;

DATA : IN STD_LOGIC_VECTOR(5 DOWNTO 0);

DOUT : OUT STD_LOGIC_VECTOR(5 DOWNTO 0);

COUT : OUT STD_LOGIC);

END CNTM60;

ARCHITECTURE behav OF CNTM60 IS

BEGIN

PROCESS(CLK,RST,EN,LOAD)

VARIABLE Q : STD_LOGIC_VECTOR(5 DOWNTO 0);

BEGIN

IF RST='0' THEN Q:= (OTHERS=>'0');

ELSIF CLK'EVENT AND CLK='1' THEN

IF EN='1' THEN

IF(LOAD='0') THEN Q:=DATA; ELSE

IF Q<59 THEN Q:=Q+1;

ELSE Q:=(OTHERS=>'0');

END IF;

END IF;

END IF;

END IF;

IF Q="111011" THEN COUT<='1';

ELSE COUT<='0';END IF;

DOUT<=Q;

END PROCESS;

END behav;

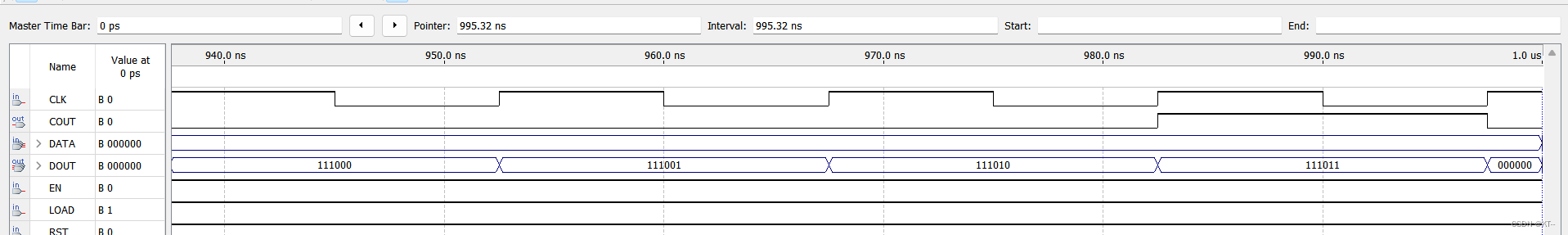

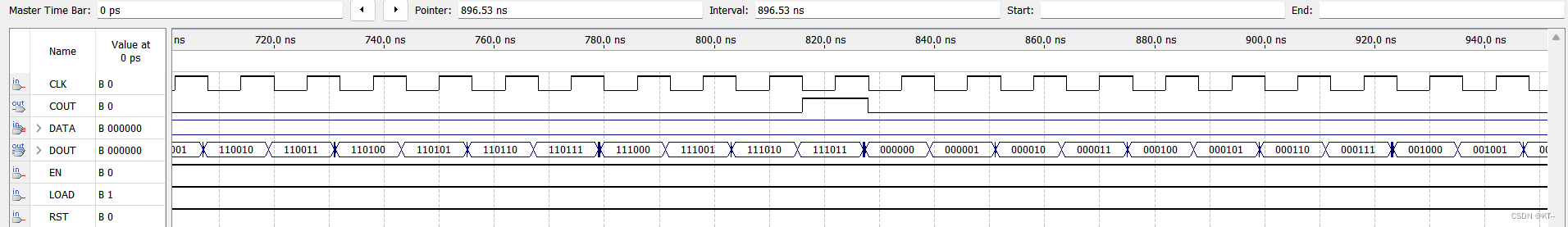

- 完成对所设计60进制计数器的功能仿真和时序仿真,记录仿真结果

功能仿真:

以6位二进制代码表示数字,当计数器计数至59(111011),开始置0(000000)

时序仿真:

六、实验预习要求

- 实验前认真阅读本实验指导;

- 熟悉quartus中相关操作及相关器件。

- 完成四和五中要求预习时完成的内容。

七、思考题。

1、在quartus完成对时序逻辑电路设计、功能仿真及验证的有哪些?

1.在quartus中创建一个新的工程,并创建一个新的原理图或VHDL文件。

2.在原理图或VHDL文件中设计时序逻辑电路,定义输入和输出端口。

3.编译和综合电路,检查是否有错误或警告。

4.创建一个测试平台文件,定义测试波形或测试向量。

5.进行仿真测试,观察时序波形是否正确。