关于FPGA对 DDR4 (MT40A256M16)的读写控制 4

语言 :Verilg HDL 、VHDL

EDA工具:ISE、Vivado、Quartus II

- 关于FPGA对 DDR4 (MT40A256M16)的读写控制 4

- 一、引言

- 二、DDR4 SDRAM设备中模式寄存器

- 重要的模式寄存器之MR1

- (1) 延迟锁定环(DLL)的启用

- (2)输出驱动器阻抗的控制方式

- (3)片上终止电阻(ODT, On-Die Termination)

- (4)加法延迟(ADDITIVE LATENCY, AL)

- (5)写均衡(Write Leveling)

- (5)输出使能

- (6)终止数据选通(Termination Data Strobe, TDQS)

- 关键词: 调用,Verilog HDL,ifdef 和 endif ,generate语句

一、引言

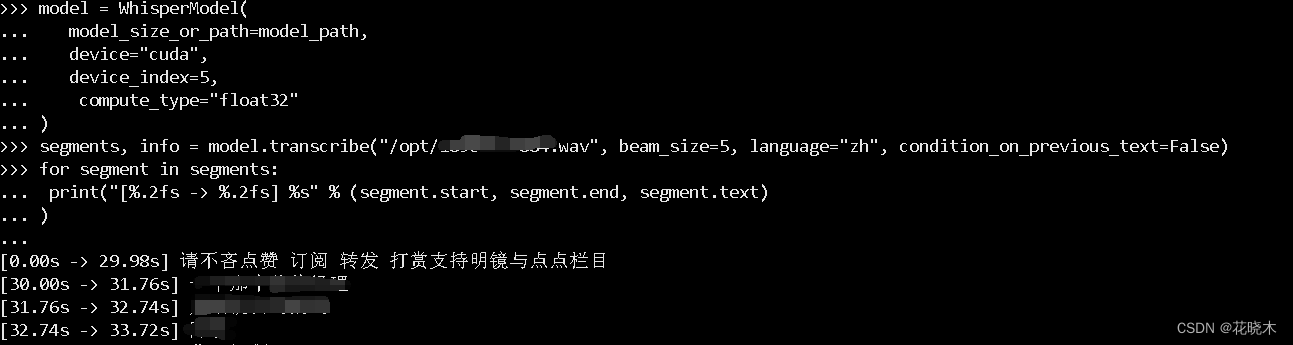

博主将会写一个系列的文章 关于FPGA对DDR4(MT40A256M16)的有效读写控制,最大化FPGA对DDR4的读写控制。首先将对DDR4的技术文档进行研读,注重DDR4的读写操作、刷新时间等。

二、DDR4 SDRAM设备中模式寄存器

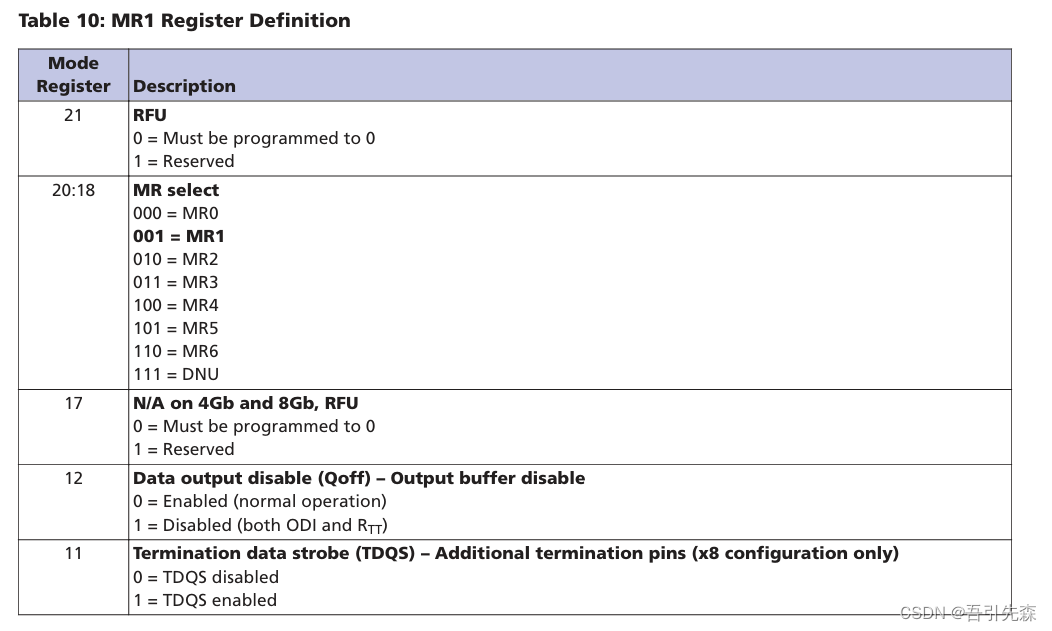

重要的模式寄存器之MR1

1、功能:MR0控制着设备的各种操作模式,具体的设置可以在随后提供的寄存器定义表中查看。并不是表中列出的所有设置在每个芯片上都可用;只有那些对于速度等级支持所必需的设置才是可用的。

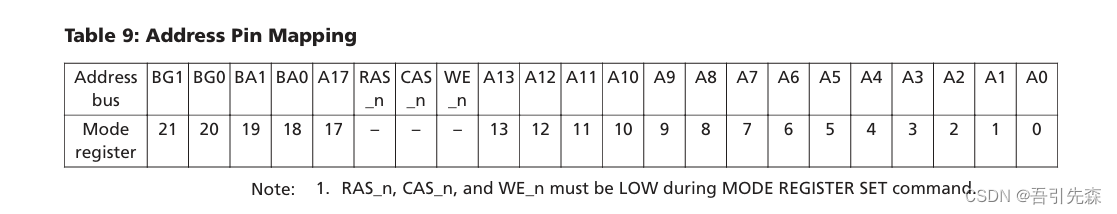

2、写入方法:MR0是通过发出模式寄存器设置(MRS)命令来写入的。在发出MRS命令的同时,需要控制BGx、BAx和Ax地址引脚的状态。

3、地址引脚映射:在MRS命令期间,地址引脚的映射关系会在随后的MR0寄存器定义表中展示

(1) 延迟锁定环(DLL)的启用

这三个参数是控制内存访问行为的关键参数

1、DLL的启用

DLL必须在正常操作中启用,并且在上电初始化以及在禁用DLL后返回正常操作时都需要启用。

2、DLL在自刷新操作中的行为

在正常操作期间(MR1[0]置为1以启用DLL),当进入自刷新(SELF REFRESH)操作时,DLL会自动禁用,并在退出自刷新操作时自动重新启用。

3、DLL复位后的同步

每次DLL被启用并在之后被复位,必须等待tDCLK个时钟周期后才能发出读(READ)或同步ODT(On-Die Termination)命令,以允许内部时钟与外部时钟同步。

tDCLK 期间CKE(时钟使能)必须连续置为为高电平。

1、DLL与写操作的关系

设备在任何写操作中不需要DLL,除非启用了RTT(WR)(写终止电阻),并且DLL需要正确进行ODT操作。

2、DLL关闭模式下的ODT支持

在DLL关闭模式下,不支持直接ODT特性。必须通过持续注册ODT引脚为低电平,或者通过MRS命令将MR1寄存器的RTT(NOM)位[9,6,2]编程为000来禁用ODT电阻。

3、DLL关闭模式下的动态ODT

在DLL关闭模式下不支持动态ODT特性;要在外部禁用动态ODT,使用MRS命令将MR2寄存器的RTT(WR)位[10:9]设置为00。

(2)输出驱动器阻抗的控制方式

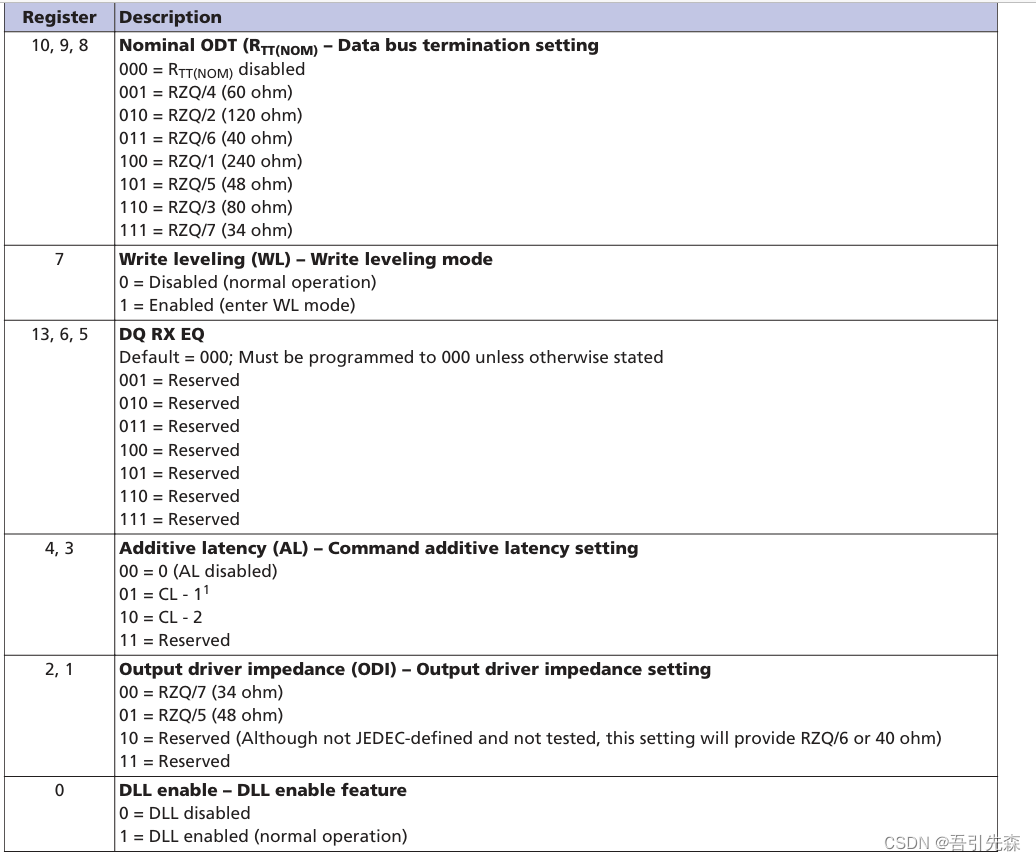

1、输出驱动器阻抗选择

DDR4 SDRAM设备的输出驱动器阻抗可以通过模式寄存器1(MR1)中的第2位和第1位(MR1[2,1])来选择。

2、寄存器定义表

具体的阻抗设置选项和对应的值会在MR1寄存器定义表中展示。

(3)片上终止电阻(ODT, On-Die Termination)

关于片上终止电阻(ODT, On-Die Termination)的不同终止值(RTT, Resistor Termination Type)的设置。

1、ODT终止值

设备能够提供三种不同的终止电阻值:

RTT(Park):当ODT信号为低电平时的终止值。

RTT(NOM):标称终止值,用于正常的操作条件。

RTT(WR):写操作期间的终止值,当ODT在写操作期间被启用时使用

ODT是一种用于减少信号反射和提高信号完整性的特性,特别是在高速内存接口中。通过编程不同的RTT值,系统设计者可以根据不同的操作条件和性能要求来优化内存设备的性能。

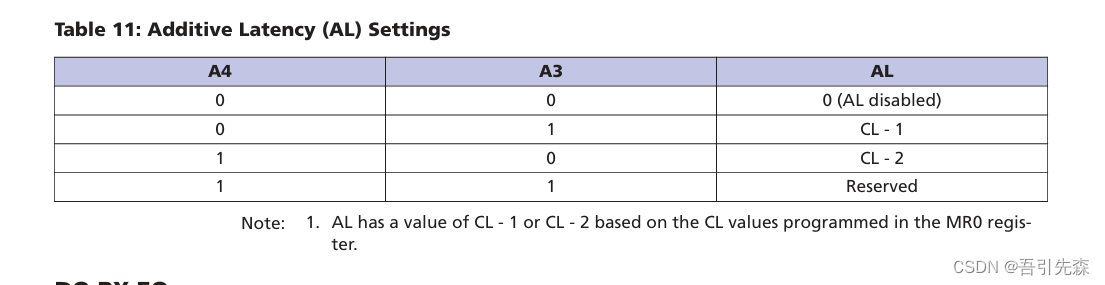

(4)加法延迟(ADDITIVE LATENCY, AL)

1、加法延迟(AL)的目的

AL操作被支持以提高设备在可持续性带宽方面的命令和数据总线的效率。

2、AL操作的工作原理

设备允许在读命令(READ)或写命令(WRITE)后立即发出激活命令(ACTIVATE)。

该命令会在设备内部保持AL时间长度,然后才被实际执行。

3、读延迟(RL)的控制

读延迟(RL)由加法延迟(AL)和CAS延迟(CL)寄存器设置的总和控制。

即:RL=AL+CLRL=AL+CL

**

4、写延迟(WL)的控制**

写延迟(WL)由加法延迟(AL)和CAS写延迟(CWL)寄存器设置的总和控制。

即:WL=AL+CWLWL=AL+CWL

5、AL操作的优势

通过使用AL,可以在不牺牲性能的情况下,减少对时钟周期的需求,从而提高内存子系统的效率。

6、AL操作的灵活性

由于AL允许命令在激活命令后立即发出,它为系统设计者提供了更大的灵活性来优化内存访问模式。

(5)写均衡(Write Leveling)

1、信号拓扑

设备使用飞线(fly-by)拓扑结构来传输命令、地址、控制信号和时钟。飞线拓扑的优点在于减少了stub的数量及其长度,有助于降低信号反射和交叉干扰。

2、信号问题

尽管飞线拓扑有其优势,但它也会导致在DIMM上每个DRAM之间的时钟和行选信号(strobe)的飞行时间(flight-time)不一致,即存在飞行时间偏斜(skew)。

3、写均衡功能

为了解决这个问题,设备支持写均衡特性。写均衡允许控制器对飞行时间偏斜进行补偿,确保数据在内存中正确写入。

4、控制器的作用

写均衡过程中,控制器会调整写操作的时序,以适应由于飞线拓扑引起的信号偏斜,从而确保数据信号的准确性和可靠性。

5、性能优化

通过写均衡,可以提高信号完整性,减少时序违规的风险,优化内存的性能和稳定性。

写均衡是DDR4内存技术中的一个重要特性,特别是在高频率高容量的内存系统中,它对于确保数据传输的准确性和系统的稳定性至关重要。控制器需要通过复杂的算法来实现写均衡,这通常涉及到对内存系统的深入理解和精确的时序控制。

(5)输出使能

通过模式寄存器1(MR1)的第12位(MR1[12])来控制输出使能:

1、输出使能/禁用控制

通过MR1[12]的设置,可以启用或禁用设备的所有输出引脚。这些输出引脚包括数据引脚(DQ)和数据选通信号(DQS)等。

2、输出禁用

当MR1[12]被设置为1时,所有输出引脚将与设备断开连接,这将消除输出驱动器的任何负载。这种设置对于某些特定的操作是有用的,比如在测量模块功耗时,可能需要禁用输出以避免影响测量结果。

3、输出使能

为了正常操作,应将MR1[12]设置为0。这样,输出引脚将正常工作,输出驱动器将加载并驱动信号到系统。

输出使能/禁用功能可以用于多种目的,比如在进行系统调试、功耗测量或在某些特定的低功耗状态下,可能需要暂时禁用输出。然而,在大多数正常操作中,输出应该是使能的,以确保数据可以正确地在内存设备和系统之间传输。

(6)终止数据选通(Termination Data Strobe, TDQS)

1、TDQS功能

TDQS是x8设备的一个特性,它提供了额外的终止电阻输出,这在某些系统配置中可能有用。

2、配置依赖性

由于TDQS功能仅在x8配置中可用,因此在x4和x16配置中必须禁用此功能。

3、TDQS与DQS的关系

在x4或x16配置中不支持TDQS时,当通过模式寄存器启用时,应用于TDQS引脚的相同终止电阻功能将应用于DQS引脚。

TDQS功能的主要目的是提供额外的信号完整性,通过在数据选通信号上增加终止电阻来减少反射和提高信号质量。然而,由于物理引脚的限制,TDQS功能与DM和DBI功能不能同时使用。系统设计者需要根据具体的系统配置和性能要求来决定是否启用TDQS功能,以及如何配置DM和DBI功能。在设计过程中,需要仔细考虑这些特性的兼容性和对系统性能的影响。

三、总结

本文详细介绍了FPGA对DDR4 SDRAM(MT40A256M16型号)的读写控制方法,重点探讨了DDR4的模式寄存器,尤其是MR1寄存器的不同配置选项及其对内存性能的影响。文章讨论了延迟锁定环(DLL)的启用、输出驱动器阻抗的控制、片上终止电阻(ODT)的设置、加法延迟(AL)以及写均衡等关键参数,解释了它们如何影响内存访问行为和性能。此外,还提到了输出使能和终止数据选通(TDQS)等特性,强调了正确配置这些参数以最大化FPGA与DDR4内存之间的读写效率和信号完整性的重要性。

![Linux[高级管理]——Squid代理服务器的部署和应用(传统模式详解)](https://img-blog.csdnimg.cn/direct/be4467ce207541fdb175c897344aeb68.png)