AXI VDMA 是 Xilinx 官方提供的高带宽视频 DMA IP,用于实现 AXI4-Stream 视频数据流与 AXI4 接口数据的转换,同时提供帧缓存与帧同步控制功能。本文主要介绍 AXI VDMA 的基本结构与原理,并简要介绍 VDMA 的配置与使用方法。

目录

1 VDMA 简介

2 VDMA 的配置

3 VDMA 的使用

1 VDMA 简介

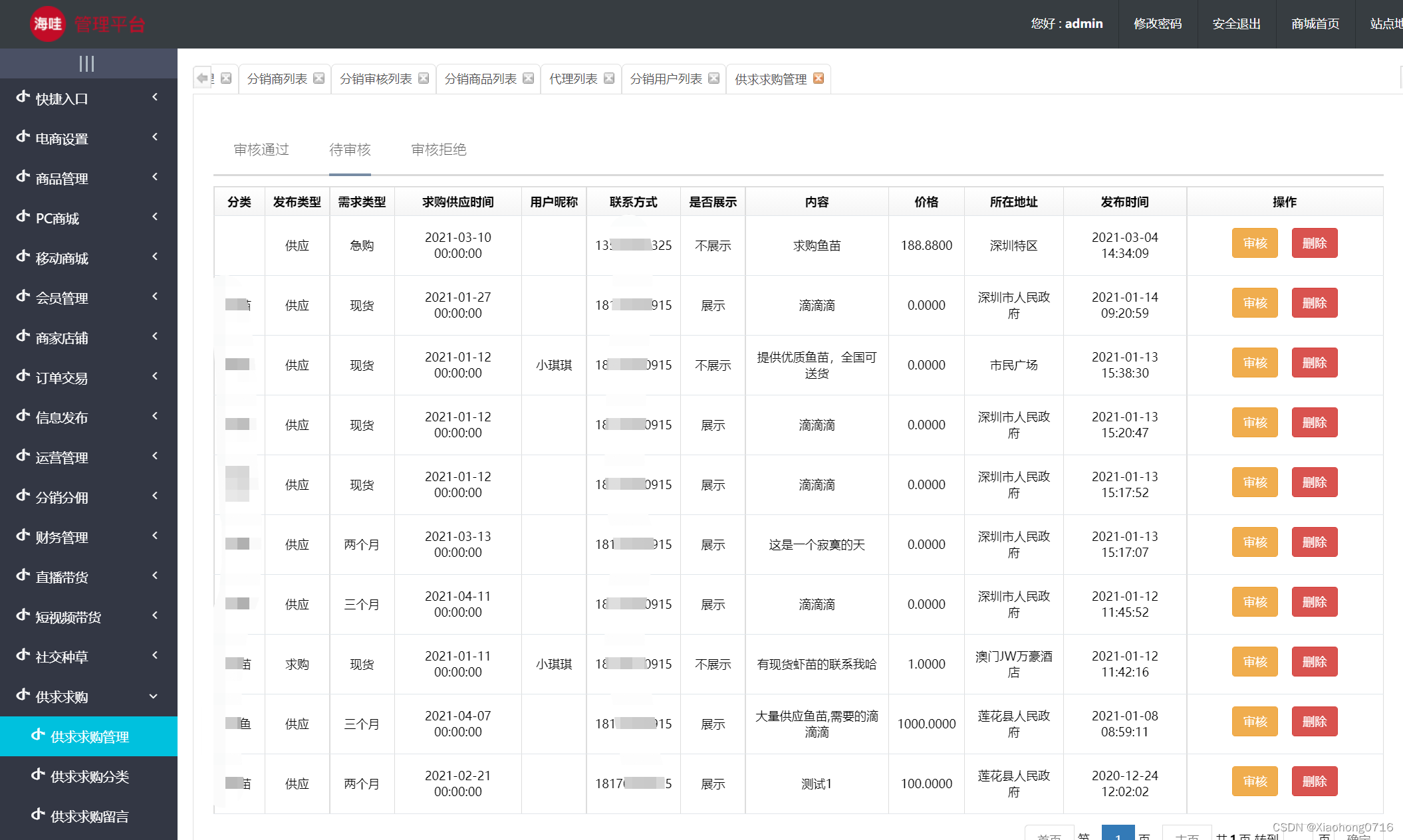

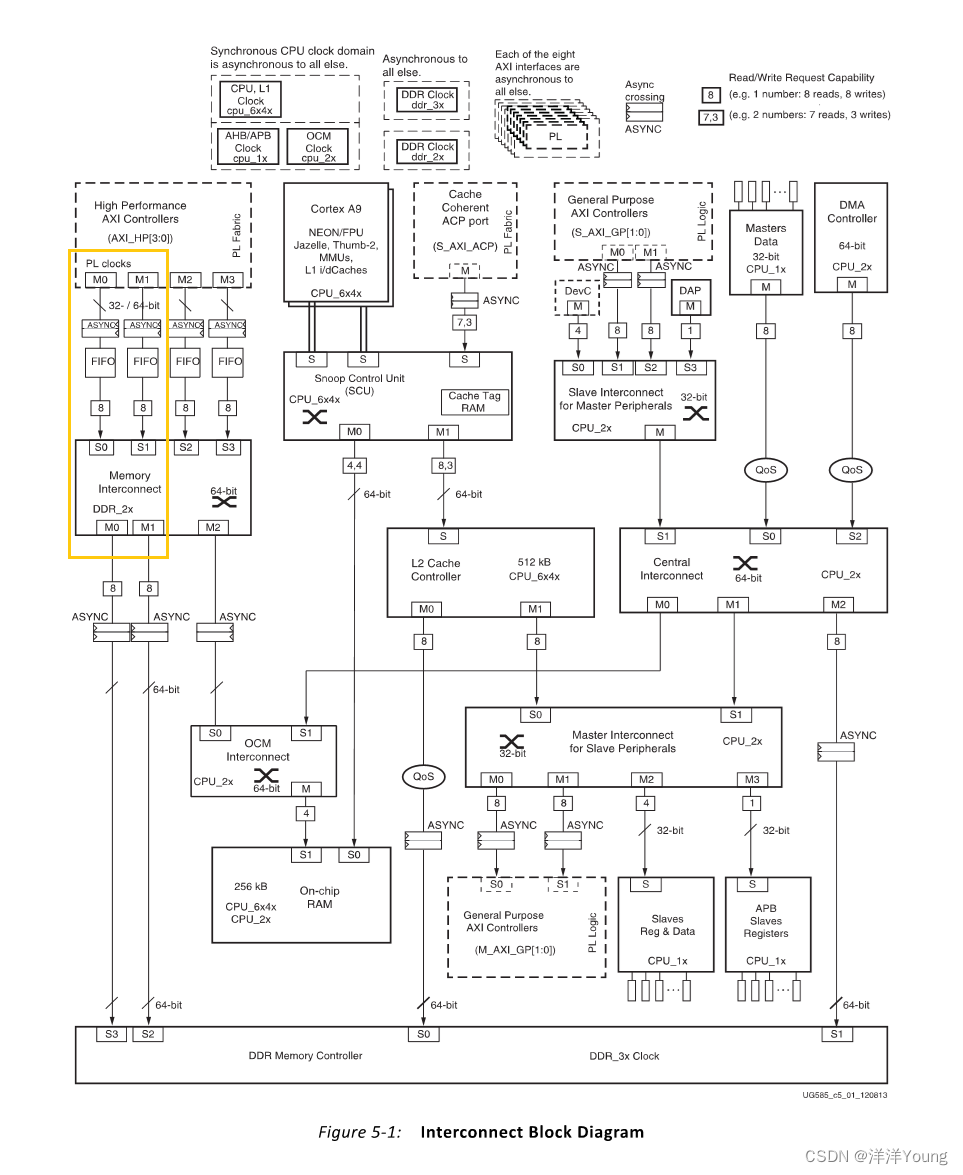

在前面《Zynq 芯片介绍》一文中,我们知道 Zynq 内部包含一个存储器单元,其中 DDR 内存控制器提供对 1GB 数据的访问,并且 PL 与 PS 对用户数据的访问是共享的。

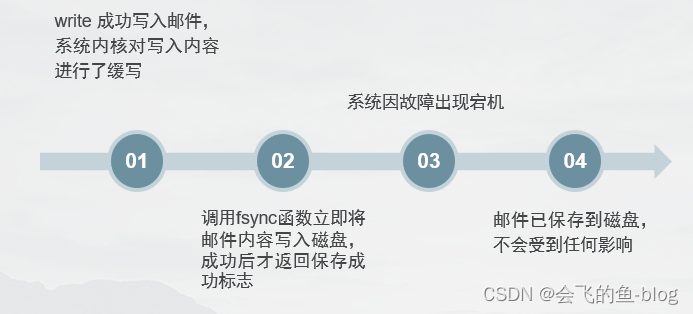

PS 端可以通过读写相应寄存器的方式,将数据写入 DDR3 或者从 DDR3 中读取数据。而对于 PL 端而言,则需要借助 AXI_HP 接口,才能实现对 DDR3 的访问。

S_AXI_HP0 和 S_AXI_HP1 是内存控制器专用接口,采用 AXI4 协议规范,HP 表示 High Performance,同时由于 DDR 读/写操作由 PL 端发起,所以这里是 AXI Slave 接口。

初始 OCM/DDR 地址映射

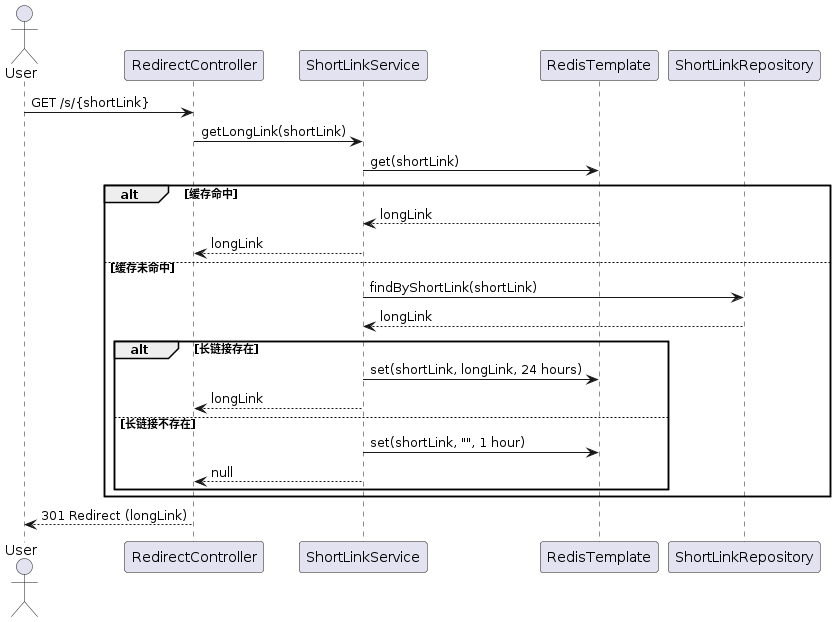

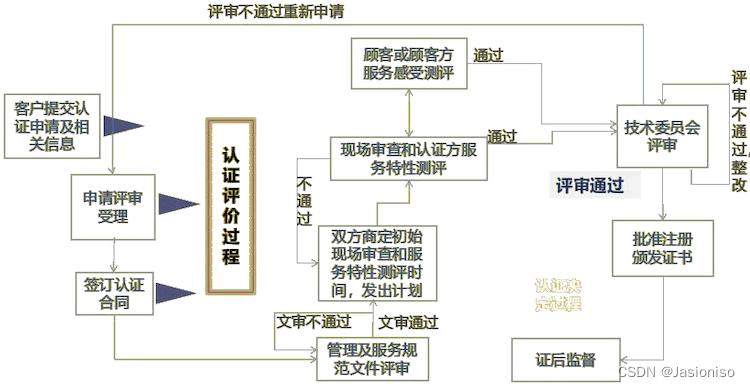

在视频处理中,许多视频应用程序离不开帧缓存,例如帧率改变、缩放、裁剪。对于视频图像,通常使用 AXI4-Stream 协议传输,因此需要借助 AXI VDMA IP 核,实现 AXI4 与 AXI4-Stream 接口的转换。

AXI VDMA 包括写通道和读通道,这两个通道是独立工作的。对于写通道,VDMA 将 AXI4-Stream Slave 数据流写入 DDR3(通过 AXI4 Master 接口);对于读通道,VDMA 从 DDR3 中读取数据(通过 AXI4 Master 接口)并转换为 AXI4-Stream Master 数据流。

其中 AXI-4 接口数据位宽可选 32, 64, 128, 256, 512, 与 1024 bit,AXI4-Stream 数据位宽可选 8 ~ 1024 bit,AXI4-Stream 数据位宽不超过对应通道的 AXI4 接口数据位宽。

同时 AXI VDMA 提供帧缓存(Frame Buffer)与帧同步控制(Frame Synchronization)功能,对于 32-bit 地址空间,最多支持 32 帧缓存。

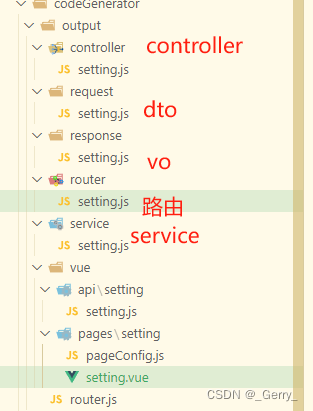

2 VDMA 的配置

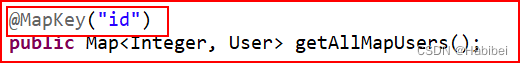

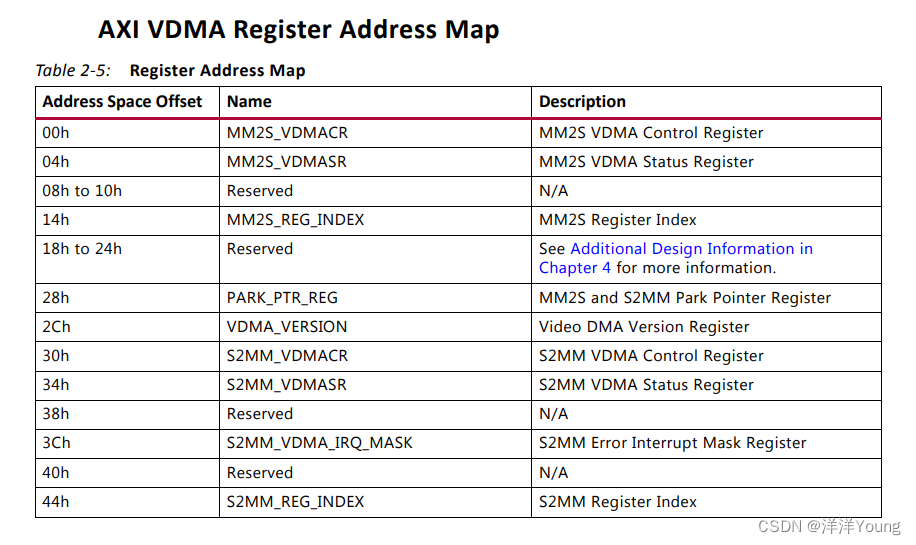

从 AXI VDMA 结构框图可以知道,AXI VDMA 使用 AXI4-Lite 接口进行配置。

配置数据按照 4 字节(32bit)小端对齐方式。

寄存器地址映射表

其中 MM2S 表示读通道,S2MM 表示写通道。

3 VDMA 的使用

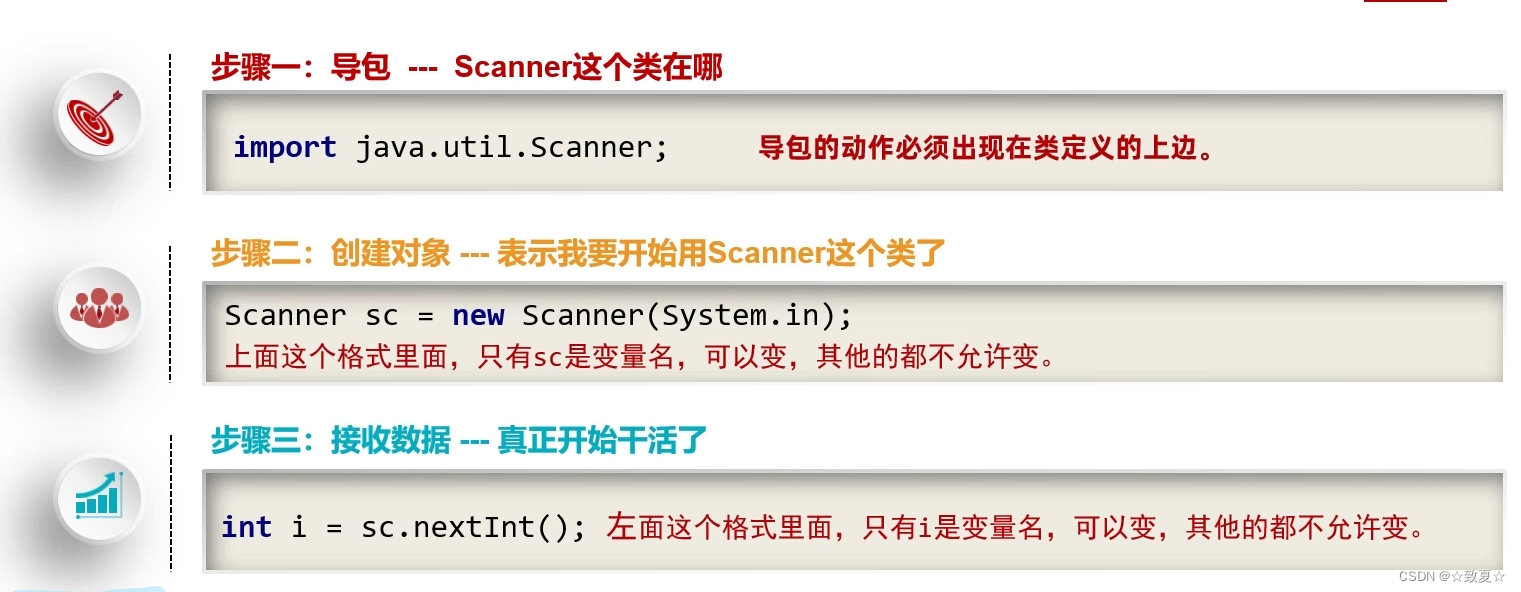

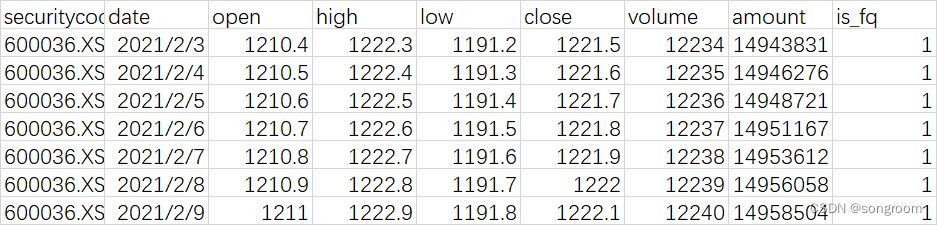

VDMA IP 核的配置主要包括读/写通道 Memory Map Data,Stream Data 位宽配置、Frame Buffer 与 Line Buffer 深度配置。

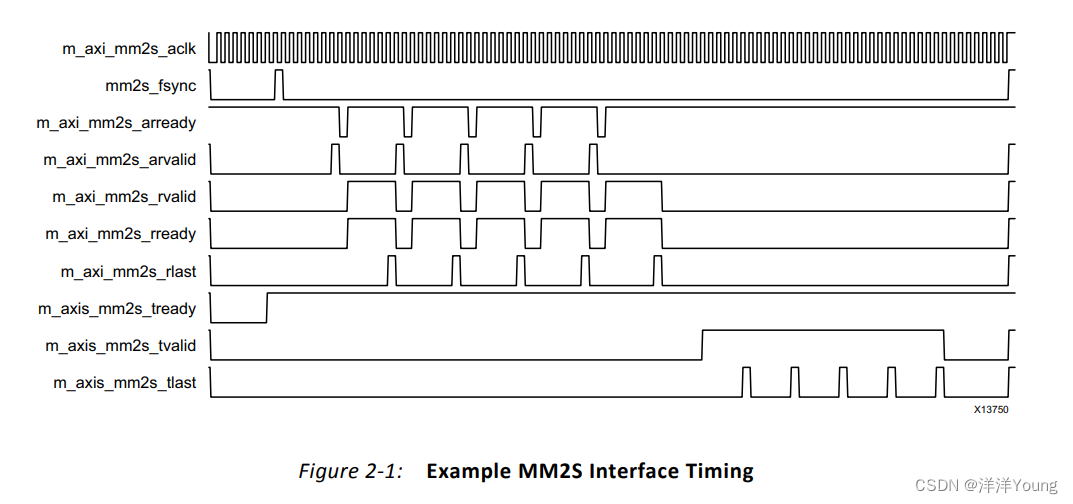

在接收到 mm2s_fsync 信号之后,VDMA 开始工作。m_axi_mm2s_rlast 用于指示图像中一行数据的结束。VDMA 将接收到的数据写入 Line Buffer,随后传输到 AXI4-Stream 端。

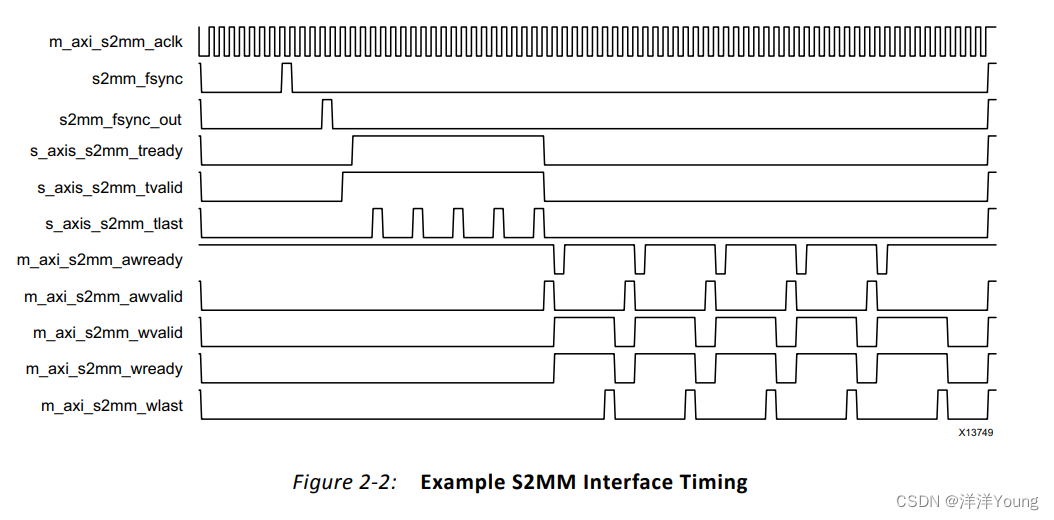

对于 s2mm 通道,VDMA 在接收到 s2mm_fsync 信号之后开始工作。VDMA 将 AXI4-Stream 视频数据流写入 Line Buffer,随后驱动 AXI4 端信号,将数据传递给 DDR3。

未完待续 ~