六、内部模拟调光

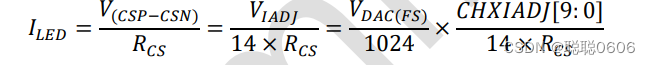

一个精确的10位DAC作为BUCK电流调节回路的参考发生器。与SPI通信时,DAC参考电压可由主机改变并调节电流在BUCK不断切换的同时,也会发生相应的变化。10位分辨率的DAC正在设计中满足电流变化平稳的要求。一个1.713mA电流步使光亮度连续变化。

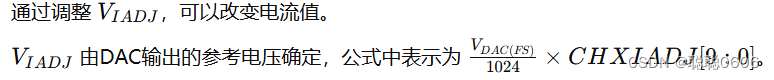

LED电流的计算方法:

例子:

七、PWM调光

除了模拟调光之外,iND87520还支持PWM调光。PWM调光由数字逻辑控制,通过SPI通信或UDIMx引脚的外部PWM信号激活。

1.内部PWM调光

内部PWM调光由10位PWM占空比寄存器和3位PWM频率配置寄存器。

0位的PWM占空比寄存器允许设置从0到1024的占空比,模拟调光的分辨率相同。这种高分辨率在低亮度应用中尤为重要,因为模拟调光在低亮度下可能会由于偏移影响而表现不佳,而PWM调光则在占空比代码较小时仍能保持良好的线性度

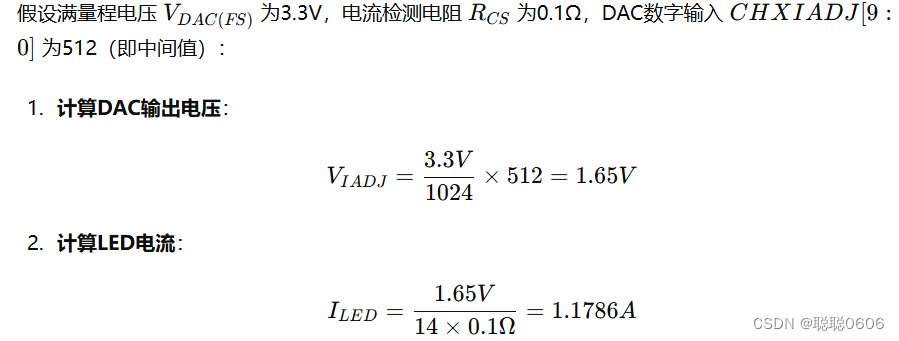

在低亮度应用中,当模拟调光出现偏置时,PWM调光因其更好的线性度而优于模拟调光即使PWM占空比码很小。此外,3位的PWM频率寄存器可以选择8种不同的频率,计算公式如下,其中CLK为主时钟频率,DIV为分频器设置的分频数。结果频率通过选择适当的分频数来调节

例子:假设主时钟频率 CLK 为 10 MHz,分频数 DIV 设置为 64:

2.外部PWM调光

外部PWM调光设计遵循UDIMx引脚的开关信号。

(1)外部PWM调光频率要求:

频率限制:外部PWM信号的频率应低于1kHz,而内部PWM调光的最高频率为1.5kHz。

逻辑输入阈值:逻辑输入阈值和

分别是VIN UVLO的下降阈值和上升阈值。

(2)VIN UVLO(欠压锁定):

功能:VIN UVLO功能用于监测输入电压VIN,并在电压过低时关闭驱动器以保护电路。

触发:VIN UVLO也由UDIMx引脚上的PWM信号触发,这意味着外部PWM调光信号不能单独控制两个通道。

(3)工作原理

①信号输入:外部PWM信号通过UDIMx引脚输入到iND87520,该信号的频率应低于1kHz,以确保正确的调光功能。

②调光控制:外部PWM信号的占空比控制LED的亮度,逻辑输入阈值和

决定了信号的有效性。当PWM信号的电压下降到

以下时,信号被认为是低电平;当电压上升到

以上时,信号被认为是高电平。

(4)与内部PWM调光的比较

①内部PWM调光的最高频率为1.5kHz,比外部PWM调光的频率更高,适用于更精细的亮度控制。

②外部PWM调光主要用于较低频率的应用,确保在低频下也能实现稳定的调光效果。

| 特性 | 内部PWM调光 | 外部PWM调光 |

| 频率范围 | 最高1.5kHz | 低于1kHz |

| 分辨率 | 高,10位PWM占空比寄存器和3位频率寄存器 | 取决于外部PWM信号 |

| 线性调光 | 更好 | 较差 |

| 控制灵活性 | 高,通过SPI通信可单独控制两个通道 | 低,受VIN UVLO影响 |

| 应用场景 | 高端照明、显示设备 | 简单照明系统、与其他控制系统集成 |

八、模式状态介绍

芯片可以在不同的工作模式下工作:正常模式,独立模式,Limp-Home模式。

在正常模式,降压操作可以直接由寄存器或外部引脚控制,具体取决于通过SPI通信的配置。

在Limp-Home模式下,buck操作由一组Limp-Home寄存器的配置决定,必须通过SPI通信预设在进入此模式之前。独立模式通过芯片提供对buck的控制没有寄存器访问的引脚。

设备不使用时提供了一种休眠模式。

在进入任何这些工作模式之前,芯片在3个预状态下转换:上电复位状态,SPI状态,加载状态。

1.状态介绍

(1)上电复位状态

在正常操作的供电电压 V5D 建立之前,芯片处于上电复位(Power-On Reset,POR)状态。在此状态下,芯片执行以下操作:

①寄存器复位:所有寄存器重置为默认值。这意味着所有配置和设置将返回到芯片出厂时的初始状态。

②通道关闭:两个通道均关闭。即,在此状态下,芯片不会驱动任何负载或输出电流。

③ADC禁用:模数转换器(ADC)被禁用。这意味着在此状态下,芯片不会进行任何模拟到数字的信号转换。

进入下一个状态的条件:

当供电电压 V5D 超过 4.1V 时,芯片将从 POR 状态进入下一个状态(通常是正常操作状态)。这意味着在 V5D 达到 4.1V 之前,芯片将保持在 POR 状态,并执行上述操作。

(2)SPI状态

在供电电压 V5D 建立之后,芯片会期待接收到一个正确的 SPI 帧。根据是否接收到有效的 SPI 帧,芯片将进入不同的操作模式。

①检测 SPI 帧:在供电电压 V5D 建立之后,芯片会监控 SPI 总线,以检测是否接收到有效的 SPI 帧

②进入加载状态(Load State):如果检测到有效的 SPI 帧,芯片会进入加载状态。在此状态下,芯片会完成寄存器配置,然后进入正常模式(Normal Mode)或 Limp-Home 模式。在进入 BUCK 操作之前,需要进行优先系统配置。

③进入独立模式(Standalone Mode):如果未检测到有效的 SPI 帧,芯片会进入独立模式。在独立模式下,不需要通信,BUCK 操作主要由外部硬件直接控制。

④在供电电压 V5D 建立后,为了检测有效的 SPI 帧,内部看门狗计时器会启用,并监控 224 个系统时钟周期(约 1.68 秒)。如果在此时间内未接收到有效的 SPI 帧,看门狗计时器将触发重置,芯片将进入独立模式

(3)加载状态

①检测 SPI 状态:在供电电压 V5D 建立后,芯片进入检测 SPI 状态(Detect SPI state),期望接收到一个有效的 SPI 帧。

②异常处理:如果独立模式(Standalone mode)是意外的(即,系统期望进入其他模式而不是独立模式),芯片会从检测 SPI 状态直接过渡到加载状态(Load state)。

③加载状态:加载状态设计用于通过 SPI 通信配置寄存器,以便进入正常模式(Normal mode)或 Limp-Home 模式。在加载状态下,CHxEN 位设置为 0,以防止 BUCK 在默认寄存器值下运行。必须读取并清除 PC 位后才能退出加载状态。

④过渡到休眠模式:加载状态可以直接通过向 SLEEP 寄存器写入 “01” 进入休眠模式(Sleep mode)以节省功耗,而无需先进入正常模式。

2.独立模式

(1)介绍

在独立模式下,芯片无需额外的SPI通信即可工作,参考电流由LHI引脚电压设定。当电压低于148mV时,两个通道都会被禁用,每个通道的PWM/使能/禁用由UDIMx引脚控制,故障反应设置为自动重启模式,故障计时器设置为3.6ms,独立模式下看门狗计时器被禁用。

(2)独立模式与SPI通信模式(正常模式)的切换

①进入到独立模式:如果在SPI状态(Detect SPI state)下没有在看门狗计时器超时前接收到有效的SPI帧,芯片将进入独立模式。

②从独立模式返回检测SPI状态:通过在读取并清除CMWTO位后向RESET寄存器写入0xD4,可以从独立模式返回检测SPI状态。

③直接进入加载状态:通过向RESET寄存器写入0xC3,芯片将直接进入加载状态(Load state)。

3.Limp-Home模式

(1)进入Limp-Home方法

在加载状态或正常模式下,当发生以下任何情况时,芯片进入Limp-Home模式:

①“LHSW位”设置为“1”

②三次看门狗超时

(2)芯片按以下顺序切换到正常模式:

①读取并清除CMWTO位

②将LHSW位写为0

(3)电流参考选择

buck根据LHM寄存器在Limp-Home模式下工作,因此它们必须在加载模式下配置:

①在Limp-Home模式下,电流参考可以选择内部LHxIADJ或通过ADC测量的外部LHI引脚电压。这由LHEXTIADJ位选择

②通过ADC测量LHI电压并存储在LHI寄存器中。

③使用数字低通滤波器防止开关噪声耦合到LHI引脚。滤波后的值存储在LHIFILT寄存器中。

④使用148 mV的下降阈值和200 mV的上升阈值来启用/禁用两个通道。

4.正常模式

(1)Load状态到Normal模式

①读取并清除PC位

②将CHxEN设置为1

③将LHSW设置为0,并读取清除看门狗超时计数器,强制进入Normal模式

④向SLEEP寄存器写入1,设备进入Sleep模式

(2)正常模式下的故障处理

①锁存故障带有锁存选项时,设备返回Load状态,CHxEN位被设置为0

②选择自动重启选项时,设备在故障计时器之后尝试恢复

5.睡眠模式

(1)在进入Sleep模式时,以下情况发生

①内部稳压器与V5A引脚断开

②振荡器被禁用

③CHxEN位被设置为低

④各通道被禁用

⑤ADC和DAC操作被禁用

⑥MOSFET被关闭

⑦用于测量VINx和V5D的电阻分压网络被断开

⑧任何对其他寄存器的读取将返回0

(2)SPI在Sleep模式下的工作

SPI块由V5D供电,因此可以在Sleep模式下监控SPI总线。当检测到对SLEEP寄存器的写操作为“00”时,设备将转换到Load模式。

(3)Sleep模式下的电压变化

在Sleep模式下,由于所有内部负载被关闭,高侧栅极驱动相关的泄漏电流被迫通过开关节点SWx,因此输出电压将升至4V以上。由于V5A内部断开,V5AUV位被设置。当退出Sleep模式时,该位被清除。

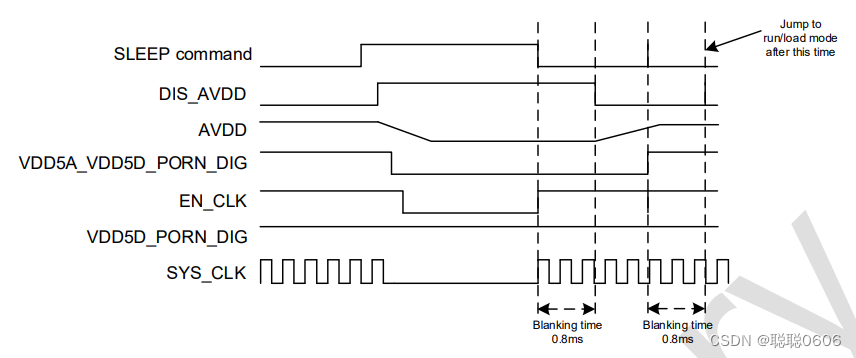

(4)Sleep模式的时序

如上图所示展示了进入和退出Sleep模式的时序图。

①Sleep命令触发后,DIS_AVDD信号和AVDD信号下降

②VDD5A_VDD5D_PORN_DIG信号随之下降。

③EN_CLK信号随后被禁用。

④SYS_CLK信号停止,表示振荡器禁用。

⑤设备进入Sleep模式,经过0.8ms的遮蔽时间后,进入稳定状态。

(5)退出Sleep模式

当监测到SLEEP寄存器的写操作为“00”时,设备退出Sleep模式,并经过0.8ms的遮蔽时间后,进入Load模式。

6.模式比较

九、SPI协议格式

这个芯片仅作为SPI从机工作。相关的引脚包括3个TTL输入引脚SSN/SCK/MOSI和1个开漏输出引脚MISO。它们与SPI总线的兼容性如下:

①片选引脚SSN:低电平有效,用于指示数据交换。当SSN为高电平(不活动)时,MISO显示高阻抗。

②SCK相位:当SSN变为有效时,第一个数据位出现在MOSI/MISO上。MOSI上的串行数据位在SCK的奇数边缘采样,而串行数据位在偶数边缘移出到MISO。

③SCK极性:奇数边缘为正边缘。

④数据顺序:最重要的位(MSB)首先传输。

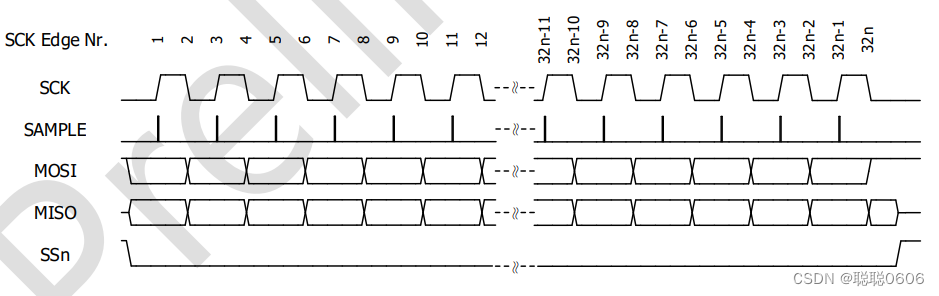

SPI帧是不可配置的16位。因此,有效传输需要16个SCK周期的正整数倍(16、32、48……),即成功的传输要求在经历16/32/48……个SCK周期后,SSN变为高电平。如果SSN在每16个SCK周期后保持低电平,SPI移位寄存器中的数据将在每来另一个16个SCK周期时继续从MOSI移入,并移出到MISO。时序图如图所示

- SCK信号在每16个时钟周期后出现低到高的转换。

- SAMPLE信号在每个奇数边缘采样MOSI数据。

- MOSI数据在每个奇数边缘采样,并在偶数边缘移出到MISO。

- SSN信号在整个传输过程中保持低电平,表明一直在进行数据交换。

图中显示了多个16位帧的连续传输,符合SPI从设备的工作模式和传输要求。

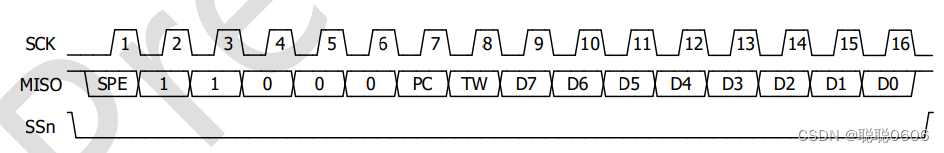

1.命令帧

命令帧由主设备发送,并由从设备接收。此帧启动通信过程。命令帧的结构和内容可能因使用的具体协议而异。

当SSN在有效的SCK周期后变得很高时,最近收到的16个数据位被视为命令帧,它只从主发送到从。

它由一个命令位、6位ADDRESS、一个奇偶校验位(奇偶校验)和8位DATA组成。

①1位命令位(CMD)。CMD = 1表示写命令;CMD = 0表示读命令。

②6位地址位(A5:A0)。

③1位奇偶校验位:计算方法如下PARITY = XNOR (CMD, A5...A0, D7…D0)。

④8位数据(D7…D0)。对于读命令,将DATA位设置为零。

接收到命令帧后,当主设备发出下一个信号时,响应帧被移出

2.读响应帧

响应帧是在从设备接收到并处理命令帧后发送回主设备的。此帧包含主设备请求的信息或关于执行命令的状态信息。

读取响应帧在任何需要从主机发送读取事务的时候被传输。它包括:

①SPI错误位(SPE),SPE=0没错误,SPE=1有错误。

②5位保留位(固定为“11000”)。

③1位PC位指示是否发生电源重启

④1位TW位指示是否存在温度警告

⑤8位数据位 SPE=0时有效

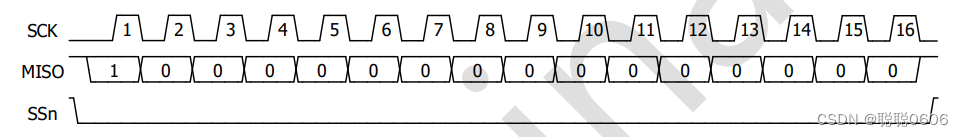

3.写响应帧

当收到写命令帧而没有SPI错误时,写响应帧在下一个事务间隔内发回。刚写的寄存器的地址和数据返回以指示写入成功,而不需要额外的读命令。组成如下:

①SPI错误位(SPE),SPE=0没错误,SPE=1有错误。

②1位命令位(CMD)。CMD = 1表示写命令;CMD = 0表示读命令。

③6位地址位(A5:A0)。

④8位数据(D7…D0)。从寄存器读取的数据

4.错误帧

这个帧响应一个带有SPI错误的帧,它在MSB后面只是1位的1和15位的零。

十、网络拓扑结构

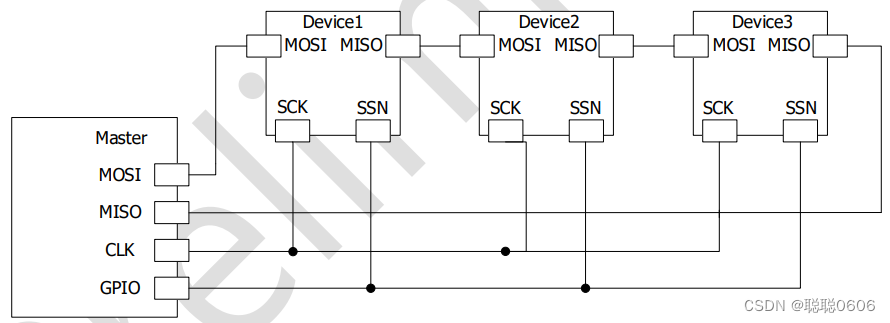

SPI总线支持星形连接和菊花链网络拓扑结构。

1. 星形连接

在星形连接中,每个设备连接到一个单独的芯片选择信号,而所有设备共享SCK/MOSI/MISO。

2.菊花链

在菊花链网络配置中,所有设备共享单个芯片选择信号,而MOSI/MISO从一个设备连接到另一个设备。每16个SCK周期后,数据为从一个设备转移到另一个设备。经过16*N个SCK循环后,数据通过全部设备。