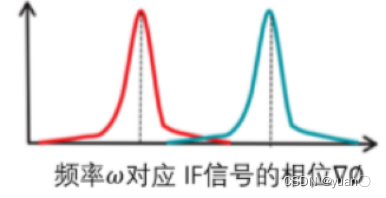

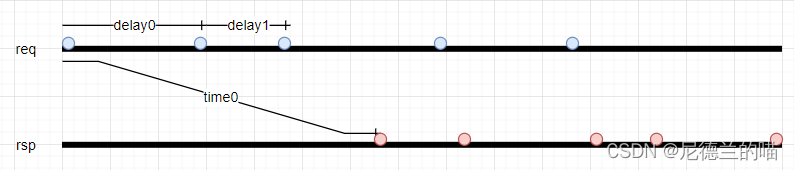

针对啸叫的问题,本文设计了一种基于移频算法的啸叫抑制器。采用高性能音频编解码芯片对音频信号采样,移频器对采样所得的音频信号进行移频,移频频率范围为0~8Hz,再用音频芯片输出,采用FFT算法计算出啸叫点频率值,显示在LCD1602上,此移频器可达到快速有效的啸叫抑制效果。

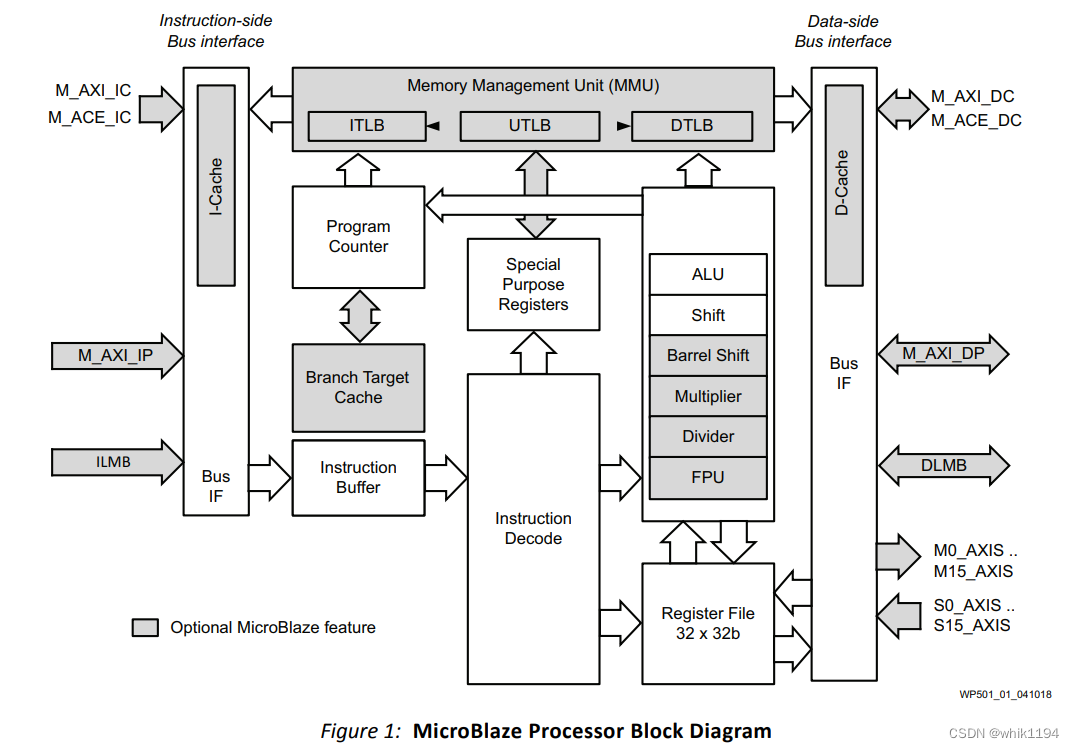

本系统采用Altera公司的Cyclone II系列FPGA作为移频、FFT等系统功能实现的硬件支持,高精度音频编解码芯片WM8731作为音频信号的采样和输出控制。

1啸叫检测方案

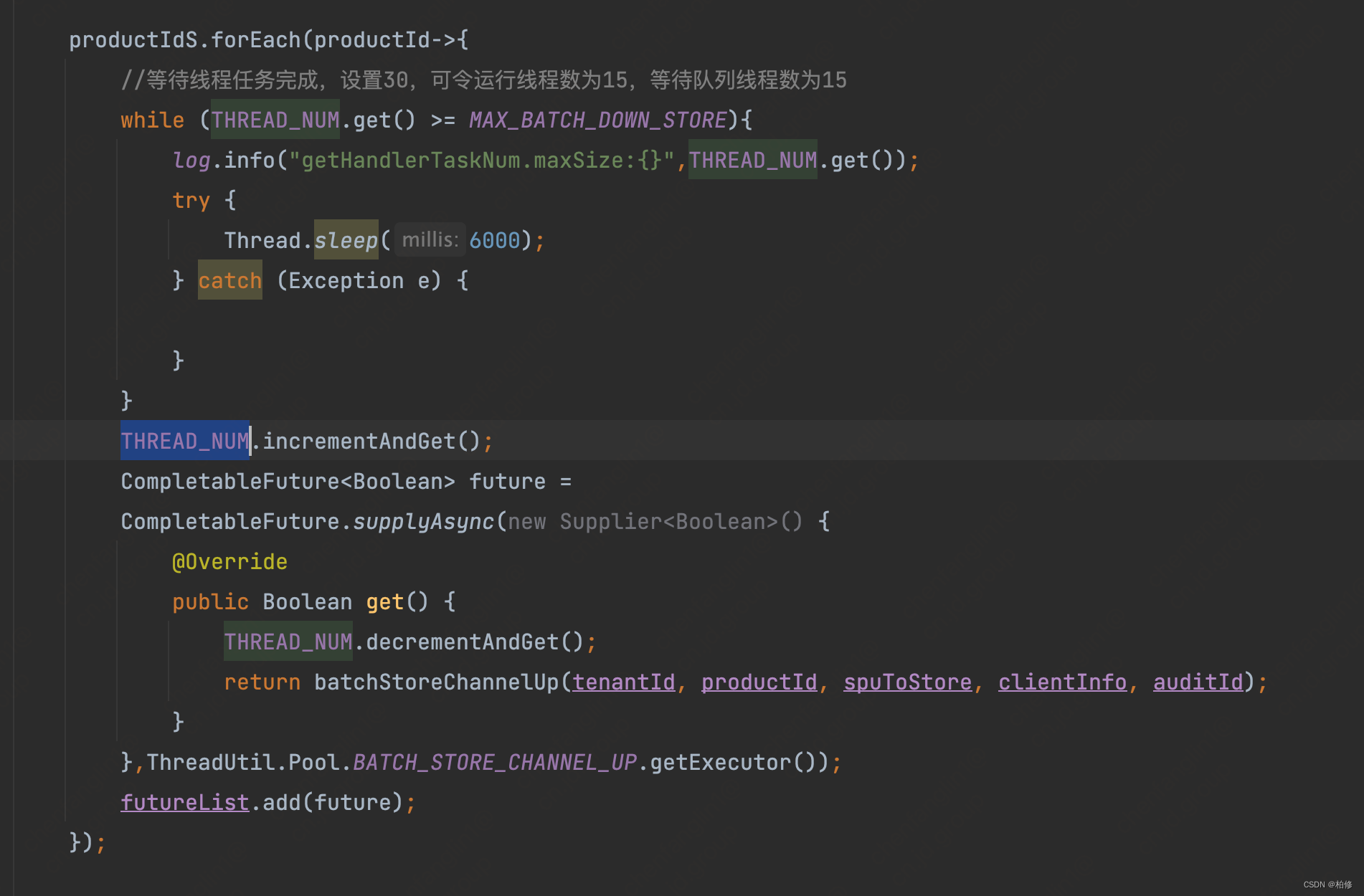

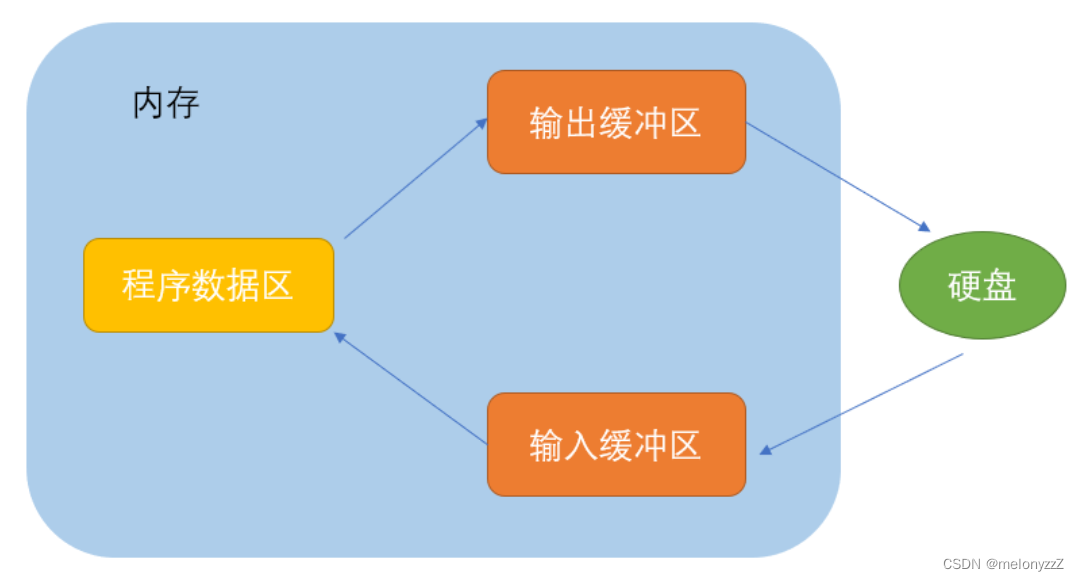

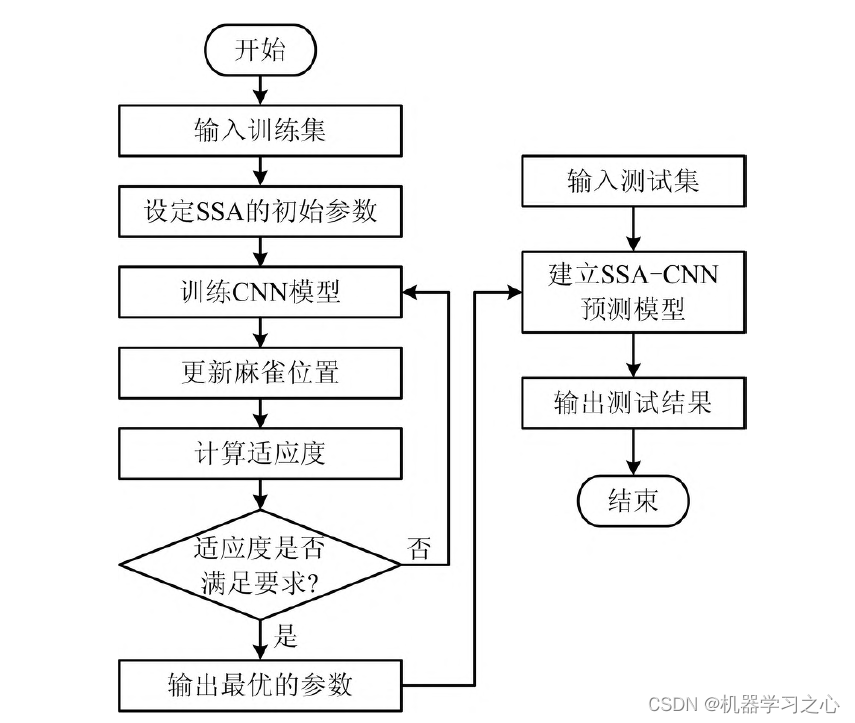

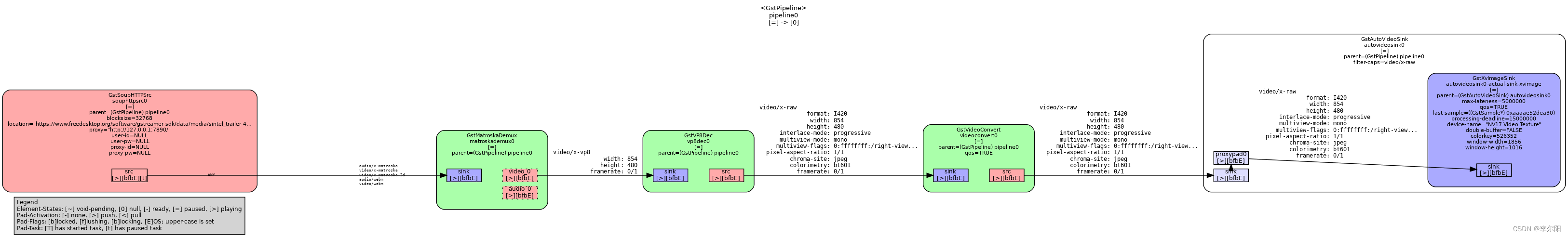

本系统中采用傅里叶变换算法计算时域信号的频谱值来确定啸叫频率点。傅里叶变换一般采用快速傅立叶变换算法,该算法实现有两种方案,一种为硬件FFT,另一种用软件代码实现FFT。在FPGA中使用硬件电路实现FFT算法,运算速度快,效率高,且Altera公司有成熟的FFT IP核,开发周期短,但硬件FFT需要较多的Memory单元存储旋转因子和临时数据以及必要的加法器和乘法器,占用较多的逻辑资源,本系统中所使用的FPGA内部资源并不丰裕,故采用第二种方案。使用软件方式实现FFT,速度相对来说比较慢,但消耗资源小,在对于实时性要求不高的系统而言,软件FFT是个不错的选择。在Cyclone 系列的FPGA中,可通过定制NIOS II内核来完成软件FFT的实现。在本系统中,对于时钟频率为100MHz的NIOS II内核,完成一次1024点的FFT算法的时间在1秒左右,可以完成实时更新啸叫频率点的功能。

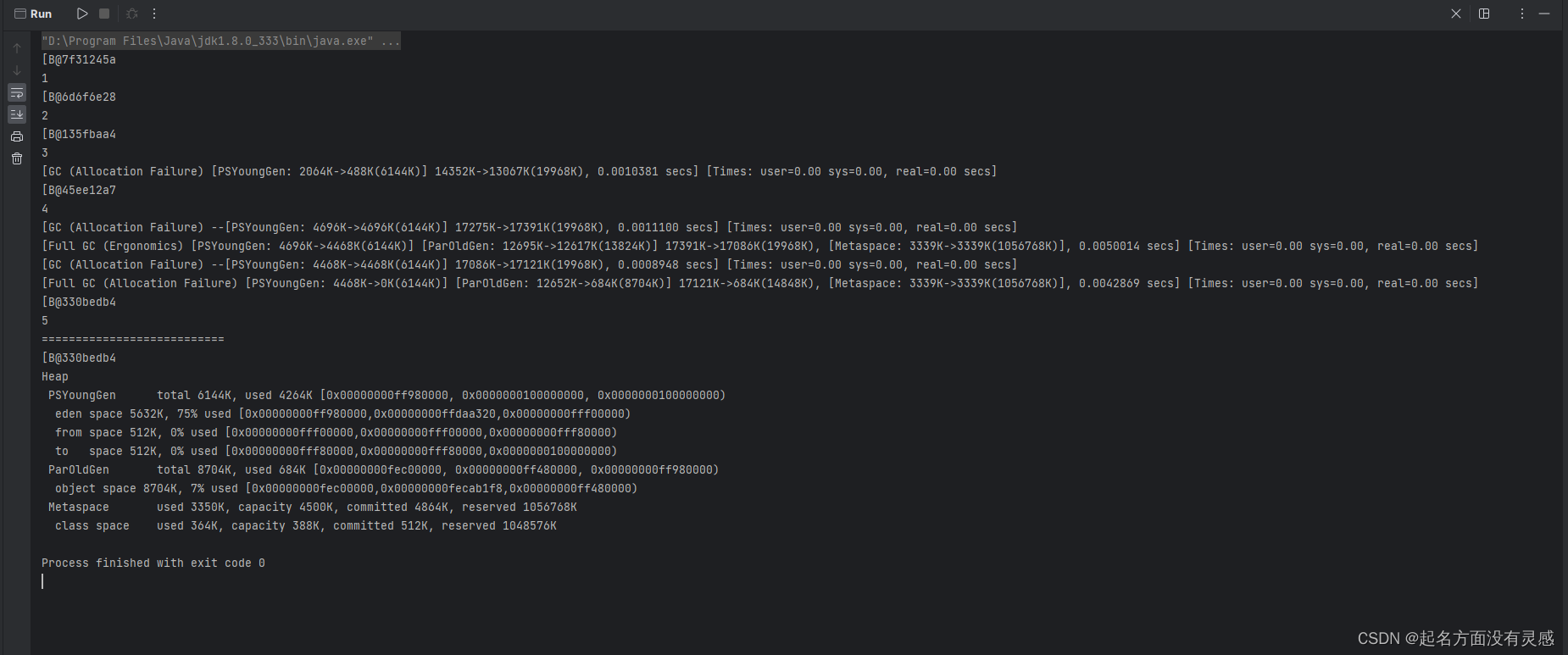

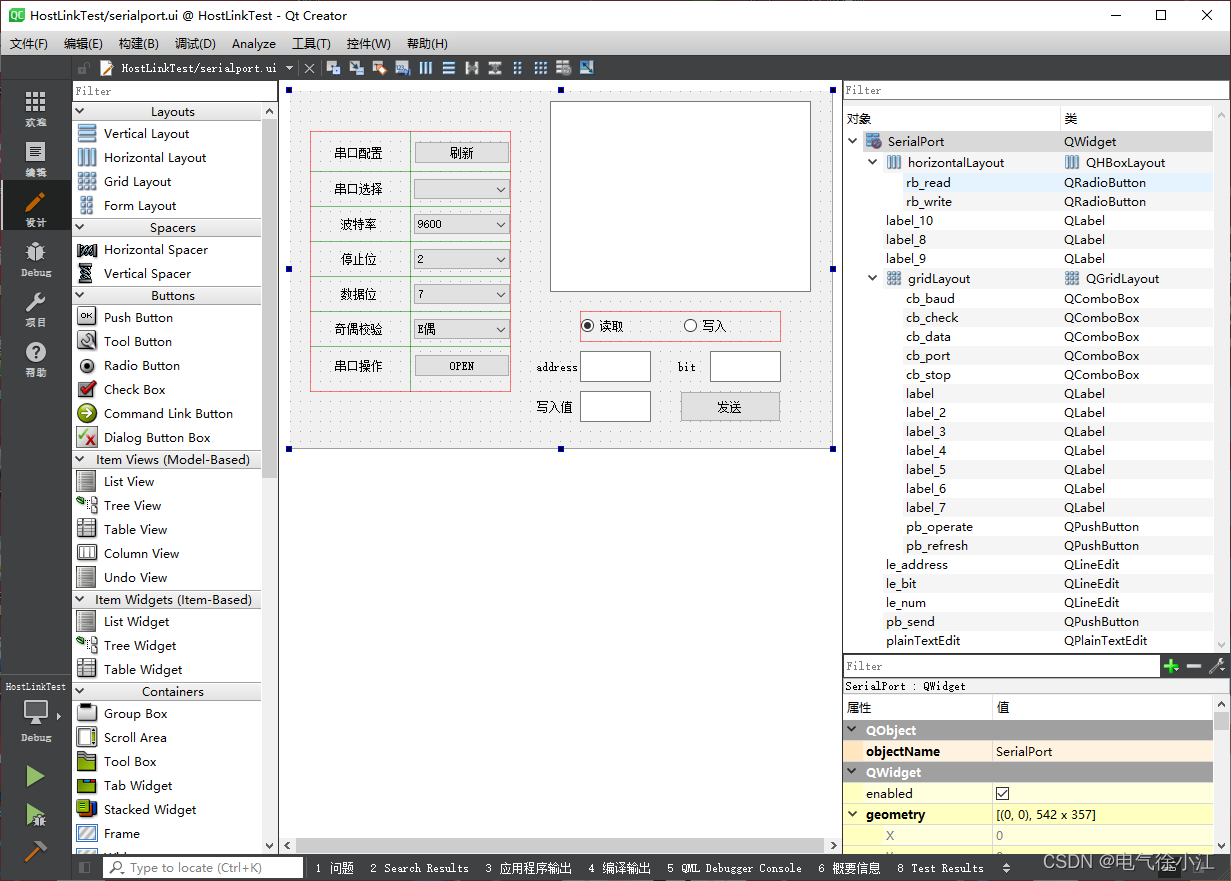

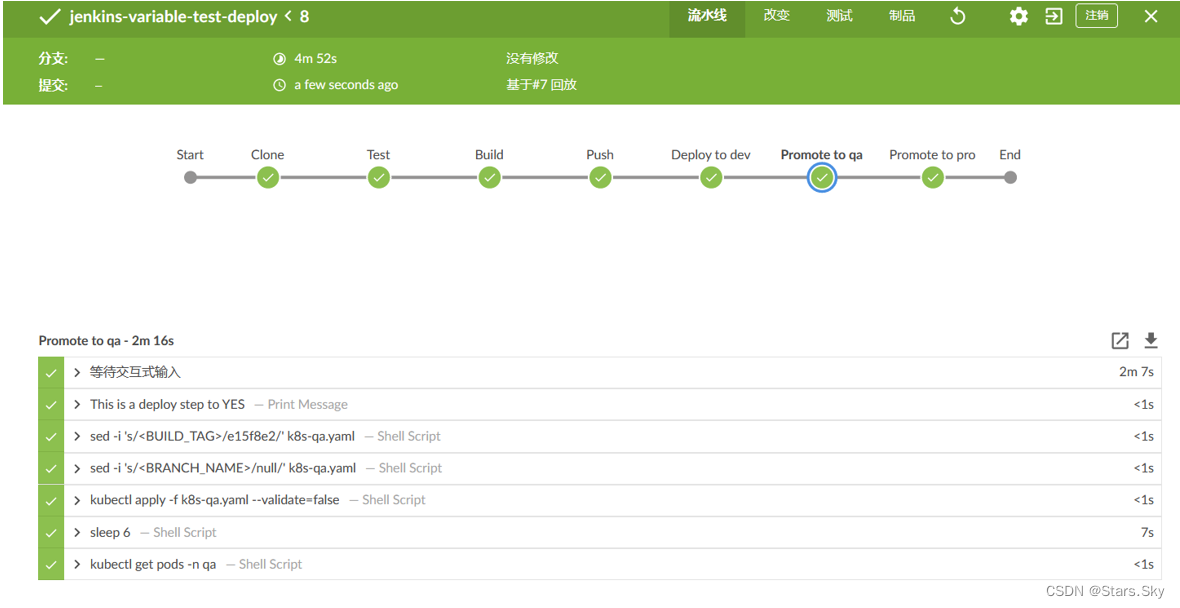

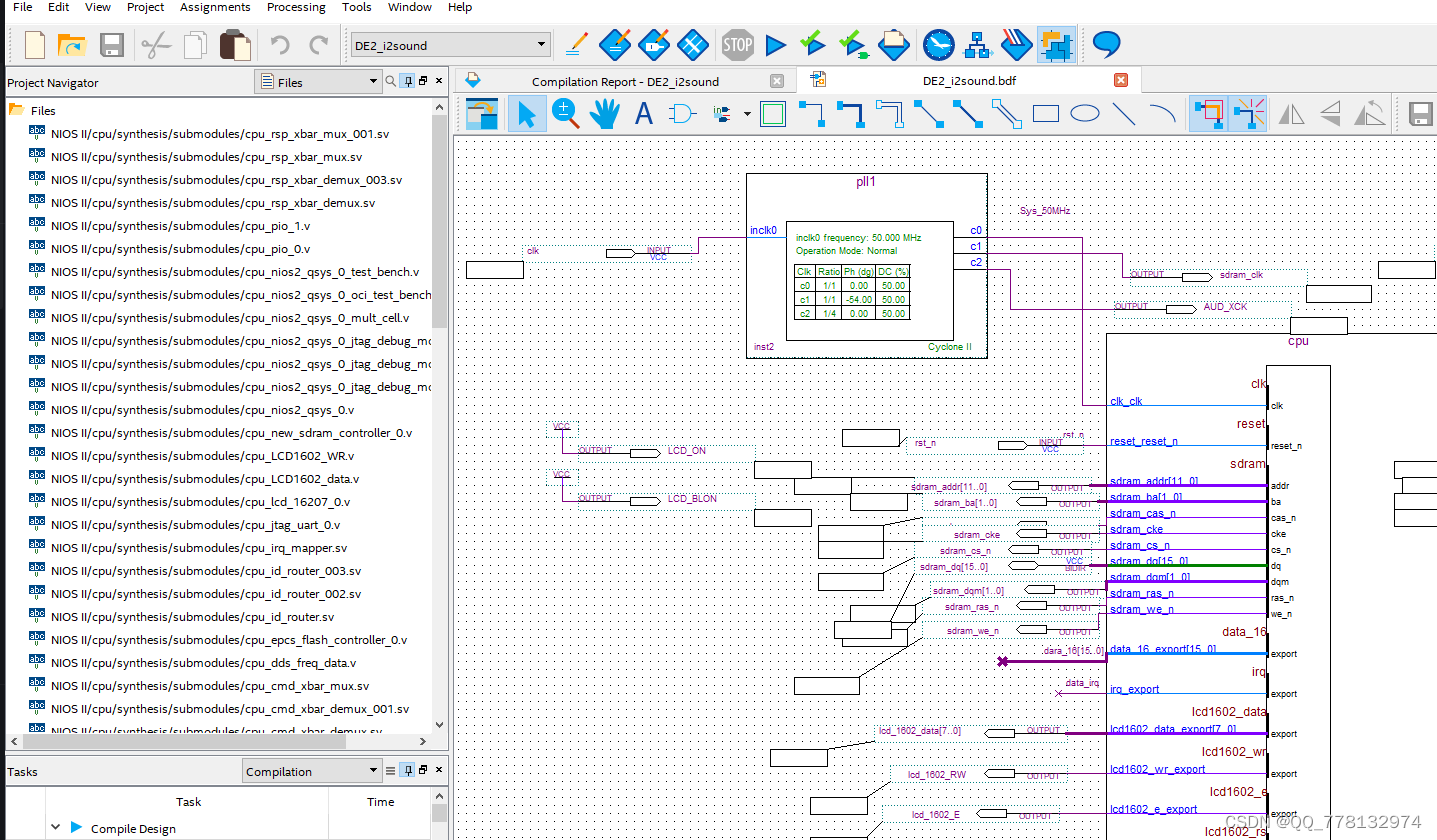

工程截图:

以上各个模块的硬件模型搭建完成之后,将其整合在一