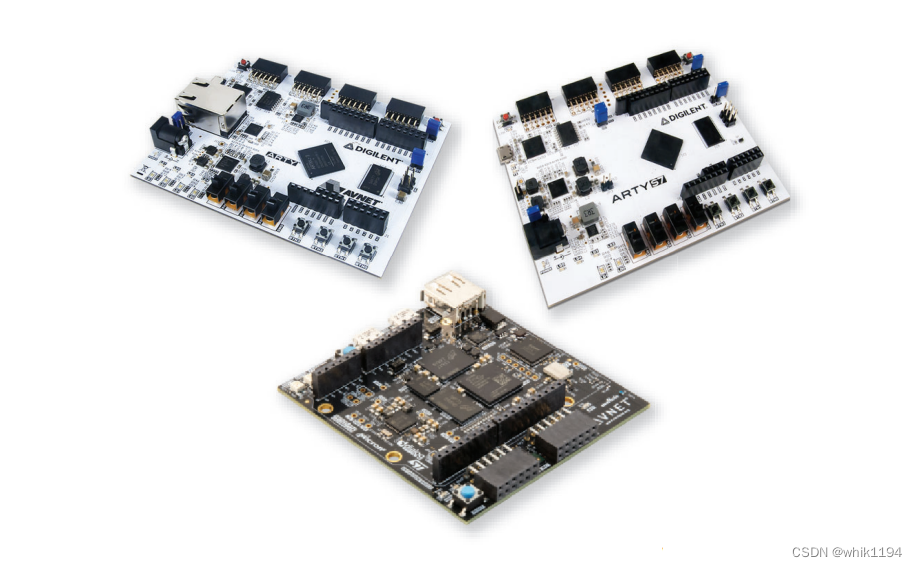

本文是Xilinx MicroBlaze系列教程的第0篇文章。这个系列文章是我个人最近两年使用Xilinx MicroBlaze软核的经验和笔记,以Xilinx ISE 14.7和Spartan-6,以及Vivado 2018.3和Artix-7为例,介绍MicroBlaze软核、AXI系列IP核的软硬件使用,希望能帮助到更多的人。

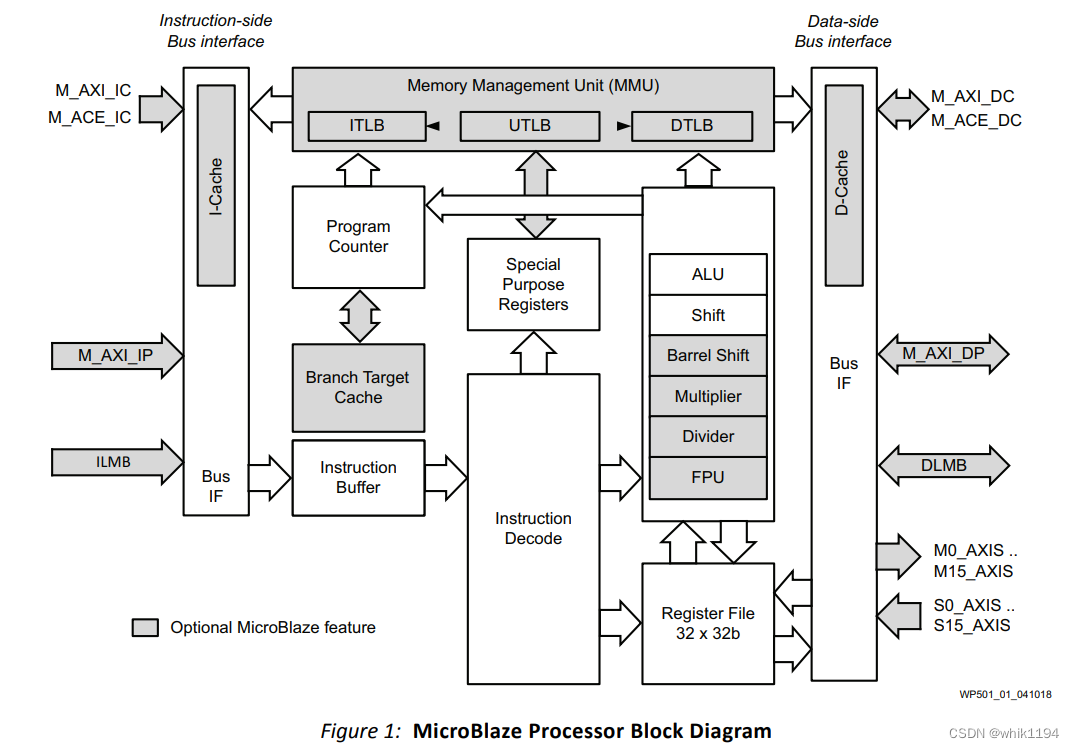

MicroBlaze是Xilinx(现AMD)开发的一款嵌入式RISC软核,可以在FPGA上使用,具有运行速度快,资源占用少,可配置性强的特点。

MicroBlaze的引入可以让一个没有任何FPGA经验的嵌入式工程师,利用ISE/Vivado/Vitis开发套件中的SDK开发工具,来开发软核固件,丰富的AXI接口的IP核,可以满足不同应用的需求,如工业、医疗、汽车、消费类以及通信市场等。支持裸机或运行RTOS操作系统。

MicroBlaze采用RISC架构和哈弗结构,32位指令和地址总线,3级流水线结构,支持响应软件和硬件终端,支持Xilinx 的Spartan、Artix、Kintex、Virtex等系列FPGA产品。

关于FPGA的软核和硬核处理器的区别,可以查看之前的文章: