电源系列文章目录

本系列文章为博主在学习工作过程中的心得记录,欢迎评论区交流讨论。

- BUCK电路工作原理、参数计算及工作模式分析

- BUCK电路布线规则、EMI分析

- 电源电路中肖特基、续流二极管要求

目录

- 电源系列文章目录

- 一、PCB布线规则

- 1、输入电感与肖特基摆放

- 2、输出电容与电感摆放

- 3、反馈电阻及走线布置

- 二、EMI整改对策

- 1、缩短开关电流回路

- 2、降低电流变化率

- 3、抑制高频噪声

- 4、增加RC吸收电容

- 5、增加共模电感

一、PCB布线规则

- 开关电源至今,电路已经相当简洁,仅由芯片、电感、肖特基、电容、电阻等几个器件就能组成功能强大的电路。我们很多工程师在实际应用时或多或少吃过亏,明明按照原厂提供的电路去制作产品,但还是会出现各种各样的问题。通常情况下,多是由于前期绘制 PCB时,没有设计好开关电源布线回路导致,下面对BUCK电路布线设计,EMI整改进行讲解。

1、输入电感与肖特基摆放

- 对于开关电源来说,输入端通常采用电解电容与陶瓷电容组合使用(主要是经济实惠),电容具有储能与滤波作用,电解电容给芯片提供瞬态电流,确保输入端电压不出现较大波动,陶瓷电容用来滤除输入端高频毛刺电压,给芯片内部逻辑电路提供纯净电源。

- 因此在布局过程中,摆放好 IC 的位置后,就应该确定陶瓷电容的位置,使陶瓷电容靠近芯片的 VIN 与GND 引脚;并且注意避免通过过孔进行连接,因为过孔会产生寄生电感,严重影响陶瓷电容滤波效果。

- 对于降压电源来说,输入端电流为不连续电流,根据公式 V = L ∗ d i / d t V=L*di/dt V=L∗di/dt可知,变化的电流会在寄生电感上产生毛刺电压,若处理不好,此毛刺电压会影响系统稳定性,并导致 IC 失效。

- 在使用条件不变的情况下,

d

i

/

d

t

di/dt

di/dt基本不会变化,只好通过降低开关电流回路上的寄生电感来降低此毛刺电压。要降低寄生电感,就要降低电流回路长度,缩短开关电流回路长度的方法是,将输入端电解电容靠近芯片的 VIN 和肖特基的阳极,芯片的 SW 引脚靠近肖特基的阴极,如下图所示。这样最大限度的降低其寄生电感,减少毛刺电压,提高系统稳定性,并可以降低辐射 EMI。

2、输出电容与电感摆放

- 为减少系统回路上噪声和电磁辐射,不仅要减少开关电流回路长度,还要缩短大电流回路,并且大电流走线要采用敷铜处理,敷铜不要有锐角,尽量少打弯,尽量不换层,若走线必须得换层处理,需要适当增加过孔数量,这样可以减少过孔带来的寄生电感。

- 可以将电感靠近芯片 SW,输出电容靠近电感和肖特基阳极,如下图所示。若输出电容位置不当,会导致输出电压不稳。

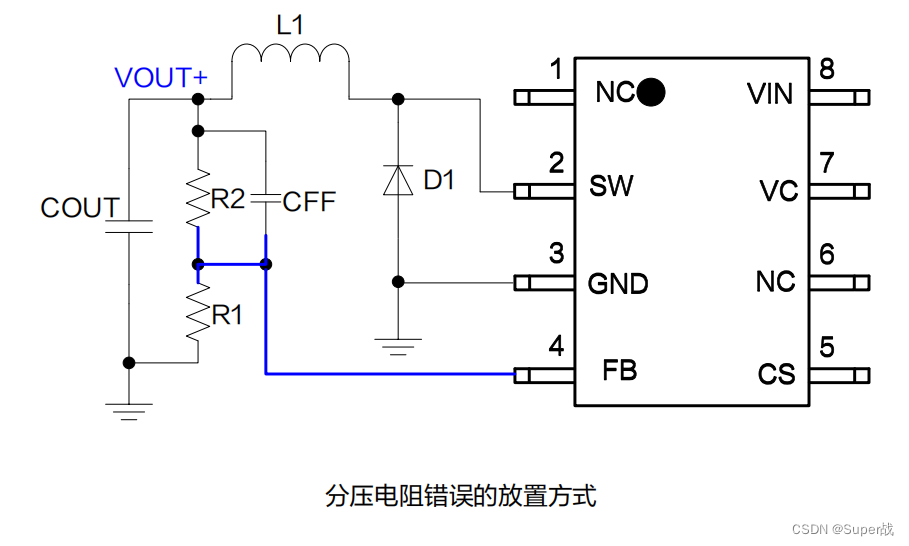

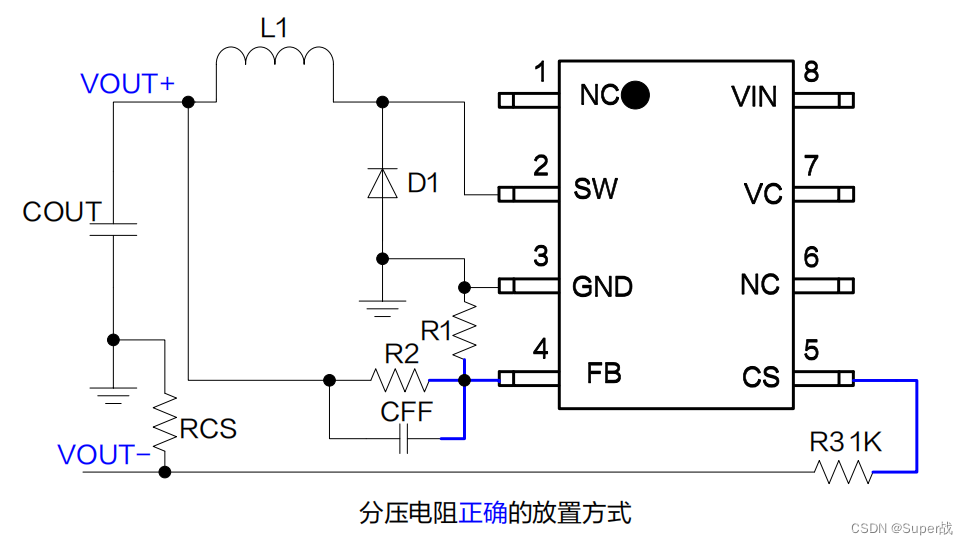

3、反馈电阻及走线布置

- 系统回路中反馈走线也很重要,FB 引脚负责调整,稳定输出电压,CS 引脚负责调整,稳定输出电流,为防止反馈引脚捡取到电路上噪声,应尽可能减小 FB 与 CS 引脚节点布线长度。

- 针对 FB 节点,需要让分压电阻靠近芯片的 FB 与 GND 引脚,针对 CS 节点,可以在靠近芯片 CS 引脚处串联 1K 电阻,滤除干扰;并且反馈走线要远离电感,肖特基,SW等开关节点,同时用 GND 走线包围最佳。

二、EMI整改对策

- 开关电源与 LDO 相比,具有效率高、体积小、可升压等显著优点,但是开关电源在工作时,会对外产生电磁辐射,若辐射过大,则会对周围器件造成严重影响,导致系统不能稳定工作。

- 要实现抑制电源对外的电磁辐射,首先应明确电磁辐射产生的机理与源头。开关电源是通过功率管打开时给电感充电,电感储能;功率管断开时,电感释放能量,实现电压变换。

- 由于功率管、续流二极管不断的打开与关断,造成电流不连续,此变化电流会产生尖峰电压(由

V

=

L

∗

d

i

/

d

t

V=L*di/dt

V=L∗di/dt可以推导出,尖峰电压等于电流回路中的寄生电感乘以电流变化率,L 是开关电流回路的寄生电感),此尖峰电压会产生较大的电磁干扰,可以通过抑制此尖峰电压来降低电磁干扰。

通常可以通过以下几种方法来降低开关电源对外产生的电磁干扰。

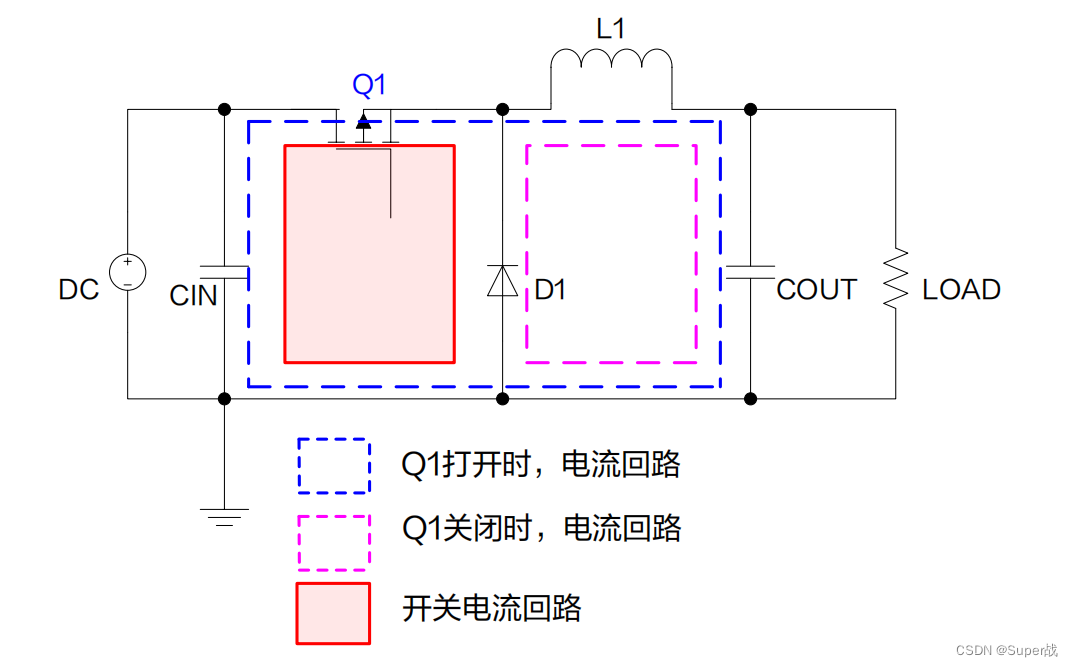

1、缩短开关电流回路

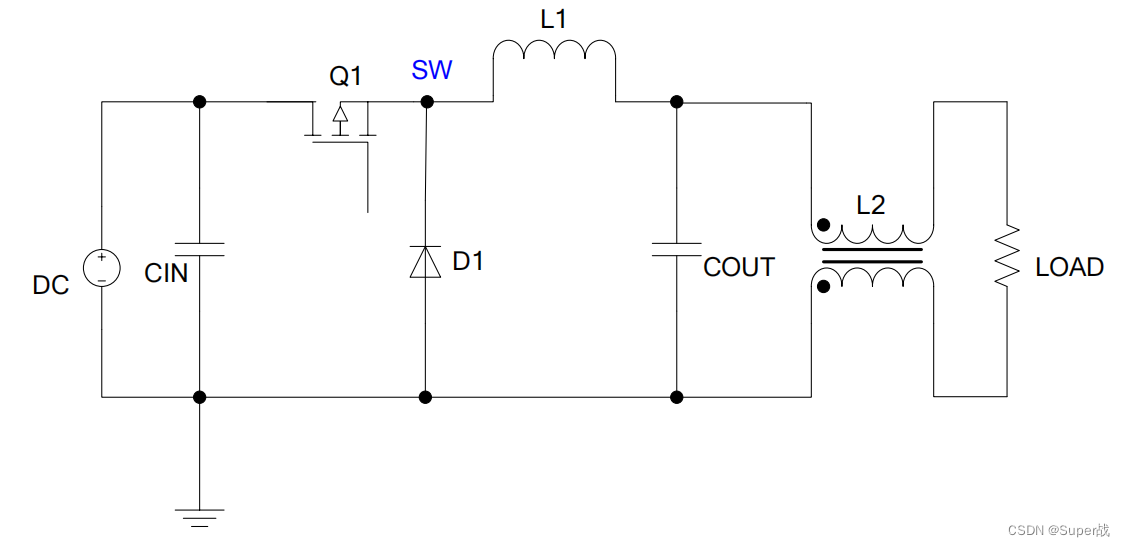

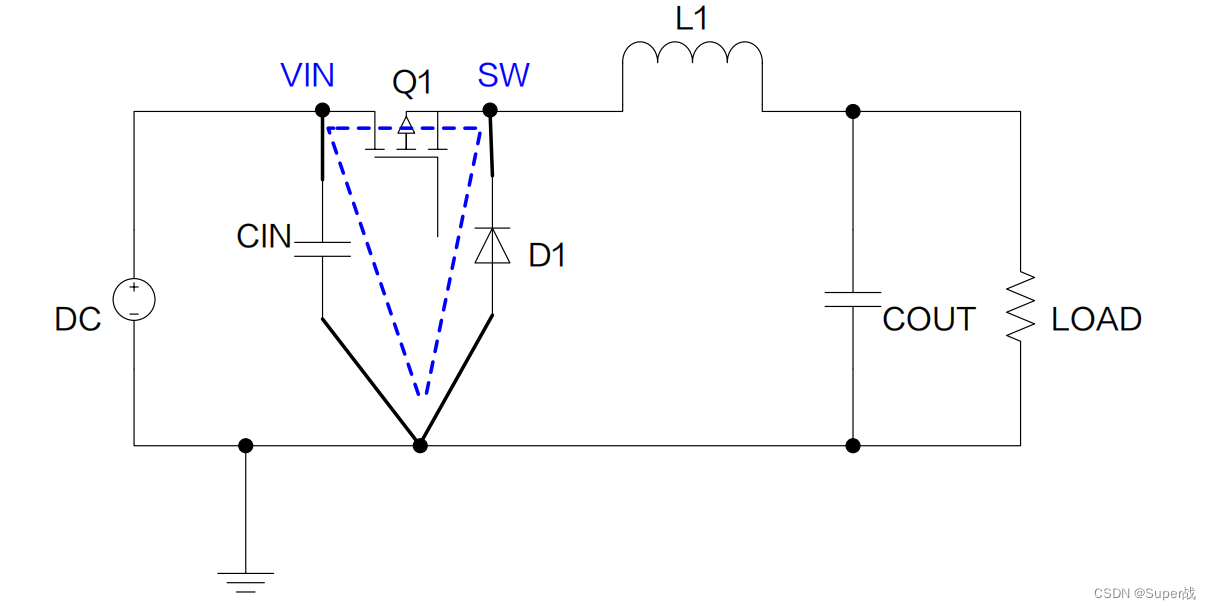

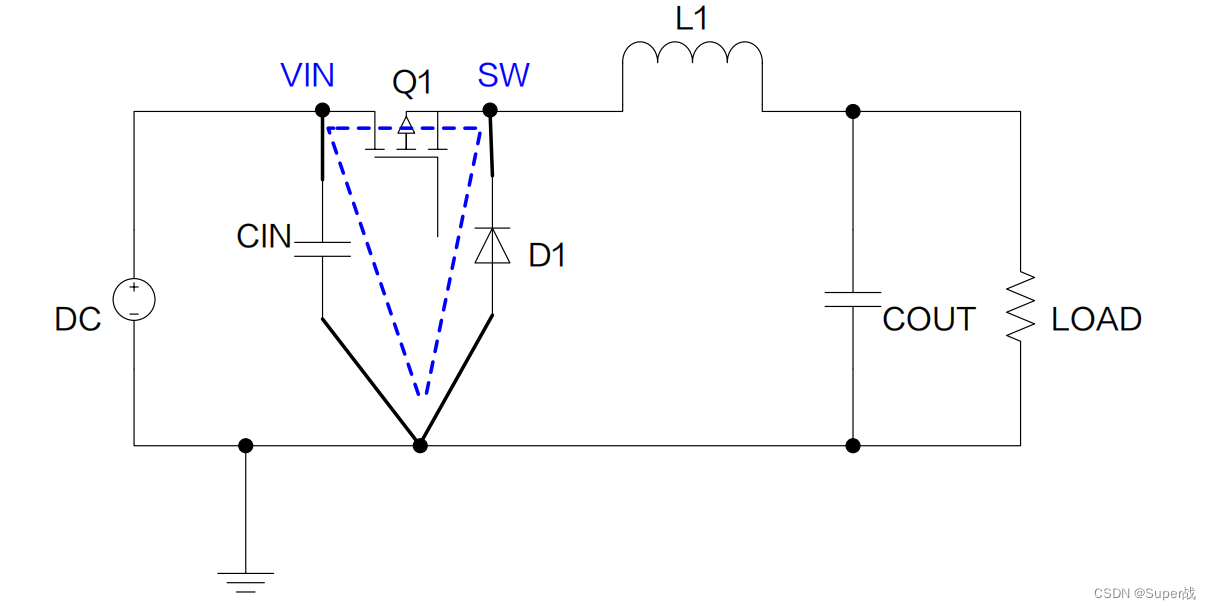

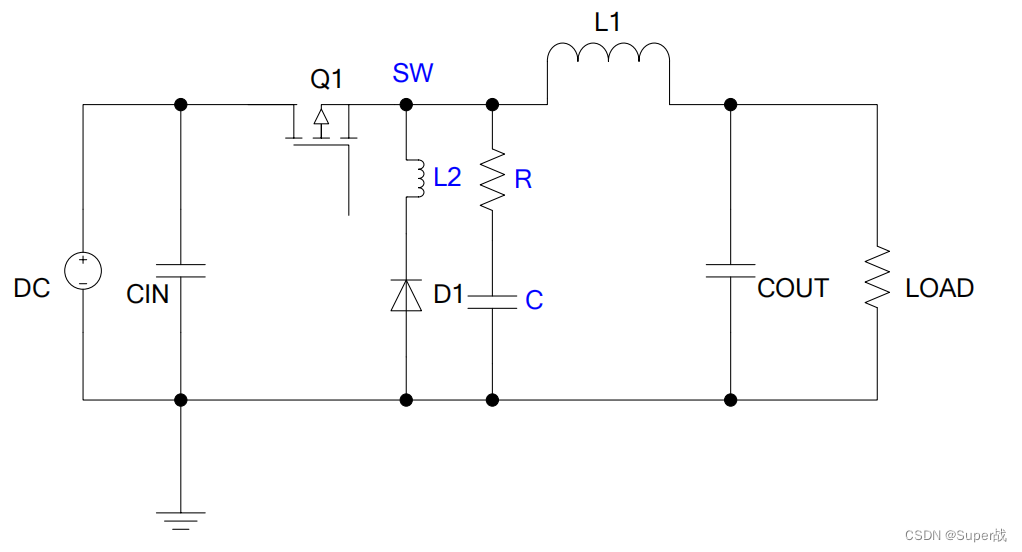

BUCK 拓扑电流回路图,以系统工作在连续状态下为例。

- 由上图可知,当功率管 Q1 打开时,电流回路是 CIN->Q1->L1->COUT;当 Q1 闭合时,电流回路是L1->COUT->D1;不论功率管 Q1 打开还是关断,电流均流过 L1 和 COUT,表明流过L1 和 COUT 处电流是连续电流,流过CIN、Q1、D1的电流是开关电流,开关电流会在寄生电感上产生毛刺电压,对外辐射电磁波。

- 由 V = L ∗ d i / d t V=L*di/dt V=L∗di/dt可知,在 d i / d t di/dt di/dt不变的条件下,可以通过缩短 CIN、Q1、D1 的电流回路,来减少开关电流回路的寄生参数,从而实现降低系统产生的电磁辐射。

2、降低电流变化率

- 降低开关电流变化率(即降低 d i / d t di/dt di/dt的值),首先在使用条件不变的情况下,电流的变化量基本不会变化,只好通过延长电流的变化时间来降低 d i / d t di/dt di/dt的值。

- 可以通过使用开关速度稍慢的二极管来降低 D1 回路电流变化率,但是使用开关速度稍慢的超快恢复二极管,会导致二极管的损耗增大,不仅会影响效率,还会导致二极管温度过高,反向漏电流增大,影响系统稳定性,需要根据工程情况进行适当的取舍。

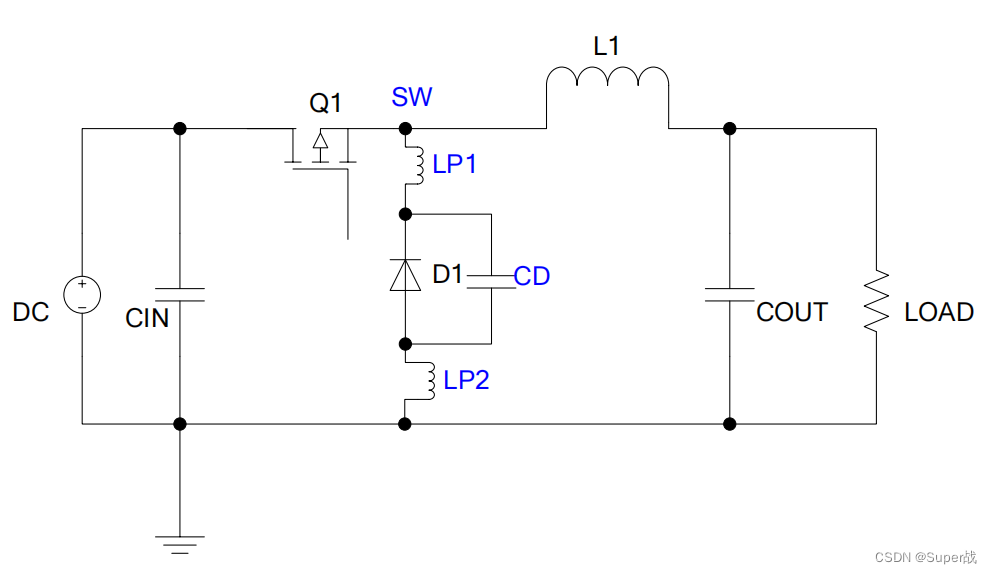

3、抑制高频噪声

- 参考下图,肖特基本身具有寄生电容,回路上还存在寄生电感;开关电流会流过肖特基 D1,寄生的电感、电容会产生振铃,若振荡频率超过 30MHz,进入辐射测试频率段,则会被测试仪器捕捉到。

- 我们可以通过在肖特基处串联磁珠来滤除高频信号,降低高频信号对外电磁辐射能量。但是肖特基上串联磁珠,会产生较大负向尖峰电压,需要控制输入电压与尖峰电压绝对值之和小于芯片的耐压,确保系统稳定性。

- 我们常用的贴片式磁珠材料主要是有磁粉、镍、银浆三大部分组成,其在高频条件下具有相当大的阻抗,可以吸收高频信号(通常 30MHz 以上为高频)。

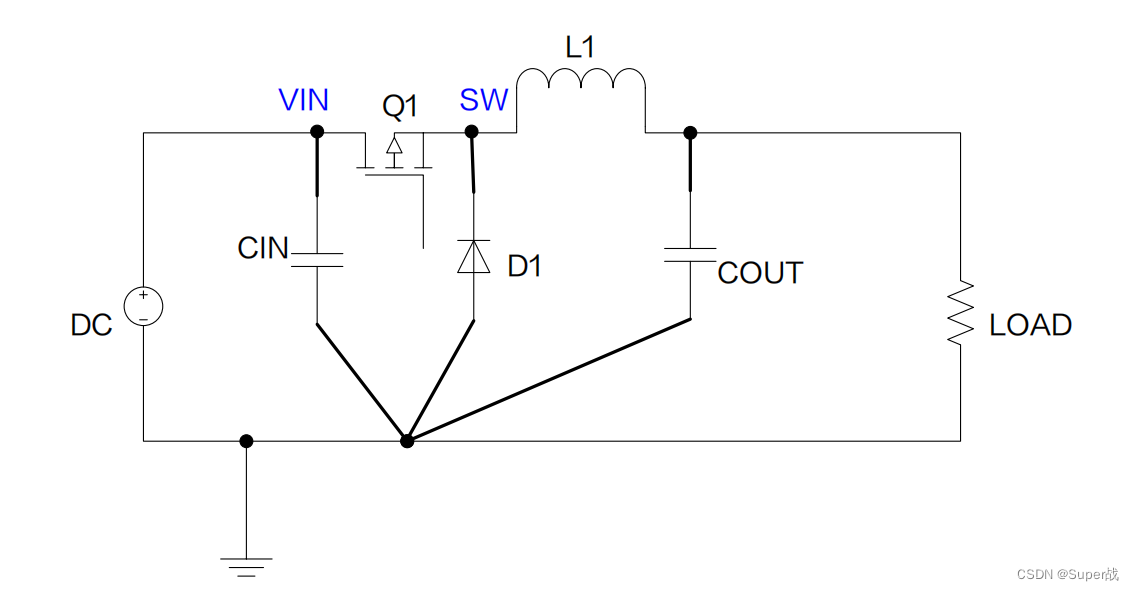

4、增加RC吸收电容

- 在无法进一步降低系统自生的干扰时,可以通过外加器件来进一步抑制;在芯片SW与GND之间并联RC吸收电路不仅可以吸收寄生参数产生的毛刺电压,也可以改变谐振频率,从而实现抑制电磁辐射。

- 通常上述两种方案串磁珠和增加RC吸收电路在组合使用时,抑制效果较佳。相应的电路图如下图所示:

5、增加共模电感

- 辐射测试点频率段一般为30Mhz到1000Mhz,此频率段对应的波长是0.3米到10米,如果要发射一定波长的电磁波,需要一根发射天线,成为天线的必要条件是长度至少要大于波长的二十分之一,当天线是电磁波半波长的整数倍时,发射功率最大。

- 通常输出端的电源线比较长,有可能成为对外发射电磁波的天线,可以通过在系统输出端串联共模电感(如下图所示),滤除共模信号来抑制辐射,但同时共模电感又具有体积大、成本高、不易加工等缺点,不适合应用于小体积、低成本方案,需要根据实际情况来进行取舍。