目录

一:结构描述方式

1.1创建工程

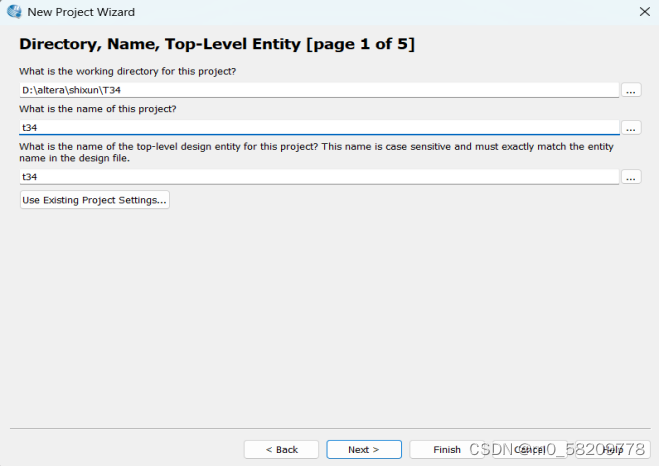

1.1.1点击New Project Wizard,创建t34工程。

1.1.2设置工程路径和名称(t34)

1.2设计门电路

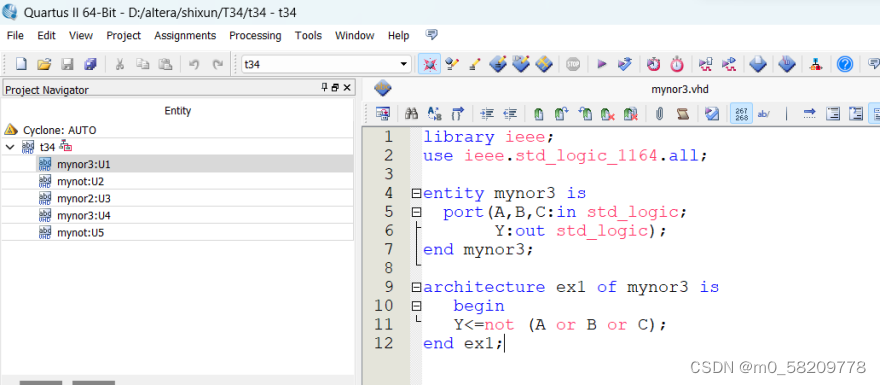

1.2.1设计三输入或非门VHDL程序

1.2.2 设计非门VHDL程序

编辑

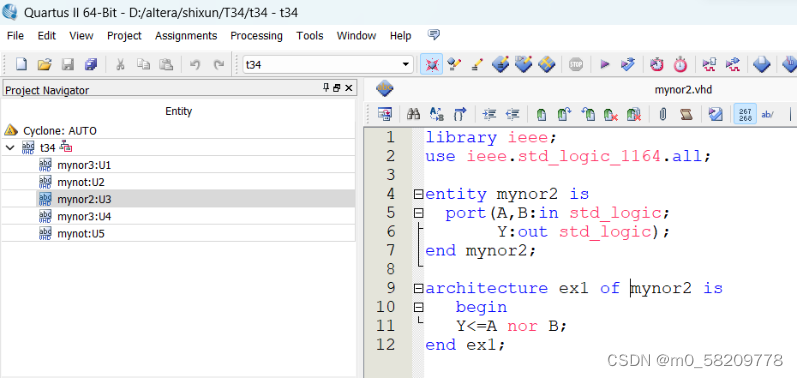

1.2.3 设计二输入或非门VHDL程序

1.3 搭建逻辑电路

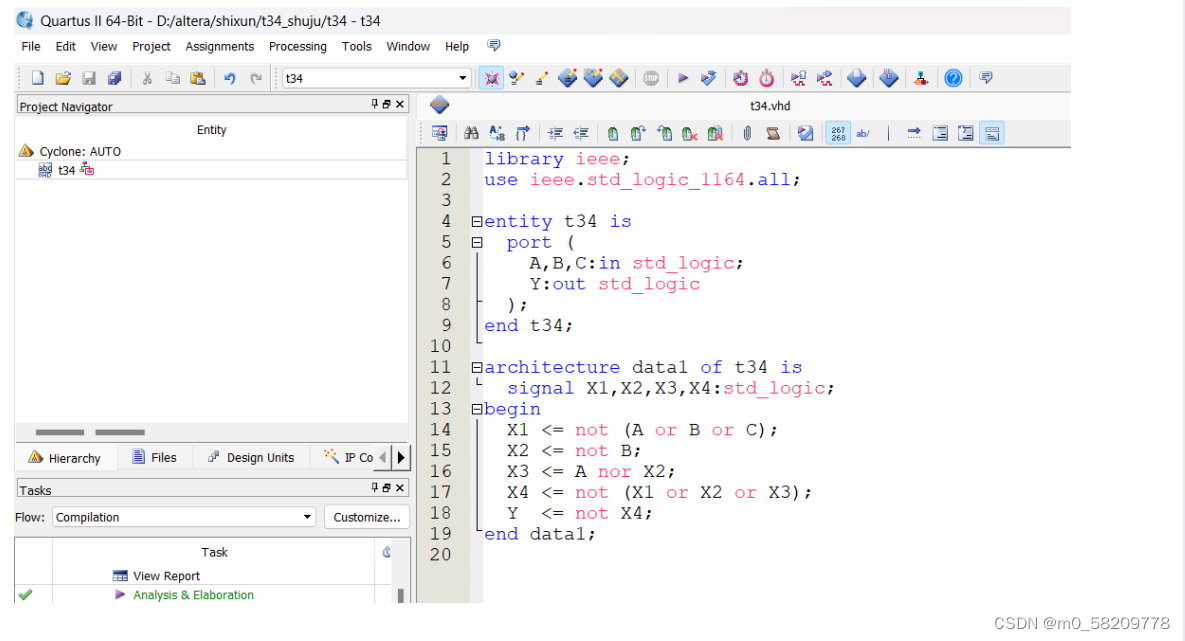

1.4.1设计题3—4电路VHDL程序

编辑

1.4.2.打开New窗口,点击University Program VWF,创建波形图。

1.5设置基本环境

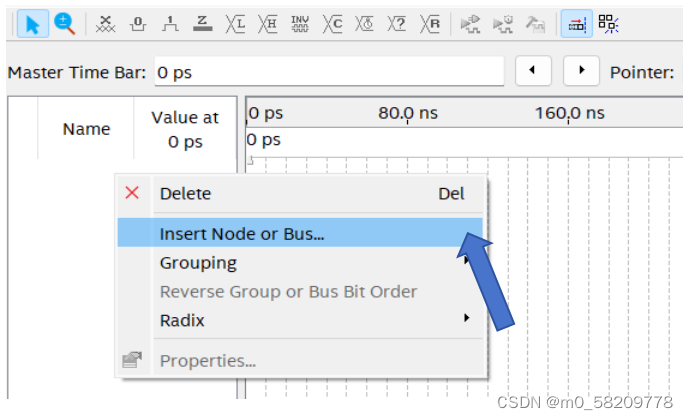

1.5.1在左边空白框单击鼠标右键,进入Insert Node or Bus...页面

编辑

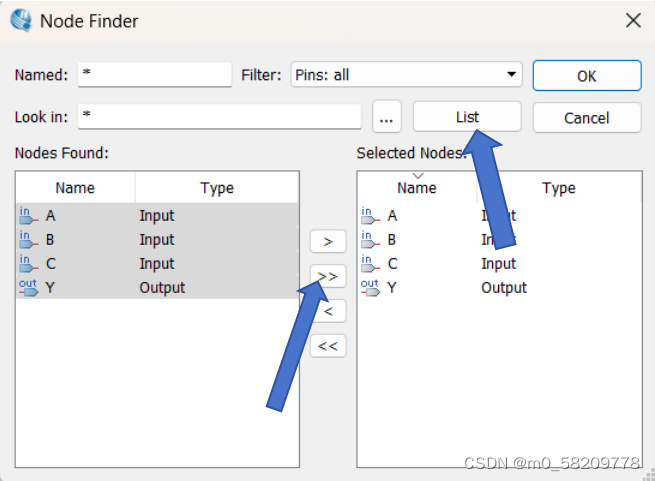

1.5.2.在Node Finder页面,点击List,后点击<<,最后ok。

1.5.3.点击Overwrite Clock,在Period时钟中,A设置为50ns,B设置为100ns,C在Forcing High(1)中后面设置为1。

1.6显示波形图

1.6.1点击Simulation,选中Options,点击Quartus II Simulator,如下所示。

编辑

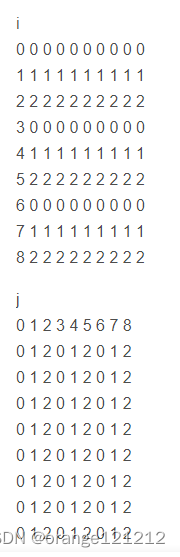

1.6.2.点击Run Functional Simulation,保存该VWF工程为t34,并且输出波形图,如下所示。

二:数据流描述方式

2.1设计题3—4的VHDL程序

2.2 设置基本环境,同1.5。

2.3 显示波形图,同1.6。

编辑

总结

一:结构描述方式

1.1创建工程

1.1.1点击New Project Wizard,创建t34工程。

1.1.2设置工程路径和名称(t34)

1.2设计门电路

1.2.1设计三输入或非门VHDL程序

1.2.2 设计非门VHDL程序

1.2.3 设计二输入或非门VHDL程序

1.3 搭建逻辑电路

| 输入A | 输入B | 输出C | 输出Y |

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 0 |

题3—4真值表如上图所示

逻辑表达式: Y=(((A+B+C)’+(A+B’)+B’)’)’=B’+A’B

1.4设计图3—4的VHDL程序

1.4.1设计题3—4电路VHDL程序

1.4.2.打开New窗口,点击University Program VWF,创建波形图。

1.5设置基本环境

1.5.1在左边空白框单击鼠标右键,进入Insert Node or Bus...页面

1.5.2.在Node Finder页面,点击List,后点击<<,最后ok。

1.5.3.点击Overwrite Clock,在Period时钟中,A设置为50ns,B设置为100ns,C在Forcing High(1)中后面设置为1。

1.6显示波形图

1.6.1点击Simulation,选中Options,点击Quartus II Simulator,如下所示。

1.6.2.点击Run Functional Simulation,保存该VWF工程为t34,并且输出波形图,如下所示。

二:数据流描述方式

2.1设计题3—4的VHDL程序

2.2 设置基本环境,同1.5。

2.3 显示波形图,同1.6。

注:结构描述方式和数据流描述方式的波形图显示一样,结果正确。

总结

在本次实验中,我们对一个简单的电路进行了结构描述和数据流描述,并使用VHDL语言编写了相应的代码。首先,我们使用结构描述方法,将电路分解为几个组件,并将这些组件连接起来以构建整个电路。然后,我们使用数据流描述方法,通过逻辑运算来描述信号之间的关系,而不需要显式地声明组件和连接。

通过这两种描述方法,我们成功地实现了同一个电路的功能,并得到了相同的输出结果。这展示了VHDL语言的灵活性,使得我们能够以不同的方式描述同一电路,并且可以根据需求选择最合适的描述方法。

这次实验让我们对VHDL语言有了更深入的了解,加强了我们对数字电路设计的理解。通过编写和仿真代码,我们能够直观地了解电路的行为,并对数字逻辑设计中的重要概念有了更深层次的理解

致谢

我要特别感谢我的``老师对我们实验的耐心指导和悉心帮助,没有老师的指导和支持,我们无法顺利完成本次实验。同时,我也要感谢实验室的同学们在实验过程中的合作和支持,大家共同努力才取得了这样的成果。最后,我也要感谢Quartus软件提供了强大的功能,为我的实验提供了便利和支持。

![【YOLOv10改进[注意力]】使用注意力MLCA改进C2f + 含全部代码和详细修改方式 + 手撕结构图](https://img-blog.csdnimg.cn/direct/72fdccaa605c4bb88d16bd92bde4bee4.png)