摘 要:

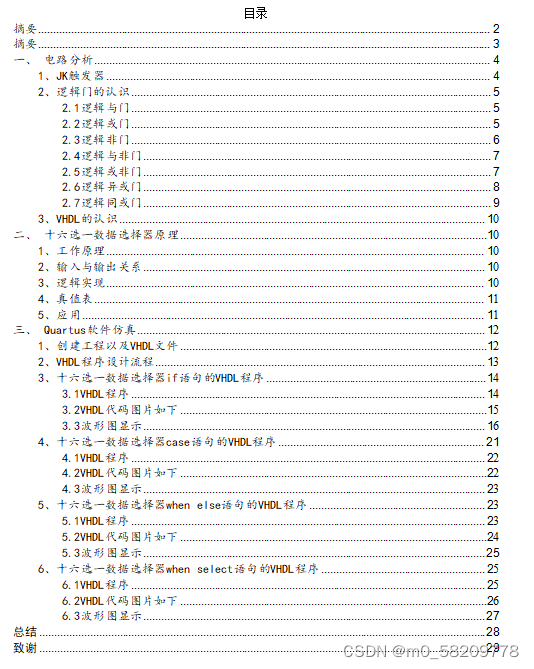

本实验通过Quartus软件完成对十六选一数据选择器的四种VHDL程序,分别为if;case;when else;when select四种方式,实现波形图的生成。同时,加深对VHDL语言的理解和使用多种方式完成任务的能力,提高实验操作能力。

关键词:Quartus;VHDL

引言

随着数字电路技术的迅猛进步,VHDL已成为硬件描述语言中的关键利器。利用VHDL,工程师能够精准地描绘电路逻辑,并通过仿真工具验证设计的准确性,进而生成对应的波形图。在本文中,我们将依据十六选一数据选择器的原理,采用Quartus软件编写四种VHDL代码,以直观地展示并生成所需的波形图,这样的工作流程使得电路设计、验证与仿真更加高效、精确。

一、电路分析

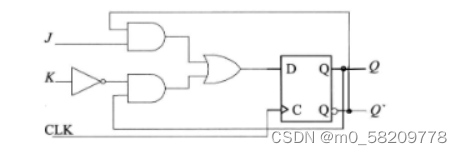

1、JK触发器

1.1电路结构

1.2 图形符号

1.3 真值表

1.4 逻辑表达式

![]()

1.5 边沿JK触发器的特点

1、CLK的上升沿或下降沿触发。

2、抗干扰能力极强,工作速度很高,在触发沿瞬间,按 Q*=J`Q+`KQ的规定更新状态。

3、功能齐全,有保持、置0、置1、翻转功能,使用方便。

2、逻辑门的认识

2.1、逻辑与门(AND):

2.1.1 图形符号:

2.1.2 逻辑符号

2.1.3 真值表:

| 输入 | 输出 | |

| A | B | Y |

| 0 | 0 | 0 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

2.1.4 逻辑表达式:

Y=AB

2.1.5 两输入与门的功能:

与门是实现逻辑“乘”运算的电路,有两个以上输入端,一个输出端(一般电路都只有一个输出端,ECL电路则有二个输出端)。只有当所有输入端都是高电平(逻辑“1”)时,该电路输出才是高电平(逻辑“1”),否则输出为低电平(逻辑“0”)。

2.2、逻辑或门(OR):

2.2.1 图形符号:

2.2.2 逻辑符号:

2.2.3 真值表:

| 输入 | 输出 | |

| A | B | Y |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 1 |

2.2.4 逻辑表达式:

Y=A+B

2.2.5 两输入或门功能:

或门是实现逻辑加的电路,又称逻辑和电路,简称或门。此电路有两个以上输入端,一个输出端。只要有一个或几个输入端是 “1”,或门的输出即为 “1”。而只有所有输入端为 “0”时,输出才为 “0”。

2.3 逻辑非门(NOT):

2.3.1 图形符号:

2.3.2 逻辑符号:

2.3.3 真值表:

| 输入 | 输出 |

| A | Y |

| 0 | 0 |

| 1 | 1 |

2.3.4 逻辑表达式:

2.3.5 非门功能:

实现逻辑代数非的功能,即输出始终和输入保持相反。当输入端为高电平(逻辑“1”)时,输出端为低电平(逻辑“0”);反之,当输入端为低电平(逻辑“0”)时,输出端则为高电平(逻辑“1”)

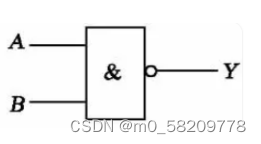

2.4 逻辑与非门(NAND):

2.4.1 图形符号:

2.4.2 逻辑符号:

2.4.3 真值表:

| 输入 | 输出 | |

| A | B | Y |

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

2.4.4 逻辑表达式:

2.4.5 两输入与非门功能:

与非门则是当输入端中有1个或1个以上是低电平时,输出为高电平;只有所有输入是高电平时,输出才是低电平。

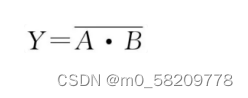

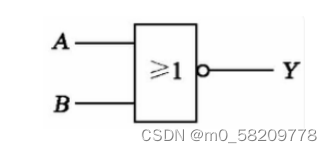

2.5 逻辑或非门(NOR):

2.5.1 图形符号:

2.5.2 逻辑符号:

2.5.3 真值表:

| 输入 | 输出 | |

| A | B | Y |

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

2.5.4 逻辑表达式:

2.5.5 两输入或非门的功能:

或非门是具有多端输入和单端输出的门电路。当任一输入端(或多端)为高电平(逻辑“1”)时,输出就是低电平(逻辑“0”);只有当所有输入端都是低电平(逻辑“0”)时,输出才是高电平(逻辑“1”)。

2.6 逻辑异或门(XOR)

2.6.1 图形符号:

2.6.2 逻辑符号:

2.6.3 真值表:

| 输入 | 输出 | |

| A | B | F |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

2.6.4 逻辑表达式:

2.6.5 两输入异或门的功能:

当输入信号中有一个为高电平,另一个为低电平时,输出信号为高电平。如果两个输入信号相同(均为高电平或均为低电平),则输出信号为低电平。

2.7、逻辑同或门(XNOR):

2.7.1 图形符号:

2.7.2 逻辑符号

2.7.3 真值表:

| 输入 | 输出 | |

| A | B | F |

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

2.7.4 逻辑表达式:

2.7.5 两输入同或门的功能:

当输入信号相同时(均为高电平或均为低电平),输出信号为高电平。如果输入信号不同,则输出信号为低电平。

在数字逻辑的世界里,基础逻辑门作为构建块,通过相互串联、并联以及引入反馈机制,可以编织出更为错综复杂的逻辑网络。这些逻辑门不仅是计算机硬件、电子系统以及各类数字电子设备的基石,更是它们实现数据处理、存储和传输等关键功能的核心所在。

简而言之,逻辑门是构建复杂逻辑功能的基石,它们通过不同的组合方式,在电子系统中发挥着数据处理、存储和传输的不可或缺的作用。

3、VHDL的认识

VHDL语言是一种用于电路设计的高级语言。它在80年代的后期出现。最初是由美国国防部开发出来供美军用来提高设计的可靠性和缩减开发周期的一种使用范围较小的设计语言 。

VHDL翻译成中文就是超高速集成电路硬件描述语言,主要是应用在数字电路的设计中。它在中国的应用多数是用在FPGA/CPLD/EPLD的设计中。当然在一些实力较为雄厚的单位,它也被用来设计ASIC。

VHDL主要用于描述数字系统的结构,行为,功能和接口。除了含有许多具有硬件特征的语句外,VHDL的语言形式、描述风格以及语法是十分类似于一般的计算机高级语言。VHDL的程序结构特点是将一项工程设计,或称设计实体(可以是一个元件,一个电路模块或一个系统)分成外部(或称可视部分,及端口)和内部(或称不可视部分),既涉及实体的内部功能和算法完成部分。在对一个设计实体定义了外部界面后,一旦其内部开发完成后,其他的设计就可以直接调用这个实体。这种将设计实体分成内外部分的概念是VHDL系统设计的基本点。

二、十六选一数据选择器原理

1.工作原理

16:1数据选择器有16个输入信号线(通常标记为a0,a1....a15)、4个选择信号线(标记为S0,S1,S2,S3)和1个输出信号线(标记为Y)。选择信号用来确定哪个输入信号会被传输到输出。

2.输入与输出关系

输出信号Y由选择信号决定。选择信号表示的二进制数确定了输出信号所连接的输入信号。例如:

(1)当S3S2S1S0=0000时,Y=a0

(2)当S3S2S1S0=0001时,Y=a1

(3)当S3S2S1S0=0010时,Y=a2

(4)依此类推,直到S3S2S1S0=1111时,Y=a15

3.逻辑实现

实现16:1多路复用器的方法之一是使用逻辑门。每个输入信号与一组与选择信号相应的组合逻辑进行“与”运算,然后所有的这些“与”运算的结果通过一个“或”门进行汇总。具体来说:

(1)与门阵列:每个输入Ii都连接到一组与门,与门的另一端连接的是选择信号的某种组合。例如,输入I0需要通过4个选择信号S3,S2,S1,S0的否定来选择(即S3′⋅S2′⋅′S1′⋅S0′)。

(2)或门:所有与门的输出连接到一个或门,或门的输出就是选择器的输出 Y。

4.真值表

| S3 | S2 | S1 | S0 | Y |

| 0 | 0 | 0 | 0 | a0 |

| 0 | 0 | 0 | 1 | a1 |

| 0 | 0 | 1 | 0 | a2 |

| 0 | 0 | 1 | 1 | a3 |

| 0 | 1 | 0 | 0 | a4 |

| 0 | 1 | 0 | 1 | a5 |

| 0 | 1 | 1 | 0 | a6 |

| 0 | 1 | 1 | 1 | a7 |

| 1 | 0 | 0 | 0 | a8 |

| 1 | 0 | 0 | 1 | a9 |

| 1 | 0 | 1 | 0 | a10 |

| 1 | 0 | 1 | 1 | a11 |

| 1 | 1 | 0 | 0 | a12 |

| 1 | 1 | 0 | 1 | a13 |

| 1 | 1 | 1 | 0 | a14 |

| 1 | 1 | 1 | 1 | a15 |

5.应用

16:1选择器在多种应用中使用,包括数据路由、信号选择、时分复用等。在计算机系统中,它可以用来选择来自不同寄存器或存储单元的数据,在通信系统中,它可以用来选择不同信号源的信号进行传输。

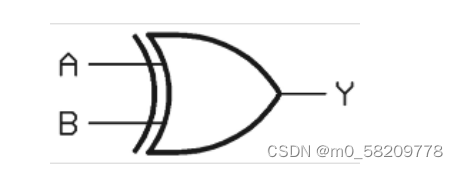

三、Quartus软件仿真

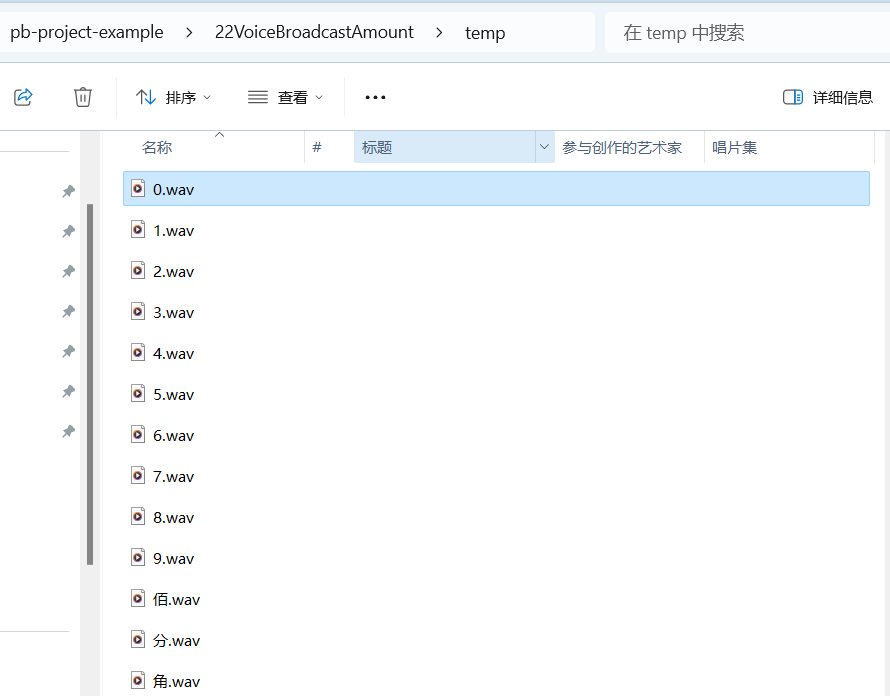

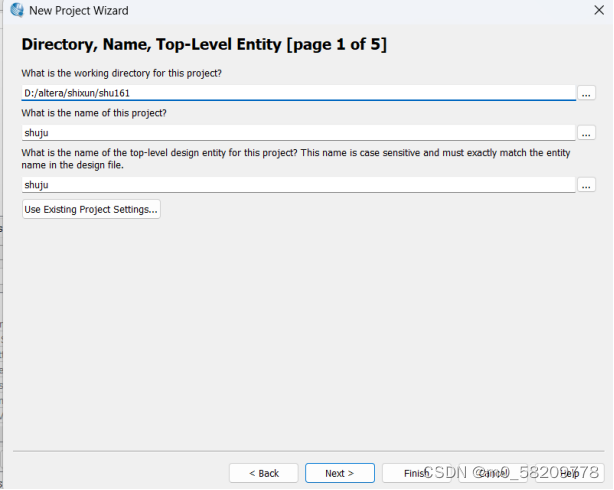

1.创建工程以及VHDL文件

1.1①选中保存的路径,②定义该工程的名称,③点击Next

1.2①选择Cyclone,②点击Next

1.3①点击New,②选中VHDL File,③点击OK,第一步就初步完成。

2.VHDL程序设计流程

VHDL(VHSIC Hardware Description Language)是一种文本化的硬件描述语言,它允许工程师精确地定义数字系统的结构和行为。在Quartus软件中,使用VHDL的数据流描述方法来进行数字系统设计,通常遵循以下步骤:

2.1. 定义实体(Entity):

(1)在VHDL代码中明确指定数字系统的接口。

(2)包括所有输入输出端口的数据类型、位宽和方向。

2.2. 架构化设计(Architecture):

(1)详细描述系统内部的工作机制和逻辑。

(2)定义数据如何在各个组件之间流动和处理。

2.3. 构建层次结构:

(1)将定义的实体和架构组合起来,形成一个完整的系统模型。

(2)通过VHDL的层次化描述,实现复杂系统的模块化设计。

通过这种VHDL描述方式,工程师可以在Quartus软件中高效地创建、模拟和验证数字系统,确保设计的正确性和可靠性。

3.十六选一数据选择器if语句的VHDL程序

3.1VHDL程序

| VHDL程序命令与解释(十六选一数据选择器) |

| library ieee;//导入IEEE库,这个库包含了标准逻辑类型和子程序 use ieee.std_logic_1164.all;//使用IEEE库中的std_logic_1164包,它定义了std_logic类型及其相关类型 library ieee;-- 引入IEEE标准库。标准库中包含各种常用的数据类型和函数。 use ieee.std_logic_1164.all;-- 使用IEEE标准库中的 std_logic_1164 包,该包定义了std_logic和std_logic_vector等数据类型。 entity shuju is-- 定义一个名为 shuju 的实体,这是 VHDL 模块的声明部分。 port(a:in std_logic_vector(15 downto 0);-- 定义一个输入端口 a,它是一个16位的标准逻辑向量(std_logic_vector),输入信号。 s:in std_logic_vector(3 downto 0);-- 定义一个输入端口 s,它是一个4位的标准逻辑向量,选择信号。 y:out std_logic-- 定义一个输出端口 y,它是一个标准逻辑信号,输出信号。 ); end;-- 结束实体声明部分。 architecture a1 of shuju is-- 定义名为 a1 的架构,它描述了实体 shuju 的具体实现 begin-- 开始架构体的定义。 process(a,s)-- 定义一个过程块 process,这个过程块在输入信号 a 或 s 发生变化时触发。 begin -- 过程块的开始。 if s="0000" then-- 如果选择信号 s 的值为 "0000" ,则执行以下语句。 y<=a(0);-- 输出信号 y 赋值为输入向量 a 的第0位。 elsif s="0001" then-- 如果选择信号 s 的值为 "0001" ,则执行以下语句。 y<=a(1);-- 输出信号 y 赋值为输入向量 a 的第1位。 elsif s="0010" then -- 如果选择信号 s 的值为 "0010" ,则执行以下语句。 y<=a(2);-- 输出信号 y 赋值为输入向量 a 的第2位。 elsif s="0011" then-- 如果选择信号 s 的值为 "0011" ,则执行以下语句。 y<=a(3);-- 输出信号 y 赋值为输入向量 a 的第3位。 elsif s="0100" then-- 如果选择信号 s 的值为 "0100" ,则执行以下语句。 y<=a(4);-- 输出信号 y 赋值为输入向量 a 的第4位。 elsif s="0101" then-- 如果选择信号 s 的值为 "0101" ,则执行以下语句。 y<=a(5);-- 输出信号 y 赋值为输入向量 a 的第5位。 elsif s="0110" then -- 如果选择信号 s 的值为 "0110" ,则执行以下语句。 y<=a(6);-- 输出信号 y 赋值为输入向量 a 的第6位。 elsif s="0111" then -- 如果选择信号 s 的值为 "0111" ,则执行以下语句。 y<=a(7); -- 输出信号 y 赋值为输入向量 a 的第7位。 elsif s="1000" then-- 如果选择信号 s 的值为 "1000" ,则执行以下语句。 y<=a(8);-- 输出信号 y 赋值为输入向量 a 的第8位。 elsif s="1001" then-- 如果选择信号 s 的值为 "1001" ,则执行以下语句。 y<=a(9); -- 输出信号 y 赋值为输入向量 a 的第9位。 elsif s="1010" then-- 如果选择信号 s 的值为 "1010" ,则执行以下语句。 y<=a(10);-- 输出信号 y 赋值为输入向量 a 的第10位。 elsif s="1011" then-- 如果选择信号 s 的值为 "1011" ,则执行以下语句。 y<=a(11); -- 输出信号 y 赋值为输入向量 a 的第11位。 elsif s="1100" then -- 如果选择信号 s 的值为 "1100" ,则执行以下语句。 y<=a(12); -- 输出信号 y 赋值为输入向量 a 的第12位。 elsif s="1101" then -- 如果选择信号 s 的值为 "1101" ,则执行以下语句。 y<=a(13); -- 输出信号 y 赋值为输入向量 a 的第13位。 elsif s="1110" then-- 如果选择信号 s 的值为 "1110" ,则执行以下语句。 y<=a(14);-- 输出信号 y 赋值为输入向量 a 的第14位。 elsif s="1111" then-- 如果选择信号 s 的值为 "1111" ,则执行以下语句。 y<=a(15);-- 输出信号 y 赋值为输入向量 a 的第15 else y<='X'; --如果选择信号 s 的值不在上述范围内,则输出信号 y 赋值为未知状态X end if; -- 结束 if 语句。 end process; -- 结束过程块。 end a1; -- 结束架构体定义 |

3.2 VHDL代码图片如下:

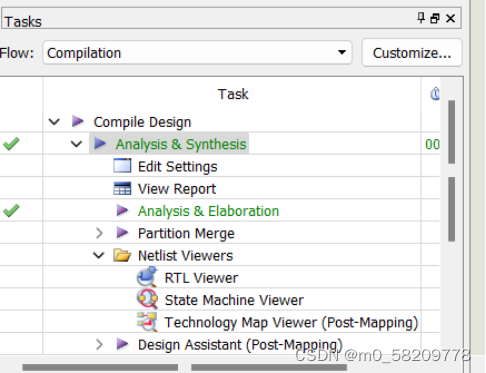

该代码运行后,无误则显示以下界面:

3.3波形图显示

3.3.1 创建VWF文件,①点击New,②点击University Program VWF,③点击OK。

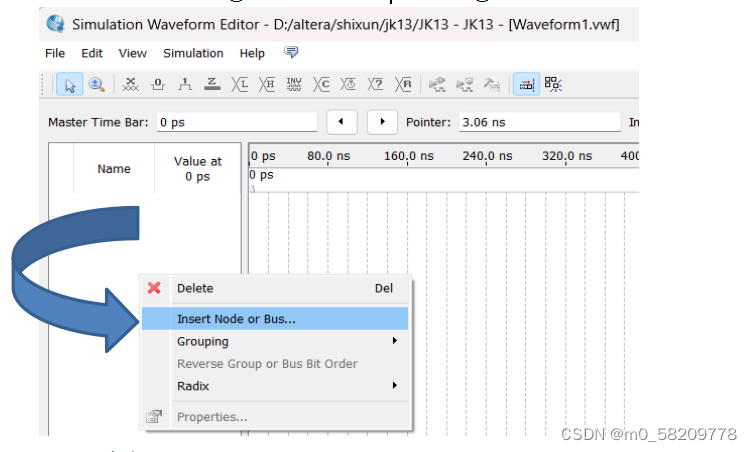

3.3.2 节点查找器,①在左侧空白处鼠标右击,②点击Insert Node or Bus...。

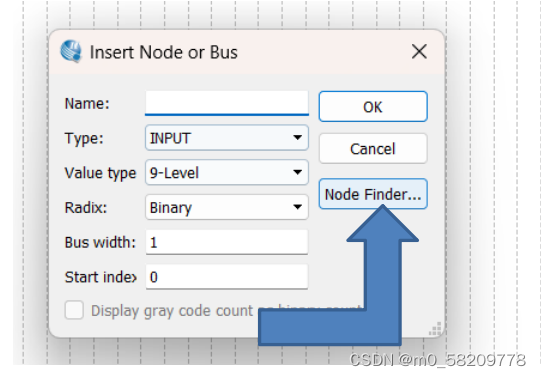

3.3.3 点击Node Finder...。

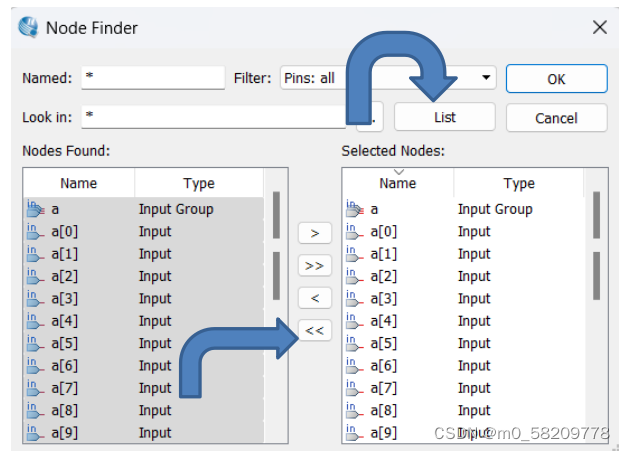

3.3.4 ①点击List,②点击<<,③点击OK

3.3.5 将s设为10进制显示,①右击s,②点击Radix,③点击Unsigned Decimal。

3.3.6 将s的Count Value的Count every改成10.0ns。

3.3.7 将a的16个输入信号改成不同的状态,部分改时钟,部分置1,部分置0,以分辨y因为s的十进制的每一刻状态的显示。

3.3.8 在Simulation中点击Options,选中Quartus II Simulator。

3.3.9 选中Run Functional Simulation

3.3.10 选择保存路径,并且定义名称为shuju1.

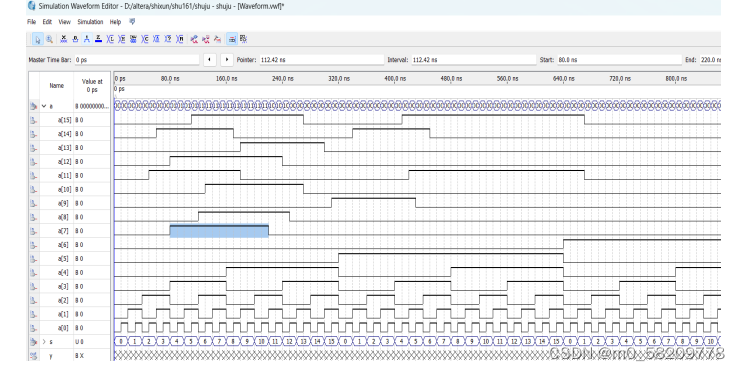

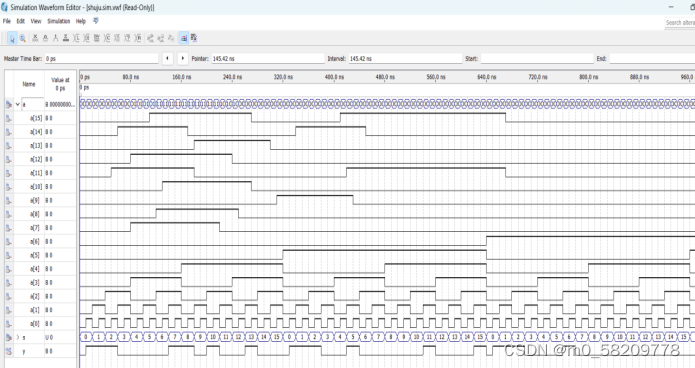

3.3.11 波形图如下,从a的15个分别的状态,根据s的进制状态,以及y的状态,可以看出该图形就是十六选一数据选择器。

4.十六选一数据选择器case语句的VHDL程序

4.1VADL程序

| VHDL程序命令与解释(十六选一数据选择器) |

| library ieee;//导入IEEE库,这个库包含了标准逻辑类型和子程序 use ieee.std_logic_1164.all;//使用IEEE库中的std_logic_1164包,它定义了std_logic类型及其相关类型 library ieee;-- 引入IEEE标准库。标准库中包含各种常用的数据类型和函数。 use ieee.std_logic_1164.all;-- 使用IEEE标准库中的 std_logic_1164 包,该包定义了std_logic和std_logic_vector等数据类型。 entity shuju is-- 定义一个名为 shuju 的实体,这是 VHDL 模块的声明部分。 port(a:in std_logic_vector(15 downto 0);-- 定义一个输入端口 a,它是一个16位的标准逻辑向量(std_logic_vector),输入信号。 s:in std_logic_vector(3 downto 0);-- 定义一个输入端口 s,它是一个4位的标准逻辑向量,选择信号。 y:out std_logic-- 定义一个输出端口 y,它是一个标准逻辑信号,输出信号。 ); end;-- 结束实体声明部分。 architecture a1 of shuju is-- 定义名为 a1 的架构,它描述了实体 shuju 的具体实现 begin-- 开始架构体的定义。 process(a,s)-- 定义一个过程块 process,这个过程块在输入信号 a 或 s 发生变化时触发。 begin -- 过程块的开始。 case s is-- 使用 case 语句,根据选择信号 s 的值进行不同的操作。 when "0000"=>y<=a(0);-- 当选择信号 s 的值为 "0000" 时,输出信号 y 赋值为输入向量 a 的第0位。 when "0001"=>y<=a(1);-- 当选择信号 s 的值为 "0001" 时,输出信号 y 赋值为输入向量 a 的第1位。 when "0010"=>y<=a(2);-- 当选择信号 s 的值为 "0010" 时,输出信号 y 赋值为输入向量 a 的第2位。 when "0011"=>y<=a(3);-- 当选择信号 s 的值为 "0011" 时,输出信号 y 赋值为输入向量 a 的第3位。 when "0100"=>y<=a(4);-- 当选择信号 s 的值为 "0100" 时,输出信号 y 赋值为输入向量 a 的第4位。 when "0101"=>y<=a(5);-- 当选择信号 s 的值为 "0101" 时,输出信号 y 赋值为输入向量 a 的第5位。 when "0110"=>y<=a(6);-- 当选择信号 s 的值为 "0110" 时,输出信号 y 赋值为输入向量 a 的第6位。 when "0111"=>y<=a(7);-- 当选择信号 s 的值为 "0111" 时,输出信号 y 赋值为输入向量 a 的第7位。 when "1000"=>y<=a(8);-- 当选择信号 s 的值为 "1000" 时,输出信号 y 赋值为输入向量 a 的第8位。 when "1001"=>y<=a(9);-- 当选择信号 s 的值为 "1001" 时,输出信号 y 赋值为输入向量 a 的第9位。 when "1010"=>y<=a(10);-- 当选择信号 s 的值为 "1010" 时,输出信号 y 赋值为输入向量 a 的第10位。 when "1011"=>y<=a(11);-- 当选择信号 s 的值为 "1011" 时,输出信号 y 赋值为输入向量 a 的第11位。 when "1100"=>y<=a(12);-- 当选择信号 s 的值为 "1100" 时,输出信号 y 赋值为输入向量 a 的第12位。 when "1101"=>y<=a(13);-- 当选择信号 s 的值为 "1101" 时,输出信号 y 赋值为输入向量 a 的第13位。 when "1110"=>y<=a(14);-- 当选择信号 s 的值为 "1110" 时,输出信号 y 赋值为输入向量 a 的第14位。 when "1111"=>y<=a(15);-- 当选择信号 s 的值为 "1111" 时,输出信号 y 赋值为输入向量 a 的第15位。 when others=>y<='X';-- 当选择信号 s 的值不在上述范围内时,输出信号 y 赋值为未知状态 'X'。 end case;-- 结束 case 语句。 end process; -- 结束过程块。 end a1; -- 结束架构体定义 |

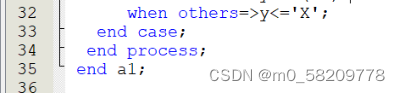

4.2 VHDL代码图片如下:

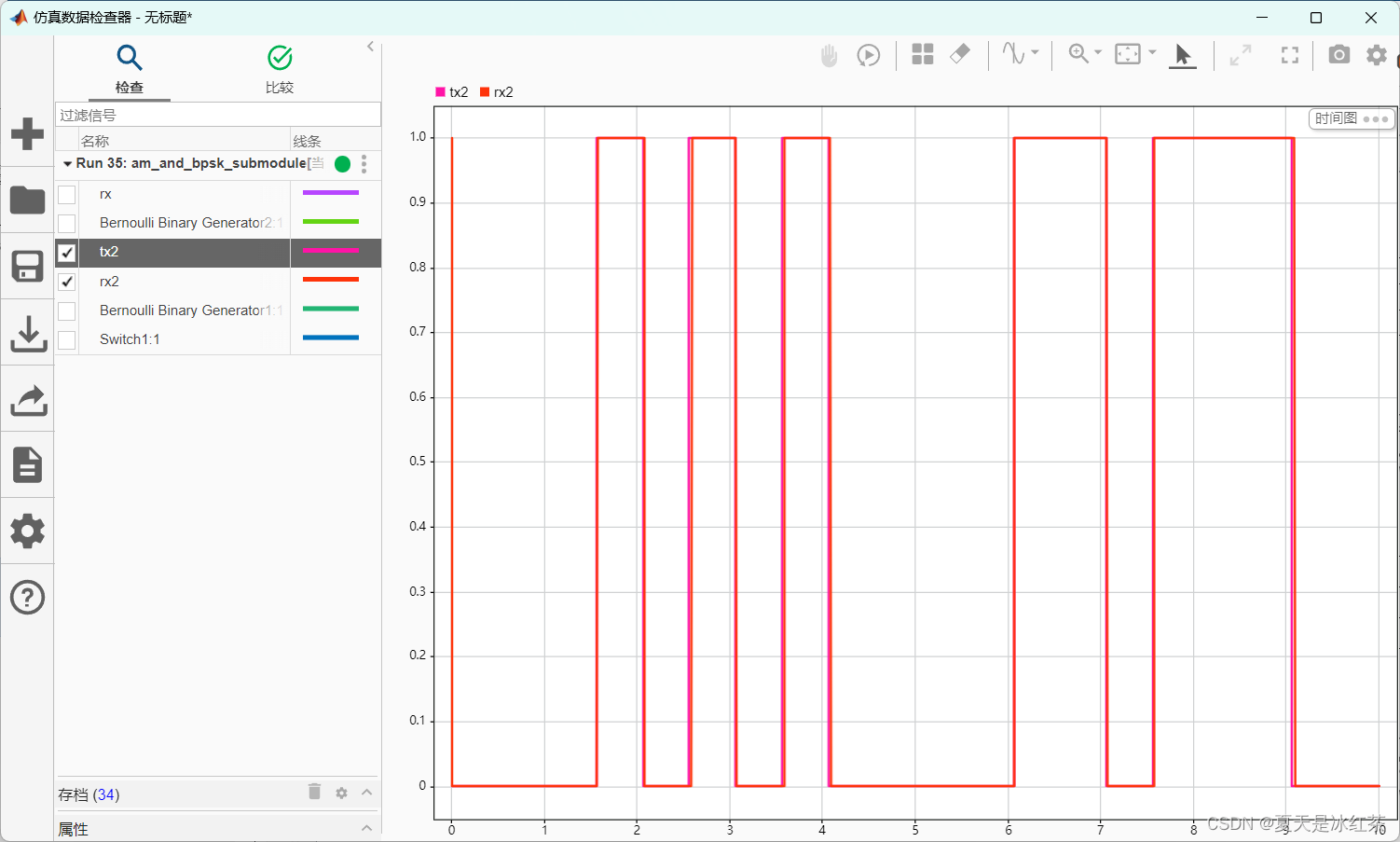

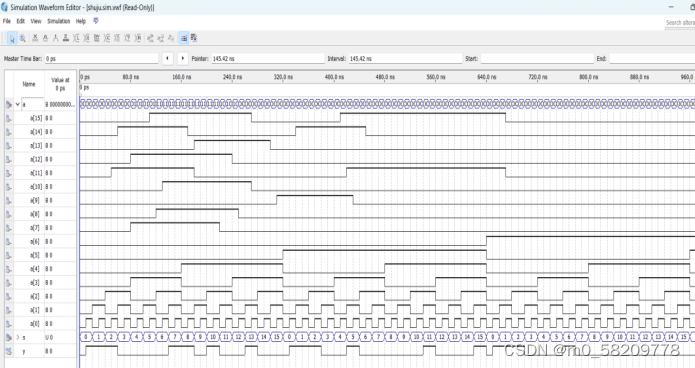

4.3 波形图结果如下:

5.十六选一数据选择器when else语句的VHDL程序

5.十六选一数据选择器when else语句的VHDL程序

5.1 VHDL程序

| VHDL程序命令与解释(十六选一数据选择器) |

| library ieee;//导入IEEE库,这个库包含了标准逻辑类型和子程序 use ieee.std_logic_1164.all;//使用IEEE库中的std_logic_1164包,它定义了std_logic类型及其相关类型 library ieee;-- 引入IEEE标准库。标准库中包含各种常用的数据类型和函数。 use ieee.std_logic_1164.all;-- 使用IEEE标准库中的 std_logic_1164 包,该包定义了std_logic和std_logic_vector等数据类型。 entity shuju is-- 定义一个名为 shuju 的实体,这是 VHDL 模块的声明部分。 port(a:in std_logic_vector(15 downto 0);-- 定义一个输入端口 a,它是一个16位的标准逻辑向量(std_logic_vector),输入信号。 s:in std_logic_vector(3 downto 0);-- 定义一个输入端口 s,它是一个4位的标准逻辑向量,选择信号。 y:out std_logic-- 定义一个输出端口 y,它是一个标准逻辑信号,输出信号。 ); end;-- 结束实体声明部分。 architecture a1 of shuju is-- 定义名为 a1 的架构,它描述了实体 shuju 的具体实现 begin-- 开始架构体的定义。 y <= a(0) when s = "0000" else -- 当选择信号 s 的值为 "0000" 时,输出信号 y 赋值为输入向量 a 的第0位。 a(1) when s = "0001" else -- 当选择信号 s 的值为 "0001" 时,输出信号 y 赋值为输入向量 a 的第1位。 a(2) when s = "0010" else -- 当选择信号 s 的值为 "0010" 时,输出信号 y 赋值为输入向量 a 的第2位。 a(3) when s = "0011" else -- 当选择信号 s 的值为 "0011" 时,输出信号 y 赋值为输入向量 a 的第3位。 a(4) when s = "0100" else -- 当选择信号 s 的值为 "0100" 时,输出信号 y 赋值为输入向量 a 的第4位。 a(5) when s = "0101" else -- 当选择信号 s 的值为 "0101" 时,输出信号 y 赋值为输入向量 a 的第5位。 a(6) when s = "0110" else -- 当选择信号 s 的值为 "0110" 时,输出信号 y 赋值为输入向量 a 的第6位。 a(7) when s = "0111" else -- 当选择信号 s 的值为 "0111" 时,输出信号 y 赋值为输入向量 a 的第7位。 a(8) when s = "1000" else -- 当选择信号 s 的值为 "1000" 时,输出信号 y 赋值为输入向量 a 的第8位。 a(9) when s = "1001" else -- 当选择信号 s 的值为 "1001" 时,输出信号 y 赋值为输入向量 a 的第9位。 a(10) when s = "1010" else -- 当选择信号 s 的值为 "1010" 时,输出信号 y 赋值为输入向量 a 的第10位。 a(11) when s = "1011" else -- 当选择信号 s 的值为 "1011" 时,输出信号 y 赋值为输入向量 a 的第11位。 a(12) when s = "1100" else -- 当选择信号 s 的值为 "1100" 时,输出信号 y 赋值为输入向量 a 的第12位。 a(13) when s = "1101" else -- 当选择信号 s 的值为 "1101" 时,输出信号 y 赋值为输入向量 a 的第13位。 a(14) when s = "1110" else -- 当选择信号 s 的值为 "1110" 时,输出信号 y 赋值为输入向量 a 的第14位。 a(15) when s = "1111" else -- 当选择信号 s 的值为 "1111" 时,输出信号 y 赋值为输入向量 a 的第15位。 'X'; -- 如果选择信号 s 的值不在上述范围内,则输出信号 y 赋值为未知状态 'X' end a1; -- 结束架构体定义。 |

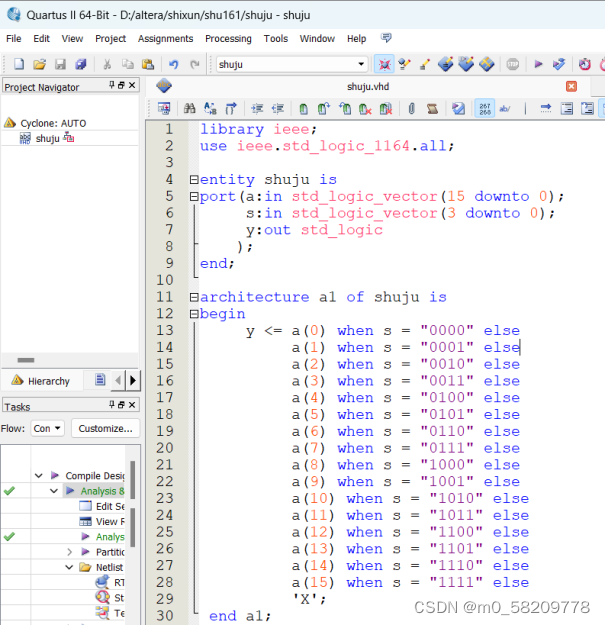

5.2 VHDL程序代码如下

5.3 波形图结果如下:

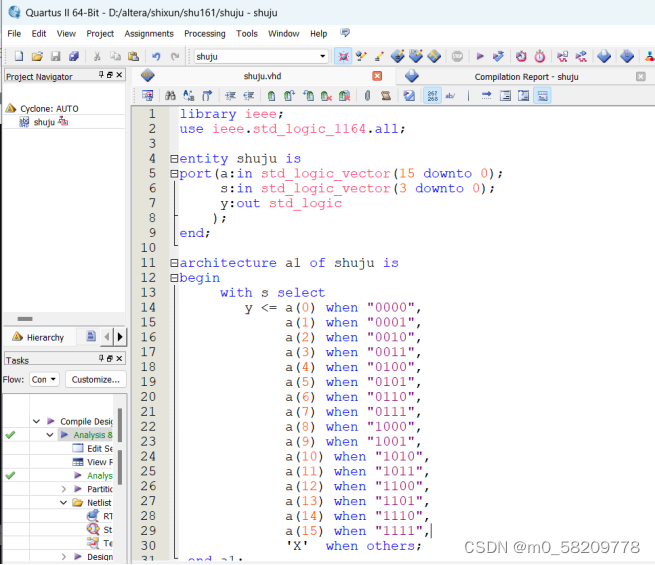

6.十六选一数据选择器when select语句的VHDL程序

6.十六选一数据选择器when select语句的VHDL程序

6.1 VHDL程序

| VHDL程序命令与解释(十六选一数据选择器) |

| library ieee;//导入IEEE库,这个库包含了标准逻辑类型和子程序 use ieee.std_logic_1164.all;//使用IEEE库中的std_logic_1164包,它定义了std_logic类型及其相关类型 library ieee;-- 引入IEEE标准库。标准库中包含各种常用的数据类型和函数。 use ieee.std_logic_1164.all;-- 使用IEEE标准库中的 std_logic_1164 包,该包定义了std_logic和std_logic_vector等数据类型。 entity shuju is-- 定义一个名为 shuju 的实体,这是 VHDL 模块的声明部分。 port(a:in std_logic_vector(15 downto 0);-- 定义一个输入端口 a,它是一个16位的标准逻辑向量(std_logic_vector),输入信号。 s:in std_logic_vector(3 downto 0);-- 定义一个输入端口 s,它是一个4位的标准逻辑向量,选择信号。 y:out std_logic-- 定义一个输出端口 y,它是一个标准逻辑信号,输出信号。 ); end;-- 结束实体声明部分。 architecture a1 of shuju is -- 定义名为 a1 的架构,描述了实体 shuju 的具体实现。 begin -- 开始架构体的定义。 with s select -- 使用 with select 语句,根据选择信号 s 的值进行选择。 y <= a(0) when "0000", -- 当选择信号 s 的值为 "0000" 时,输出信号 y 赋值为输入向量 a 的第0位。 a(1) when "0001", -- 当选择信号 s 的值为 "0001" 时,输出信号 y 赋值为输入向量 a 的第1位。 a(2) when "0010", -- 当选择信号 s 的值为 "0010" 时,输出信号 y 赋值为输入向量 a 的第2位。 a(3) when "0011", -- 当选择信号 s 的值为 "0011" 时,输出信号 y 赋值为输入向量 a 的第3位。 a(4) when "0100", -- 当选择信号 s 的值为 "0100" 时,输出信号 y 赋值为输入向量 a 的第4位。 a(5) when "0101", -- 当选择信号 s 的值为 "0101" 时,输出信号 y 赋值为输入向量 a 的第5位。 a(6) when "0110", -- 当选择信号 s 的值为 "0110" 时,输出信号 y 赋值为输入向量 a 的第6位。 a(7) when "0111", -- 当选择信号 s 的值为 "0111" 时,输出信号 y 赋值为输入向量 a 的第7位。 a(8) when "1000", -- 当选择信号 s 的值为 "1000" 时,输出信号 y 赋值为输入向量 a 的第8位。 a(9) when "1001", -- 当选择信号 s 的值为 "1001" 时,输出信号 y 赋值为输入向量 a 的第9位。 a(10) when "1010", -- 当选择信号 s 的值为 "1010" 时,输出信号 y 赋值为输入向量 a 的第10位。 a(11) when "1011", -- 当选择信号 s 的值为 "1011" 时,输出信号 y 赋值为输入向量 a 的第11位。 a(12) when "1100", -- 当选择信号 s 的值为 "1100" 时,输出信号 y 赋值为输入向量 a 的第12位。 a(13) when "1101", -- 当选择信号 s 的值为 "1101" 时,输出信号 y 赋值为输入向量 a 的第13位。 a(14) when "1110", -- 当选择信号 s 的值为 "1110" 时,输出信号 y 赋值为输入向量 a 的第14位。 a(15) when "1111", -- 当选择信号 s 的值为 "1111" 时,输出信号 y 赋值为输入向量 a 的第15位。 'X' when others; -- 当选择信号 s 的值不在上述范围内时,输出信号 y 赋值为未知状态 'X'。 end a1; -- 结束架构体定义。 |

6.2 VHDL程序代码如下

6.3 波形图结果如下:

总结

1.实验目的:

本次实验旨在通过使用Quartus软件,编写四个十六选一数据选择器的VHDL代码,分别使用if-elsif、case、when else和with select四种语句来实现,并进行波形仿真验证以比较其正确性和性能。

2.实验方法

(1)使用 if-elsif 语句:

逐一检查选择信号s的值,并根据其值选择对应的输入数据位。

(2)使用 case 语句:

采用结构化的case语句,根据选择信号s的不同值进行分支选择。

(3)使用 when else 语句:

通过嵌套的条件选择语句,依次判断选择信号s的值,并选择相应的数据位。

(4)使用 with select 语句:

使用选择语句,根据选择信号s的值直接选择相应的数据位,实现方式最为简洁

3. 波形仿真结果

通过Quartus软件对每种实现方法进行波形仿真,观察输入选择信号s和输入数据a,以及输出信号y的波形变化。仿真结果总结如下:

(1)if-elsif 语句的仿真结果:

仿真波形显示输出信号y随着选择信号s的变化正确地反映了输入数据a中对应位的值。

当s为无效值时,输出y显示为未知状态'X'.

(2)case 语句的仿真结果:

case语句的仿真波形与if-elsif语句一致,输出信号y在选择信号s的不同取值下正确地反映了相应的输入数据位。

(3)when else 语句的仿真结果:

仿真波形显示y随s的变化正确反映了输入数据a中的相应位。

在所有可能的选择信号取值下,输出信号均正确。

(4)with select 语句的仿真结果:

仿真波形显示y在s的每个取值下都正确地选择了输入数据a的对应位。

with select语句提供了最为简洁明了的实现方式,仿真结果完全正确。

4.实验结论

通过对四种不同VHDL实现方式的波形仿真验证,可以得出以下结论:

功能正确性:

四种实现方式均能够正确地实现16选1数据选择器的功能,输出信号y能够正确反映输入选择信号s对应的数据位。

代码简洁性:

使用with select语句的实现最为简洁和直观,代码可读性和维护性最好。case语句的实现结构化程度高,代码也较为简洁明了。

仿真效率:

四种实现方式的仿真效率基本相当,但在代码编写和调试过程中,with select和case语句的实现方式更易于理解和调试。

5. 实验总结

本次实验成功地使用四种不同的VHDL语句实现了16选1数据选择器,并通过Quartus软件进行了波形仿真验证。实验结果表明,每种实现方式都能够正确地实现数据选择器的功能。通过比较,可以看出with select和case语句的实现方式在代码简洁性和可维护性方面具有优势。实验过程中发现,仿真工具能够直观地展示数字电路的行为,有助于设计和验证复杂的数字电路。

致谢

在此,我要向我的导师``老师表示最诚挚的感谢。在整个实验报告撰写的过程中,`老师始终给予我悉心的指导和耐心的解答。他渊博的学识、对专业的热情与执着,以及严谨认真的工作态度,都对我产生了深远的影响。他的亲历亲为、追求完美的精神,不仅教会了我专业知识,更传授了我做人的道理。同时,我也要感谢所有在实验过程中给予我们指导和帮助的老师们。是您们的专业知识和丰富经验,为我们指明了方向,提供了宝贵的建议。您们的严谨治学态度和无私奉献的精神,是我们学习的楷模,让我们在实验过程中收获满满,受益匪浅。

![[WTL/Win32]_[中级]_[MVP架构在实际项目中应用的地方]](https://img-blog.csdnimg.cn/direct/466ffe7b1bcf4f74a032871c30ad58b8.png)