加法器的工作原理:从简单的逻辑到现代计算

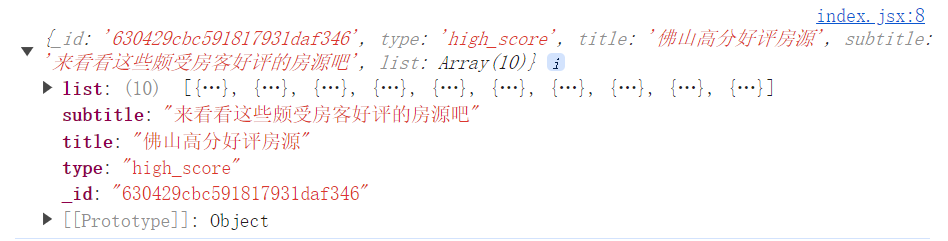

我们在cpu内部结构窥探·「1」中提到CPU内部ALU的核心部件就是运算器,今天就以加法器为例,来讲解我们ALU中算数逻辑运算的过程。

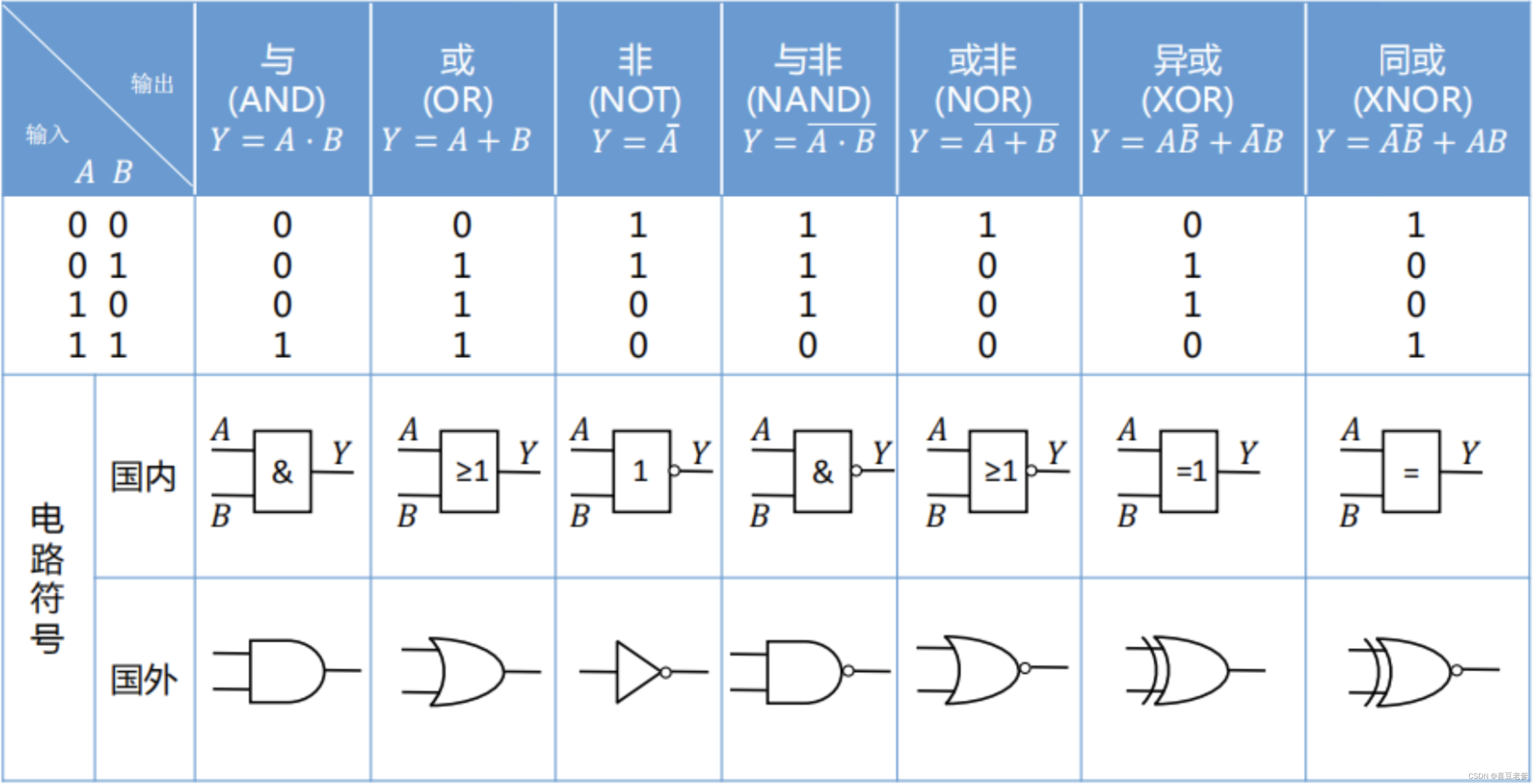

1.认识数字电路中的各种门电路

2. 什么是加法器?

加法器是一种数字电路,用于对二进制数进行加法运算。它们是计算机算术逻辑单元(ALU)的核心组件,也是各种数字系统(如计算器和数字信号处理器)的基础模块。加法器通常可以分为以下几种类型:

- 半加器(Half Adder):处理两个单个位的加法。

- 全加器(Full Adder):处理两个输入位和一个进位位的加法。

- 多位加法器:处理多位二进制数的加法,通常通过连接多个全加器来实现。

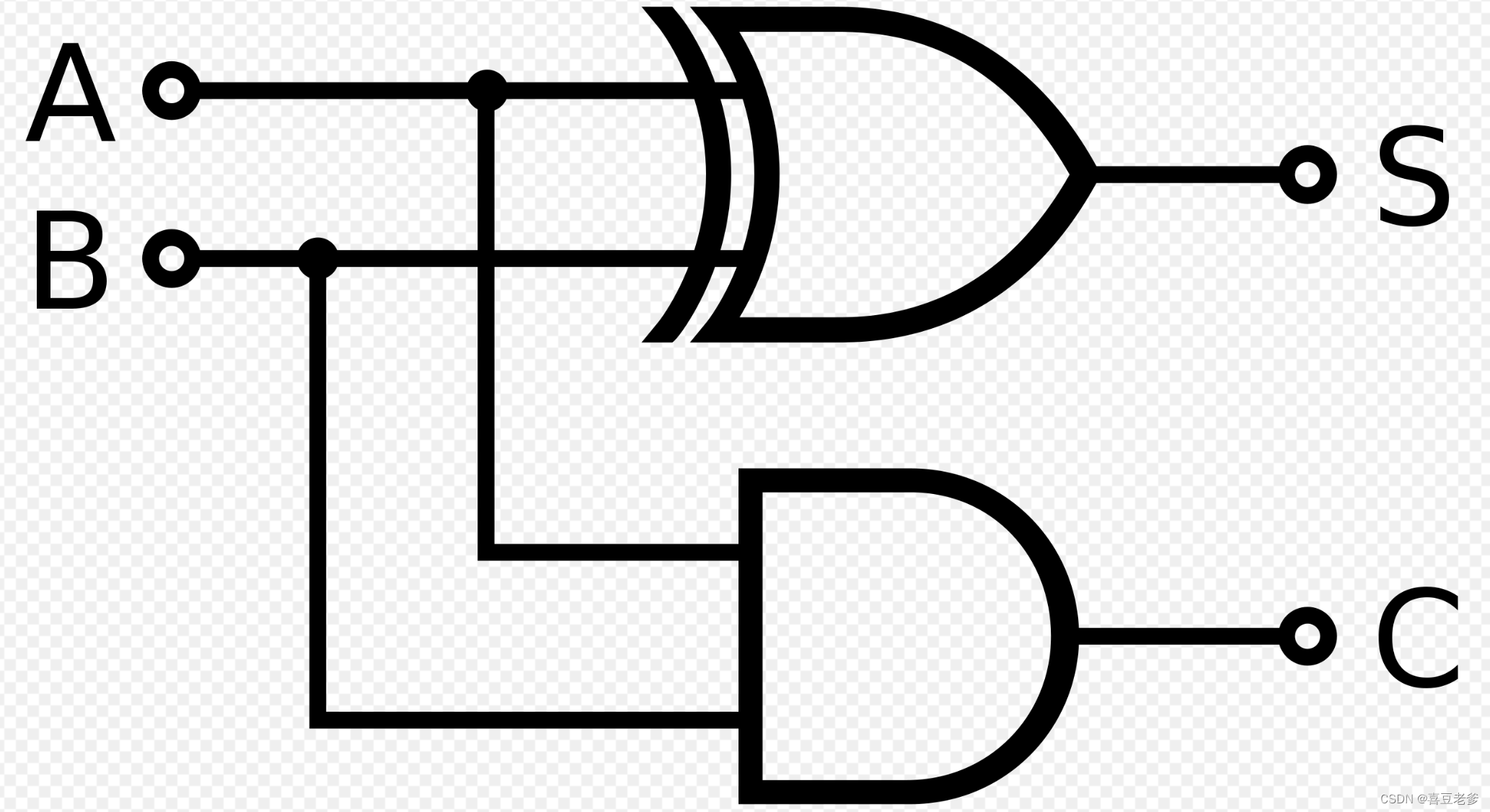

3. 半加器(Half Adder)

逻辑电路

半加器是最基本的加法器,它负责对两个单个位进行加法运算,输出一个和(Sum)和一个进位(Carry)。

工作原理

半加器接收两个输入位 ( A ) 和 ( B ):

-

和(Sum):由输入位 ( A ) 和 ( B ) 的异或(XOR)运算得出。其逻辑表达式为:

Sum=A⊕B

-

进位(Carry):由输入位 ( A ) 和 ( B ) 的与(AND)运算得出。其逻辑表达式为:

-

Carry=A⋅B

| A | B | Sum | Carry |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

如表所示,当 ( A ) 和 ( B ) 都为 1 时,和为 0 并产生一个进位。半加器的局限性在于它不能处理进位输入,因此只能用于简单的单个位加法。

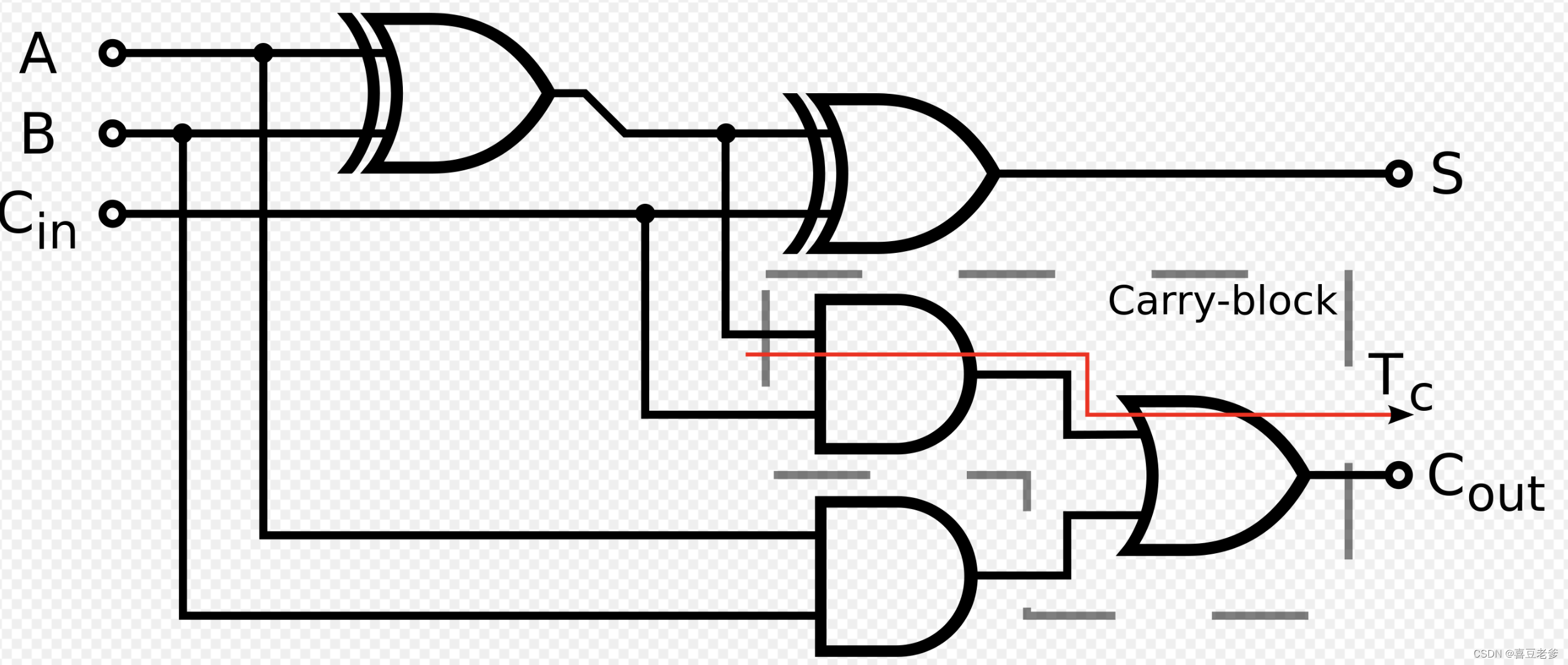

4. 全加器(Full Adder)

逻辑电路

全加器扩展了半加器的功能,能够处理两个输入位和一个来自低位的进位输入。它输出一个和和一个进位输出。

工作原理

全加器有三个输入:( A )、( B ) 和 ( C_{in} )(进位输入)。它通过组合两个半加器的逻辑实现:

-

第一个半加器对 ( A ) 和 ( B ) 进行加法,产生初步的和 ( S_1 ) 和进位 ( C_1 ):

S1=A⊕B C1=A⋅B -

第二个半加器将初步的和 ( S_1 ) 与进位输入 ( C_{in} ) 相加,产生最终的和 ( S ) 和第二个进位 ( C_2 ):

S=S1⊕Cin C2=S1⋅Cin -

最终的进位输出 ( C_{out} ) 是两个进位的或运算:

Cout=C1∨C2

| A | B | ( Cin) | Sum | ( Cout ) |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 | 0 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 | 1 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 |

全加器的输出逻辑综合了两个半加器和一个或门(OR Gate)的运算结果,使它能够处理多位加法中的进位传递。

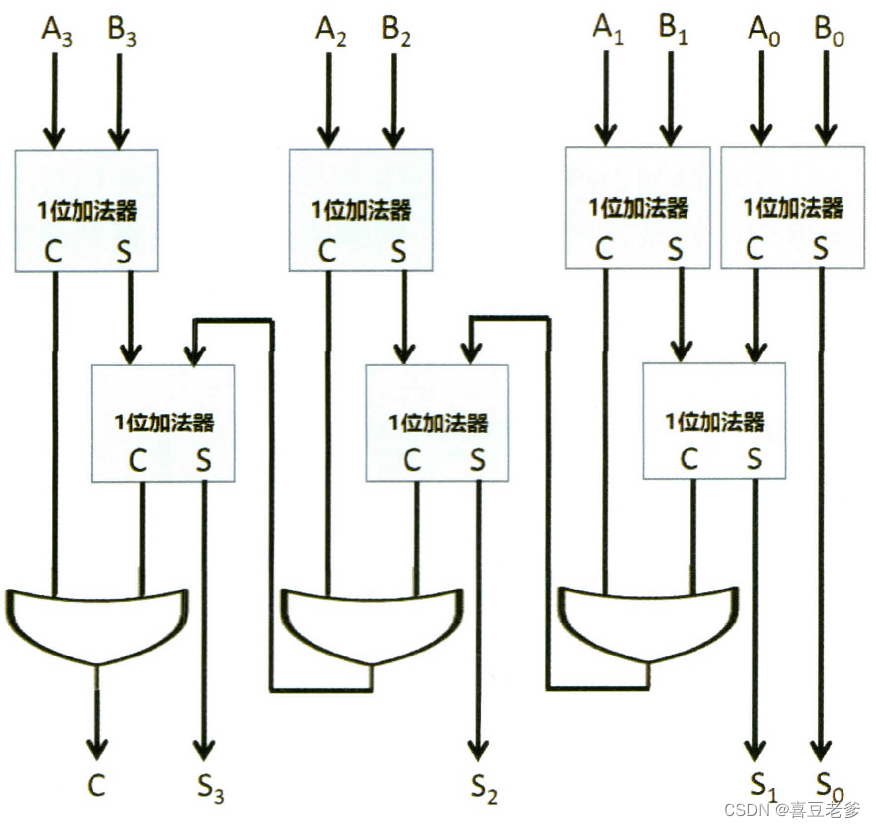

4. 多位加法器

如下图是一个4位加法器的逻辑电路:

5. 举一反三

以此类推,我们可以了解到ALU的其他运算单元如:加法器、减法器、与非门(用于逻辑运算)等的实现原理。

在这里仅从最基本的一个加法运算出发,来了解cpu内部ALU是如何实现这些运算的,真实的ALU要比这个复杂千万倍,这只是他最基本的原理。

![[Algorithm][动态规划][01背包问题][目标和][最后一块石头的重量Ⅱ]详细讲解](https://img-blog.csdnimg.cn/direct/cf1aa68624594a93b4a093cf92d2cfb4.png)