目录

1. 简介

2. 用法解析

2.1 命令语法

2.2 实例展示

3. 注意事项

4. 总结

1. 简介

在 Vitis 工具流程中,Vitis HLS 能够自动将 m_axi 接口端口的大小调整为 512 位,以改善突发访问能力。但是,端口宽度自动调整仅支持标准 C 语言数据类型,不支持聚合类型,例如,ap_int、ap_uint、struct 或 array。

打个比方,你有一个水管,HLS 工具可以自动把这个水管变粗,让更多的水(数据)一次通过,这样就提高了效率。但是,这个自动变粗的魔法只适用于简单的水管(标准 C 语言数据类型),对于一些特殊设计的水管(比如 ap_int、ap_uint、struct 或 array 这些复杂的数据类型),它就不起作用了。

本文还展示一个例子,了解如何在Vivado IP流程中为m_axi端口启用自动端口扩展。

在 Vitis Kernel Flow 中,默认情况下以下两个config_interface设置是开启的:

config_interface -m_axi_max_widen_bitwidth 256

config_interface -m_axi_alignment_byte_size 64在Vivado IP流程中,则需要显式设置它们。可以通过 GUI 或者编译指令设置。

2. 用法解析

2.1 命令语法

HLS 工具使用以下 2 条命令来自动调整端口宽度:

- config_interface -m_axi_max_widen_bitwidth <N>:将 M-AXI 接口上的突发自动拓宽至指定的位宽。<N> 的值必须为 2 的幂(介于 0 到 1024 之间)。

- config_interface -m_axi_alignment_byte_size <N>:突发拓宽还需要明确的对齐属性。假定映射到 m_axi 接口的指针至少对齐到所提供的宽度(以字节为单位,值为 2 的幂)。这样有助于自动进行突发拓宽。

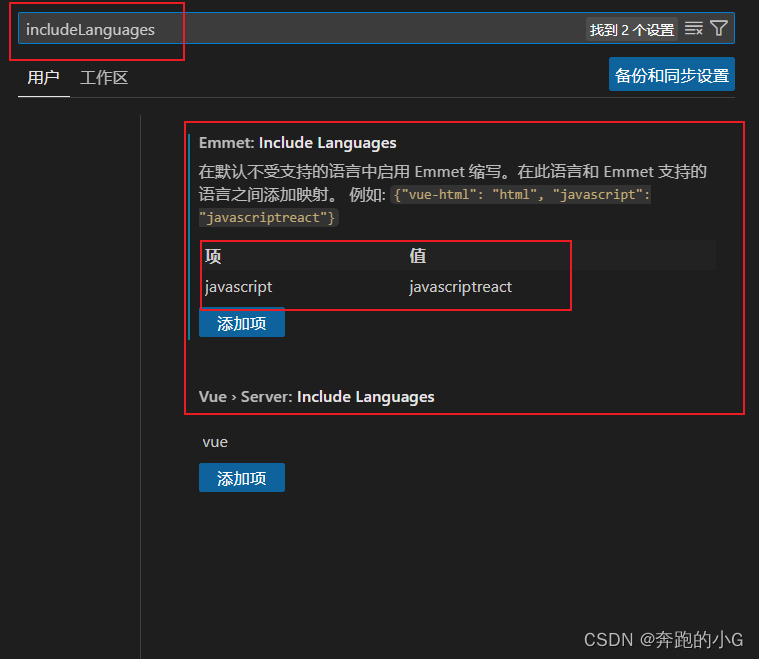

或者通过 GUI 界面进行设置:

2.2 实例展示

#include <cstdlib>

#include <iostream>

constexpr uint64_t N = 64;

constexpr uint64_t MAXWBW = 256;

void example(int a[N], int b[N]) {

#pragma HLS INTERFACE m_axi port = a depth = N bundle = gmem max_widen_bitwidth = MAXWBW

#pragma HLS INTERFACE m_axi port = b depth = N bundle = gmem

int buff[N];

for (size_t i = 0; i < N; ++i) {

#pragma HLS PIPELINE II = 1

buff[i] = a[i];

buff[i] = buff[i] + 100;

b[i] = buff[i];

}

}

- #include <cstdlib> 和 #include <iostream>:这些是标准 C++ 头文件,用于包含有关内存分配和输入/输出的函数和类。

- constexpr uint64_t N = 64; 和 constexpr uint64_t MAXWBW = 256;:这些是常量定义,其中 N 表示数组大小,MAXWBW 表示最大宽度。

- #pragma HLS INTERFACE m_axi port = a depth = N bundle = gmem max_widen_bitwidth = MAXWBW 和 #pragma HLS INTERFACE m_axi port = b depth = N bundle = gmem:这些是 Vitis HLS 的指令,用于指定接口和内存映射。它们告诉综合工具如何处理输入和输出。

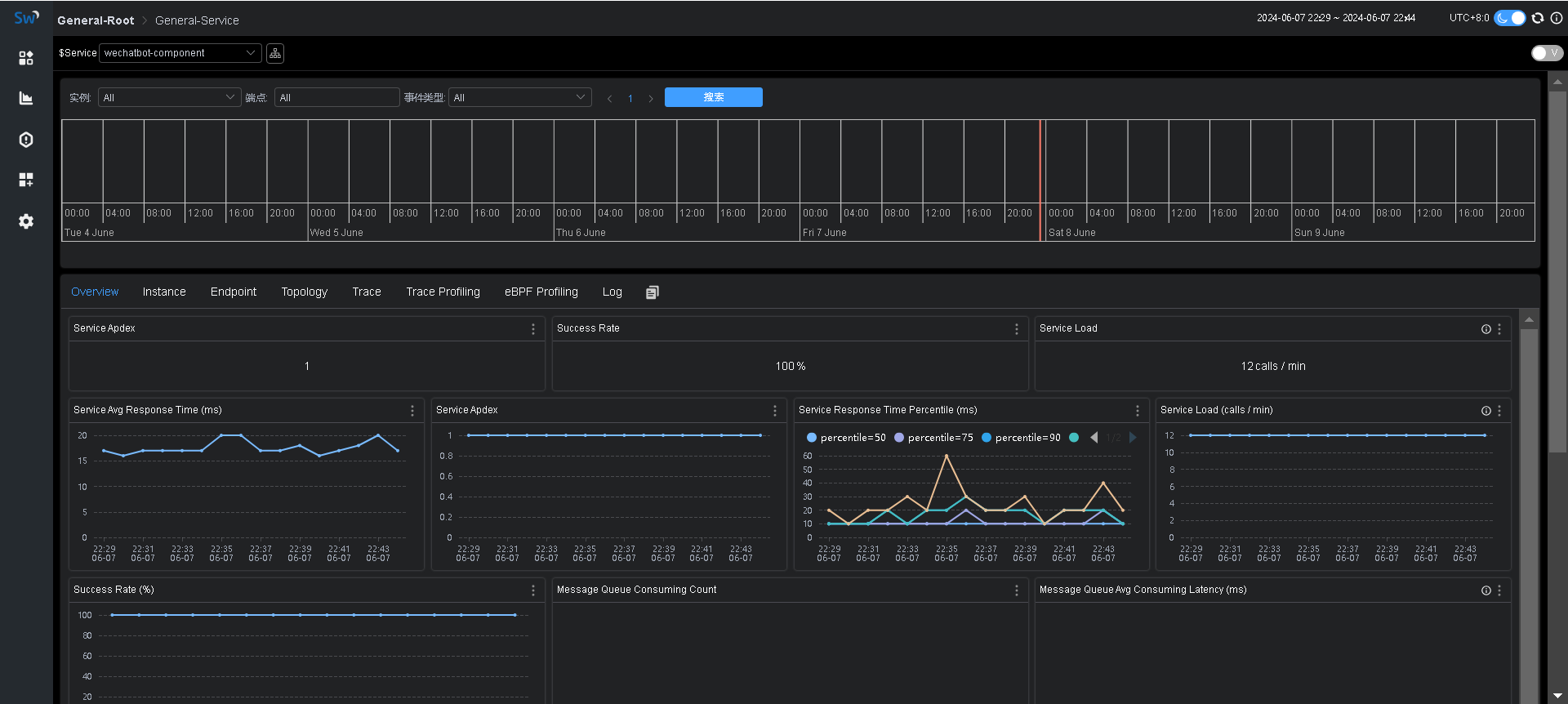

查看综合报告:

================================================================

== HW Interfaces

================================================================

* M_AXI

+------------+------------+---------------+---------+--------+----------+-----------+--------------+--------------+-------------+-------------+

| Interface | Data Width | Address Width | Latency | Offset | Register | Max Widen | Max Read | Max Write | Num Read | Num Write |

| | (SW->HW) | | | | | Bitwidth | Burst Length | Burst Length | Outstanding | Outstanding |

+------------+------------+---------------+---------+--------+----------+-----------+--------------+--------------+-------------+-------------+

| m_axi_gmem | 32 -> 256 | 64 | 0 | slave | 0 | 256 | 16 | 16 | 16 | 16 |

+------------+------------+---------------+---------+--------+----------+-----------+--------------+--------------+-------------+-------------+3. 注意事项

接口上的结构体会阻止端口的自动拓宽操作。必须将结构体拆分为多个独立元素才能启用MAXI位宽拓展功能。

使用端口宽度自动调整功能有利有弊,需在使用时审慎考量。此功能可缩短来自 DDR 的读取时延,因为该工具读取的是大矢量而不是数据类型大小。它还会添加更多必要资源,以缓冲巨型矢量,并将数据相应转换为数据路径大小。

仅当工具可看到突发访问时,自动调整端口宽度大小功能才能调整端口大小。因此,突发所需的所有前置条件(如 AXI突发传输 中所述)都必须得到满足后才能调整端口大小。这些前置条件包括:

- 必须按单调递增访问顺序(访问的存储器位置和访问时间两方面都是如此)。不能访问位于先前访问的两处存储器位置之间的存储器位置,即没有重叠。

- 从全局存储器进行访问时使用的模式应采用顺序访问模式,并具有下列附加要求:

- 需对非矢量类型执行顺序访问

- 顺序访问的起始位置需对齐到拓宽后的字大小

- 顺序访问的长度需被拓宽因子整除

4. 总结

在Vitis工具流程中,Vitis HLS可以通过自动调整m_axi接口端口宽度至512位来提高突发访问能力。这种自动端口扩展仅适用于标准C语言数据类型,不支持聚合类型。为了在Vivado IP流程中启用这一功能,必须显式设置config_interface命令。设置m_axi_max_widen_bitwidth和m_axi_alignment_byte_size可以指定接口的最大位宽和对齐字节数。代码实例展示了如何通过HLS指令配置接口和内存映射,以优化性能。使用此功能需注意结构体会阻止端口拓宽,且自动调整端口宽度功能仅在满足突发访问的前提条件时才能生效。此功能可缩短读取时延,但也会增加资源需求。