收到 ICESTICK 评估板后还没好好玩。先来点个灯,正好把之前介绍过的工具链串起来用一下。

代码

- Verilog代码只有一个顶层模块

top.v,定义如下:

module top(output wire D1,

output wire D2,

output wire D3,

output wire D4,

output wire D5);

assign D1 = 1'b1;

assign D2 = 1'b0;

assign D3 = 1'b1;

assign D4 = 1'b1;

assign D5 = 1'b1;

endmodule

在这个模块中,我们定义了五个输出引脚(D1到D5),并赋予了它们固定的值。注意,这里让LED2不亮,这是为了实验效果而特别安排的。

- 接下来是引脚配置文件

pinmap.pcf,它将模块中的引脚与ICESTICK的物理引脚对应起来:

set_io D1 99

set_io D2 98

set_io D3 97

set_io D4 96

set_io D5 95

综合(synthesis)

$ yosys -p "synth_ice40 -top top -blif blink_on.blif -json blink_on.json" top.v

输出如下:

/----------------------------------------------------------------------------\

| yosys -- Yosys Open SYnthesis Suite |

| Copyright (C) 2012 - 2024 Claire Xenia Wolf <claire@yosyshq.com> |

| Distributed under an ISC-like license, type "license" to see terms |

\----------------------------------------------------------------------------/

Yosys 0.40+45 (git sha1 dd2195543, g++ 11.4.0-1ubuntu1~22.04 -fPIC -Os)

-- Parsing `top.v' using frontend ` -vlog2k' --

1. Executing Verilog-2005 frontend: top.v

Parsing Verilog input from `top.v' to AST representation.

Storing AST representation for module `$abstract\top'.

Successfully finished Verilog frontend.

-- Running command `synth_ice40 -top top -blif blink_on.blif -json blink_on.json' --

2. Executing SYNTH_ICE40 pass.

2.1. Executing Verilog-2005 frontend: /usr/local/bin/../share/yosys/ice40/cells_sim.v

Parsing Verilog input from `/usr/local/bin/../share/yosys/ice40/cells_sim.v' to AST representation.

Generating RTLIL representation for module `\SB_IO'.

Generating RTLIL representation for module `\SB_GB_IO'.

Generating RTLIL representation for module `\SB_GB'.

Generating RTLIL representation for module `\SB_LUT4'.

Generating RTLIL representation for module `\SB_CARRY'.

Generating RTLIL representation for module `\SB_DFF'.

Generating RTLIL representation for module `\SB_DFFE'.

Generating RTLIL representation for module `\SB_DFFSR'.

Generating RTLIL representation for module `\SB_DFFR'.

Generating RTLIL representation for module `\SB_DFFSS'.

Generating RTLIL representation for module `\SB_DFFS'.

Generating RTLIL representation for module `\SB_DFFESR'.

Generating RTLIL representation for module `\SB_DFFER'.

Generating RTLIL representation for module `\SB_DFFESS'.

Generating RTLIL representation for module `\SB_DFFES'.

Generating RTLIL representation for module `\SB_DFFN'.

Generating RTLIL representation for module `\SB_DFFNE'.

Generating RTLIL representation for module `\SB_DFFNSR'.

Generating RTLIL representation for module `\SB_DFFNR'.

Generating RTLIL representation for module `\SB_DFFNSS'.

Generating RTLIL representation for module `\SB_DFFNS'.

Generating RTLIL representation for module `\SB_DFFNESR'.

Generating RTLIL representation for module `\SB_DFFNER'.

Generating RTLIL representation for module `\SB_DFFNESS'.

Generating RTLIL representation for module `\SB_DFFNES'.

Generating RTLIL representation for module `\SB_RAM40_4K'.

Generating RTLIL representation for module `\SB_RAM40_4KNR'.

Generating RTLIL representation for module `\SB_RAM40_4KNW'.

Generating RTLIL representation for module `\SB_RAM40_4KNRNW'.

Generating RTLIL representation for module `\ICESTORM_LC'.

Generating RTLIL representation for module `\SB_PLL40_CORE'.

Generating RTLIL representation for module `\SB_PLL40_PAD'.

Generating RTLIL representation for module `\SB_PLL40_2_PAD'.

Generating RTLIL representation for module `\SB_PLL40_2F_CORE'.

Generating RTLIL representation for module `\SB_PLL40_2F_PAD'.

Generating RTLIL representation for module `\SB_WARMBOOT'.

Generating RTLIL representation for module `\SB_SPRAM256KA'.

Generating RTLIL representation for module `\SB_HFOSC'.

Generating RTLIL representation for module `\SB_LFOSC'.

Generating RTLIL representation for module `\SB_RGBA_DRV'.

Generating RTLIL representation for module `\SB_LED_DRV_CUR'.

Generating RTLIL representation for module `\SB_RGB_DRV'.

Generating RTLIL representation for module `\SB_I2C'.

Generating RTLIL representation for module `\SB_SPI'.

Generating RTLIL representation for module `\SB_LEDDA_IP'.

Generating RTLIL representation for module `\SB_FILTER_50NS'.

Generating RTLIL representation for module `\SB_IO_I3C'.

Generating RTLIL representation for module `\SB_IO_OD'.

Generating RTLIL representation for module `\SB_MAC16'.

Generating RTLIL representation for module `\ICESTORM_RAM'.

Successfully finished Verilog frontend.

2.2. Executing HIERARCHY pass (managing design hierarchy).

2.3. Executing AST frontend in derive mode using pre-parsed AST for module `\top'.

Generating RTLIL representation for module `\top'.

2.3.1. Analyzing design hierarchy..

Top module: \top

2.3.2. Analyzing design hierarchy..

Top module: \top

Removing unused module `$abstract\top'.

Removed 1 unused modules.

2.4. Executing PROC pass (convert processes to netlists).

2.4.1. Executing PROC_CLEAN pass (remove empty switches from decision trees).

Cleaned up 0 empty switches.

2.4.2. Executing PROC_RMDEAD pass (remove dead branches from decision trees).

Marked 1 switch rules as full_case in process $proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:1414$241 in module SB_DFFNES.

Marked 1 switch rules as full_case in process $proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:1353$234 in module SB_DFFNESS.

Marked 1 switch rules as full_case in process $proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:1273$230 in module SB_DFFNER.

Marked 1 switch rules as full_case in process $proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:1212$223 in module SB_DFFNESR.

Marked 1 switch rules as full_case in process $proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:1138$220 in module SB_DFFNS.

Marked 1 switch rules as full_case in process $proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:1088$217 in module SB_DFFNSS.

Marked 1 switch rules as full_case in process $proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:1017$214 in module SB_DFFNR.

Marked 1 switch rules as full_case in process $proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:967$211 in module SB_DFFNSR.

Marked 1 switch rules as full_case in process $proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:803$203 in module SB_DFFES.

Marked 1 switch rules as full_case in process $proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:742$196 in module SB_DFFESS.

Marked 1 switch rules as full_case in process $proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:662$192 in module SB_DFFER.

Marked 1 switch rules as full_case in process $proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:601$185 in module SB_DFFESR.

Marked 1 switch rules as full_case in process $proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:527$182 in module SB_DFFS.

Marked 1 switch rules as full_case in process $proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:477$179 in module SB_DFFSS.

Marked 1 switch rules as full_case in process $proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:406$176 in module SB_DFFR.

Marked 1 switch rules as full_case in process $proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:356$173 in module SB_DFFSR.

Removed a total of 0 dead cases.

2.4.3. Executing PROC_PRUNE pass (remove redundant assignments in processes).

Removed 8 redundant assignments.

Promoted 22 assignments to connections.

2.4.4. Executing PROC_INIT pass (extract init attributes).

Found init rule in `\SB_DFFNES.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:0$244'.

Set init value: \Q = 1'0

Found init rule in `\SB_DFFNESS.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:0$240'.

Set init value: \Q = 1'0

Found init rule in `\SB_DFFNER.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:0$233'.

Set init value: \Q = 1'0

Found init rule in `\SB_DFFNESR.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:0$229'.

Set init value: \Q = 1'0

Found init rule in `\SB_DFFNS.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:0$222'.

Set init value: \Q = 1'0

Found init rule in `\SB_DFFNSS.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:0$219'.

Set init value: \Q = 1'0

Found init rule in `\SB_DFFNR.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:0$216'.

Set init value: \Q = 1'0

Found init rule in `\SB_DFFNSR.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:0$213'.

Set init value: \Q = 1'0

Found init rule in `\SB_DFFNE.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:0$210'.

Set init value: \Q = 1'0

Found init rule in `\SB_DFFN.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:0$208'.

Set init value: \Q = 1'0

Found init rule in `\SB_DFFES.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:0$206'.

Set init value: \Q = 1'0

Found init rule in `\SB_DFFESS.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:0$202'.

Set init value: \Q = 1'0

Found init rule in `\SB_DFFER.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:0$195'.

Set init value: \Q = 1'0

Found init rule in `\SB_DFFESR.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:0$191'.

Set init value: \Q = 1'0

Found init rule in `\SB_DFFS.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:0$184'.

Set init value: \Q = 1'0

Found init rule in `\SB_DFFSS.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:0$181'.

Set init value: \Q = 1'0

Found init rule in `\SB_DFFR.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:0$178'.

Set init value: \Q = 1'0

Found init rule in `\SB_DFFSR.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:0$175'.

Set init value: \Q = 1'0

Found init rule in `\SB_DFFE.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:0$172'.

Set init value: \Q = 1'0

Found init rule in `\SB_DFF.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:0$170'.

Set init value: \Q = 1'0

2.4.5. Executing PROC_ARST pass (detect async resets in processes).

Found async reset \S in `\SB_DFFNES.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:1414$241'.

Found async reset \R in `\SB_DFFNER.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:1273$230'.

Found async reset \S in `\SB_DFFNS.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:1138$220'.

Found async reset \R in `\SB_DFFNR.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:1017$214'.

Found async reset \S in `\SB_DFFES.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:803$203'.

Found async reset \R in `\SB_DFFER.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:662$192'.

Found async reset \S in `\SB_DFFS.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:527$182'.

Found async reset \R in `\SB_DFFR.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:406$176'.

2.4.6. Executing PROC_ROM pass (convert switches to ROMs).

Converted 0 switches.

<suppressed ~18 debug messages>

2.4.7. Executing PROC_MUX pass (convert decision trees to multiplexers).

Creating decoders for process `\SB_DFFNES.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:0$244'.

Creating decoders for process `\SB_DFFNES.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:1414$241'.

1/1: $0\Q[0:0]

Creating decoders for process `\SB_DFFNESS.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:0$240'.

Creating decoders for process `\SB_DFFNESS.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:1353$234'.

1/1: $0\Q[0:0]

Creating decoders for process `\SB_DFFNER.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:0$233'.

Creating decoders for process `\SB_DFFNER.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:1273$230'.

1/1: $0\Q[0:0]

Creating decoders for process `\SB_DFFNESR.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:0$229'.

Creating decoders for process `\SB_DFFNESR.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:1212$223'.

1/1: $0\Q[0:0]

Creating decoders for process `\SB_DFFNS.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:0$222'.

Creating decoders for process `\SB_DFFNS.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:1138$220'.

1/1: $0\Q[0:0]

Creating decoders for process `\SB_DFFNSS.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:0$219'.

Creating decoders for process `\SB_DFFNSS.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:1088$217'.

1/1: $0\Q[0:0]

Creating decoders for process `\SB_DFFNR.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:0$216'.

Creating decoders for process `\SB_DFFNR.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:1017$214'.

1/1: $0\Q[0:0]

Creating decoders for process `\SB_DFFNSR.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:0$213'.

Creating decoders for process `\SB_DFFNSR.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:967$211'.

1/1: $0\Q[0:0]

Creating decoders for process `\SB_DFFNE.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:0$210'.

Creating decoders for process `\SB_DFFNE.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:922$209'.

1/1: $0\Q[0:0]

Creating decoders for process `\SB_DFFN.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:0$208'.

Creating decoders for process `\SB_DFFN.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:882$207'.

Creating decoders for process `\SB_DFFES.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:0$206'.

Creating decoders for process `\SB_DFFES.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:803$203'.

1/1: $0\Q[0:0]

Creating decoders for process `\SB_DFFESS.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:0$202'.

Creating decoders for process `\SB_DFFESS.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:742$196'.

1/1: $0\Q[0:0]

Creating decoders for process `\SB_DFFER.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:0$195'.

Creating decoders for process `\SB_DFFER.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:662$192'.

1/1: $0\Q[0:0]

Creating decoders for process `\SB_DFFESR.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:0$191'.

Creating decoders for process `\SB_DFFESR.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:601$185'.

1/1: $0\Q[0:0]

Creating decoders for process `\SB_DFFS.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:0$184'.

Creating decoders for process `\SB_DFFS.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:527$182'.

1/1: $0\Q[0:0]

Creating decoders for process `\SB_DFFSS.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:0$181'.

Creating decoders for process `\SB_DFFSS.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:477$179'.

1/1: $0\Q[0:0]

Creating decoders for process `\SB_DFFR.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:0$178'.

Creating decoders for process `\SB_DFFR.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:406$176'.

1/1: $0\Q[0:0]

Creating decoders for process `\SB_DFFSR.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:0$175'.

Creating decoders for process `\SB_DFFSR.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:356$173'.

1/1: $0\Q[0:0]

Creating decoders for process `\SB_DFFE.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:0$172'.

Creating decoders for process `\SB_DFFE.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:311$171'.

1/1: $0\Q[0:0]

Creating decoders for process `\SB_DFF.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:0$170'.

Creating decoders for process `\SB_DFF.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:271$169'.

2.4.8. Executing PROC_DLATCH pass (convert process syncs to latches).

2.4.9. Executing PROC_DFF pass (convert process syncs to FFs).

Creating register for signal `\SB_DFFNES.\Q' using process `\SB_DFFNES.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:1414$241'.

created $adff cell `$procdff$425' with negative edge clock and positive level reset.

Creating register for signal `\SB_DFFNESS.\Q' using process `\SB_DFFNESS.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:1353$234'.

created $dff cell `$procdff$426' with negative edge clock.

Creating register for signal `\SB_DFFNER.\Q' using process `\SB_DFFNER.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:1273$230'.

created $adff cell `$procdff$427' with negative edge clock and positive level reset.

Creating register for signal `\SB_DFFNESR.\Q' using process `\SB_DFFNESR.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:1212$223'.

created $dff cell `$procdff$428' with negative edge clock.

Creating register for signal `\SB_DFFNS.\Q' using process `\SB_DFFNS.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:1138$220'.

created $adff cell `$procdff$429' with negative edge clock and positive level reset.

Creating register for signal `\SB_DFFNSS.\Q' using process `\SB_DFFNSS.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:1088$217'.

created $dff cell `$procdff$430' with negative edge clock.

Creating register for signal `\SB_DFFNR.\Q' using process `\SB_DFFNR.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:1017$214'.

created $adff cell `$procdff$431' with negative edge clock and positive level reset.

Creating register for signal `\SB_DFFNSR.\Q' using process `\SB_DFFNSR.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:967$211'.

created $dff cell `$procdff$432' with negative edge clock.

Creating register for signal `\SB_DFFNE.\Q' using process `\SB_DFFNE.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:922$209'.

created $dff cell `$procdff$433' with negative edge clock.

Creating register for signal `\SB_DFFN.\Q' using process `\SB_DFFN.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:882$207'.

created $dff cell `$procdff$434' with negative edge clock.

Creating register for signal `\SB_DFFES.\Q' using process `\SB_DFFES.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:803$203'.

created $adff cell `$procdff$435' with positive edge clock and positive level reset.

Creating register for signal `\SB_DFFESS.\Q' using process `\SB_DFFESS.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:742$196'.

created $dff cell `$procdff$436' with positive edge clock.

Creating register for signal `\SB_DFFER.\Q' using process `\SB_DFFER.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:662$192'.

created $adff cell `$procdff$437' with positive edge clock and positive level reset.

Creating register for signal `\SB_DFFESR.\Q' using process `\SB_DFFESR.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:601$185'.

created $dff cell `$procdff$438' with positive edge clock.

Creating register for signal `\SB_DFFS.\Q' using process `\SB_DFFS.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:527$182'.

created $adff cell `$procdff$439' with positive edge clock and positive level reset.

Creating register for signal `\SB_DFFSS.\Q' using process `\SB_DFFSS.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:477$179'.

created $dff cell `$procdff$440' with positive edge clock.

Creating register for signal `\SB_DFFR.\Q' using process `\SB_DFFR.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:406$176'.

created $adff cell `$procdff$441' with positive edge clock and positive level reset.

Creating register for signal `\SB_DFFSR.\Q' using process `\SB_DFFSR.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:356$173'.

created $dff cell `$procdff$442' with positive edge clock.

Creating register for signal `\SB_DFFE.\Q' using process `\SB_DFFE.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:311$171'.

created $dff cell `$procdff$443' with positive edge clock.

Creating register for signal `\SB_DFF.\Q' using process `\SB_DFF.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:271$169'.

created $dff cell `$procdff$444' with positive edge clock.

2.4.10. Executing PROC_MEMWR pass (convert process memory writes to cells).

2.4.11. Executing PROC_CLEAN pass (remove empty switches from decision trees).

Removing empty process `SB_DFFNES.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:0$244'.

Found and cleaned up 1 empty switch in `\SB_DFFNES.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:1414$241'.

Removing empty process `SB_DFFNES.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:1414$241'.

Removing empty process `SB_DFFNESS.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:0$240'.

Found and cleaned up 2 empty switches in `\SB_DFFNESS.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:1353$234'.

Removing empty process `SB_DFFNESS.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:1353$234'.

Removing empty process `SB_DFFNER.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:0$233'.

Found and cleaned up 1 empty switch in `\SB_DFFNER.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:1273$230'.

Removing empty process `SB_DFFNER.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:1273$230'.

Removing empty process `SB_DFFNESR.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:0$229'.

Found and cleaned up 2 empty switches in `\SB_DFFNESR.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:1212$223'.

Removing empty process `SB_DFFNESR.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:1212$223'.

Removing empty process `SB_DFFNS.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:0$222'.

Removing empty process `SB_DFFNS.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:1138$220'.

Removing empty process `SB_DFFNSS.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:0$219'.

Found and cleaned up 1 empty switch in `\SB_DFFNSS.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:1088$217'.

Removing empty process `SB_DFFNSS.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:1088$217'.

Removing empty process `SB_DFFNR.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:0$216'.

Removing empty process `SB_DFFNR.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:1017$214'.

Removing empty process `SB_DFFNSR.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:0$213'.

Found and cleaned up 1 empty switch in `\SB_DFFNSR.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:967$211'.

Removing empty process `SB_DFFNSR.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:967$211'.

Removing empty process `SB_DFFNE.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:0$210'.

Found and cleaned up 1 empty switch in `\SB_DFFNE.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:922$209'.

Removing empty process `SB_DFFNE.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:922$209'.

Removing empty process `SB_DFFN.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:0$208'.

Removing empty process `SB_DFFN.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:882$207'.

Removing empty process `SB_DFFES.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:0$206'.

Found and cleaned up 1 empty switch in `\SB_DFFES.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:803$203'.

Removing empty process `SB_DFFES.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:803$203'.

Removing empty process `SB_DFFESS.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:0$202'.

Found and cleaned up 2 empty switches in `\SB_DFFESS.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:742$196'.

Removing empty process `SB_DFFESS.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:742$196'.

Removing empty process `SB_DFFER.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:0$195'.

Found and cleaned up 1 empty switch in `\SB_DFFER.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:662$192'.

Removing empty process `SB_DFFER.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:662$192'.

Removing empty process `SB_DFFESR.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:0$191'.

Found and cleaned up 2 empty switches in `\SB_DFFESR.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:601$185'.

Removing empty process `SB_DFFESR.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:601$185'.

Removing empty process `SB_DFFS.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:0$184'.

Removing empty process `SB_DFFS.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:527$182'.

Removing empty process `SB_DFFSS.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:0$181'.

Found and cleaned up 1 empty switch in `\SB_DFFSS.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:477$179'.

Removing empty process `SB_DFFSS.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:477$179'.

Removing empty process `SB_DFFR.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:0$178'.

Removing empty process `SB_DFFR.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:406$176'.

Removing empty process `SB_DFFSR.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:0$175'.

Found and cleaned up 1 empty switch in `\SB_DFFSR.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:356$173'.

Removing empty process `SB_DFFSR.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:356$173'.

Removing empty process `SB_DFFE.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:0$172'.

Found and cleaned up 1 empty switch in `\SB_DFFE.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:311$171'.

Removing empty process `SB_DFFE.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:311$171'.

Removing empty process `SB_DFF.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:0$170'.

Removing empty process `SB_DFF.$proc$/usr/local/bin/../share/yosys/ice40/cells_sim.v:271$169'.

Cleaned up 18 empty switches.

2.4.12. Executing OPT_EXPR pass (perform const folding).

Optimizing module top.

2.5. Executing FLATTEN pass (flatten design).

2.6. Executing TRIBUF pass.

2.7. Executing DEMINOUT pass (demote inout ports to input or output).

2.8. Executing OPT_EXPR pass (perform const folding).

Optimizing module top.

2.9. Executing OPT_CLEAN pass (remove unused cells and wires).

Finding unused cells or wires in module \top..

2.10. Executing CHECK pass (checking for obvious problems).

Checking module top...

Found and reported 0 problems.

2.11. Executing OPT pass (performing simple optimizations).

2.11.1. Executing OPT_EXPR pass (perform const folding).

Optimizing module top.

2.11.2. Executing OPT_MERGE pass (detect identical cells).

Finding identical cells in module `\top'.

Removed a total of 0 cells.

2.11.3. Executing OPT_MUXTREE pass (detect dead branches in mux trees).

Running muxtree optimizer on module \top..

Creating internal representation of mux trees.

No muxes found in this module.

Removed 0 multiplexer ports.

2.11.4. Executing OPT_REDUCE pass (consolidate $*mux and $reduce_* inputs).

Optimizing cells in module \top.

Performed a total of 0 changes.

2.11.5. Executing OPT_MERGE pass (detect identical cells).

Finding identical cells in module `\top'.

Removed a total of 0 cells.

2.11.6. Executing OPT_DFF pass (perform DFF optimizations).

2.11.7. Executing OPT_CLEAN pass (remove unused cells and wires).

Finding unused cells or wires in module \top..

2.11.8. Executing OPT_EXPR pass (perform const folding).

Optimizing module top.

2.11.9. Finished OPT passes. (There is nothing left to do.)

2.12. Executing FSM pass (extract and optimize FSM).

2.12.1. Executing FSM_DETECT pass (finding FSMs in design).

2.12.2. Executing FSM_EXTRACT pass (extracting FSM from design).

2.12.3. Executing FSM_OPT pass (simple optimizations of FSMs).

2.12.4. Executing OPT_CLEAN pass (remove unused cells and wires).

Finding unused cells or wires in module \top..

2.12.5. Executing FSM_OPT pass (simple optimizations of FSMs).

2.12.6. Executing FSM_RECODE pass (re-assigning FSM state encoding).

2.12.7. Executing FSM_INFO pass (dumping all available information on FSM cells).

2.12.8. Executing FSM_MAP pass (mapping FSMs to basic logic).

2.13. Executing OPT pass (performing simple optimizations).

2.13.1. Executing OPT_EXPR pass (perform const folding).

Optimizing module top.

2.13.2. Executing OPT_MERGE pass (detect identical cells).

Finding identical cells in module `\top'.

Removed a total of 0 cells.

2.13.3. Executing OPT_MUXTREE pass (detect dead branches in mux trees).

Running muxtree optimizer on module \top..

Creating internal representation of mux trees.

No muxes found in this module.

Removed 0 multiplexer ports.

2.13.4. Executing OPT_REDUCE pass (consolidate $*mux and $reduce_* inputs).

Optimizing cells in module \top.

Performed a total of 0 changes.

2.13.5. Executing OPT_MERGE pass (detect identical cells).

Finding identical cells in module `\top'.

Removed a total of 0 cells.

2.13.6. Executing OPT_DFF pass (perform DFF optimizations).

2.13.7. Executing OPT_CLEAN pass (remove unused cells and wires).

Finding unused cells or wires in module \top..

2.13.8. Executing OPT_EXPR pass (perform const folding).

Optimizing module top.

2.13.9. Finished OPT passes. (There is nothing left to do.)

2.14. Executing WREDUCE pass (reducing word size of cells).

2.15. Executing PEEPOPT pass (run peephole optimizers).

2.16. Executing OPT_CLEAN pass (remove unused cells and wires).

Finding unused cells or wires in module \top..

2.17. Executing SHARE pass (SAT-based resource sharing).

2.18. Executing TECHMAP pass (map to technology primitives).

2.18.1. Executing Verilog-2005 frontend: /usr/local/bin/../share/yosys/cmp2lut.v

Parsing Verilog input from `/usr/local/bin/../share/yosys/cmp2lut.v' to AST representation.

Generating RTLIL representation for module `\_90_lut_cmp_'.

Successfully finished Verilog frontend.

2.18.2. Continuing TECHMAP pass.

No more expansions possible.

<suppressed ~6 debug messages>

2.19. Executing OPT_EXPR pass (perform const folding).

Optimizing module top.

2.20. Executing OPT_CLEAN pass (remove unused cells and wires).

Finding unused cells or wires in module \top..

2.21. Executing ALUMACC pass (create $alu and $macc cells).

Extracting $alu and $macc cells in module top:

created 0 $alu and 0 $macc cells.

2.22. Executing OPT pass (performing simple optimizations).

2.22.1. Executing OPT_EXPR pass (perform const folding).

Optimizing module top.

2.22.2. Executing OPT_MERGE pass (detect identical cells).

Finding identical cells in module `\top'.

Removed a total of 0 cells.

2.22.3. Executing OPT_MUXTREE pass (detect dead branches in mux trees).

Running muxtree optimizer on module \top..

Creating internal representation of mux trees.

No muxes found in this module.

Removed 0 multiplexer ports.

2.22.4. Executing OPT_REDUCE pass (consolidate $*mux and $reduce_* inputs).

Optimizing cells in module \top.

Performed a total of 0 changes.

2.22.5. Executing OPT_MERGE pass (detect identical cells).

Finding identical cells in module `\top'.

Removed a total of 0 cells.

2.22.6. Executing OPT_DFF pass (perform DFF optimizations).

2.22.7. Executing OPT_CLEAN pass (remove unused cells and wires).

Finding unused cells or wires in module \top..

2.22.8. Executing OPT_EXPR pass (perform const folding).

Optimizing module top.

2.22.9. Finished OPT passes. (There is nothing left to do.)

2.23. Executing MEMORY pass.

2.23.1. Executing OPT_MEM pass (optimize memories).

Performed a total of 0 transformations.

2.23.2. Executing OPT_MEM_PRIORITY pass (removing unnecessary memory write priority relations).

Performed a total of 0 transformations.

2.23.3. Executing OPT_MEM_FEEDBACK pass (finding memory read-to-write feedback paths).

2.23.4. Executing MEMORY_BMUX2ROM pass (converting muxes to ROMs).

2.23.5. Executing MEMORY_DFF pass (merging $dff cells to $memrd).

2.23.6. Executing OPT_CLEAN pass (remove unused cells and wires).

Finding unused cells or wires in module \top..

2.23.7. Executing MEMORY_SHARE pass (consolidating $memrd/$memwr cells).

2.23.8. Executing OPT_MEM_WIDEN pass (optimize memories where all ports are wide).

Performed a total of 0 transformations.

2.23.9. Executing OPT_CLEAN pass (remove unused cells and wires).

Finding unused cells or wires in module \top..

2.23.10. Executing MEMORY_COLLECT pass (generating $mem cells).

2.24. Executing OPT_CLEAN pass (remove unused cells and wires).

Finding unused cells or wires in module \top..

2.25. Executing MEMORY_LIBMAP pass (mapping memories to cells).

2.26. Executing TECHMAP pass (map to technology primitives).

2.26.1. Executing Verilog-2005 frontend: /usr/local/bin/../share/yosys/ice40/brams_map.v

Parsing Verilog input from `/usr/local/bin/../share/yosys/ice40/brams_map.v' to AST representation.

Generating RTLIL representation for module `\$__ICE40_RAM4K_'.

Successfully finished Verilog frontend.

2.26.2. Executing Verilog-2005 frontend: /usr/local/bin/../share/yosys/ice40/spram_map.v

Parsing Verilog input from `/usr/local/bin/../share/yosys/ice40/spram_map.v' to AST representation.

Generating RTLIL representation for module `\$__ICE40_SPRAM_'.

Successfully finished Verilog frontend.

2.26.3. Continuing TECHMAP pass.

No more expansions possible.

<suppressed ~4 debug messages>

2.27. Executing ICE40_BRAMINIT pass.

2.28. Executing OPT pass (performing simple optimizations).

2.28.1. Executing OPT_EXPR pass (perform const folding).

Optimizing module top.

2.28.2. Executing OPT_MERGE pass (detect identical cells).

Finding identical cells in module `\top'.

Removed a total of 0 cells.

2.28.3. Executing OPT_DFF pass (perform DFF optimizations).

2.28.4. Executing OPT_CLEAN pass (remove unused cells and wires).

Finding unused cells or wires in module \top..

2.28.5. Finished fast OPT passes.

2.29. Executing MEMORY_MAP pass (converting memories to logic and flip-flops).

2.30. Executing OPT pass (performing simple optimizations).

2.30.1. Executing OPT_EXPR pass (perform const folding).

Optimizing module top.

2.30.2. Executing OPT_MERGE pass (detect identical cells).

Finding identical cells in module `\top'.

Removed a total of 0 cells.

2.30.3. Executing OPT_MUXTREE pass (detect dead branches in mux trees).

Running muxtree optimizer on module \top..

Creating internal representation of mux trees.

No muxes found in this module.

Removed 0 multiplexer ports.

2.30.4. Executing OPT_REDUCE pass (consolidate $*mux and $reduce_* inputs).

Optimizing cells in module \top.

Performed a total of 0 changes.

2.30.5. Executing OPT_MERGE pass (detect identical cells).

Finding identical cells in module `\top'.

Removed a total of 0 cells.

2.30.6. Executing OPT_DFF pass (perform DFF optimizations).

2.30.7. Executing OPT_CLEAN pass (remove unused cells and wires).

Finding unused cells or wires in module \top..

2.30.8. Executing OPT_EXPR pass (perform const folding).

Optimizing module top.

2.30.9. Finished OPT passes. (There is nothing left to do.)

2.31. Executing ICE40_WRAPCARRY pass (wrap carries).

2.32. Executing TECHMAP pass (map to technology primitives).

2.32.1. Executing Verilog-2005 frontend: /usr/local/bin/../share/yosys/techmap.v

Parsing Verilog input from `/usr/local/bin/../share/yosys/techmap.v' to AST representation.

Generating RTLIL representation for module `\_90_simplemap_bool_ops'.

Generating RTLIL representation for module `\_90_simplemap_reduce_ops'.

Generating RTLIL representation for module `\_90_simplemap_logic_ops'.

Generating RTLIL representation for module `\_90_simplemap_compare_ops'.

Generating RTLIL representation for module `\_90_simplemap_various'.

Generating RTLIL representation for module `\_90_simplemap_registers'.

Generating RTLIL representation for module `\_90_shift_ops_shr_shl_sshl_sshr'.

Generating RTLIL representation for module `\_90_shift_shiftx'.

Generating RTLIL representation for module `\_90_fa'.

Generating RTLIL representation for module `\_90_lcu_brent_kung'.

Generating RTLIL representation for module `\_90_alu'.

Generating RTLIL representation for module `\_90_macc'.

Generating RTLIL representation for module `\_90_alumacc'.

Generating RTLIL representation for module `\$__div_mod_u'.

Generating RTLIL representation for module `\$__div_mod_trunc'.

Generating RTLIL representation for module `\_90_div'.

Generating RTLIL representation for module `\_90_mod'.

Generating RTLIL representation for module `\$__div_mod_floor'.

Generating RTLIL representation for module `\_90_divfloor'.

Generating RTLIL representation for module `\_90_modfloor'.

Generating RTLIL representation for module `\_90_pow'.

Generating RTLIL representation for module `\_90_pmux'.

Generating RTLIL representation for module `\_90_demux'.

Generating RTLIL representation for module `\_90_lut'.

Successfully finished Verilog frontend.

2.32.2. Executing Verilog-2005 frontend: /usr/local/bin/../share/yosys/ice40/arith_map.v

Parsing Verilog input from `/usr/local/bin/../share/yosys/ice40/arith_map.v' to AST representation.

Generating RTLIL representation for module `\_80_ice40_alu'.

Successfully finished Verilog frontend.

2.32.3. Continuing TECHMAP pass.

No more expansions possible.

<suppressed ~73 debug messages>

2.33. Executing OPT pass (performing simple optimizations).

2.33.1. Executing OPT_EXPR pass (perform const folding).

Optimizing module top.

2.33.2. Executing OPT_MERGE pass (detect identical cells).

Finding identical cells in module `\top'.

Removed a total of 0 cells.

2.33.3. Executing OPT_DFF pass (perform DFF optimizations).

2.33.4. Executing OPT_CLEAN pass (remove unused cells and wires).

Finding unused cells or wires in module \top..

2.33.5. Finished fast OPT passes.

2.34. Executing ICE40_OPT pass (performing simple optimizations).

2.34.1. Running ICE40 specific optimizations.

2.34.2. Executing OPT_EXPR pass (perform const folding).

Optimizing module top.

2.34.3. Executing OPT_MERGE pass (detect identical cells).

Finding identical cells in module `\top'.

Removed a total of 0 cells.

2.34.4. Executing OPT_DFF pass (perform DFF optimizations).

2.34.5. Executing OPT_CLEAN pass (remove unused cells and wires).

Finding unused cells or wires in module \top..

2.34.6. Finished OPT passes. (There is nothing left to do.)

2.35. Executing DFFLEGALIZE pass (convert FFs to types supported by the target).

2.36. Executing TECHMAP pass (map to technology primitives).

2.36.1. Executing Verilog-2005 frontend: /usr/local/bin/../share/yosys/ice40/ff_map.v

Parsing Verilog input from `/usr/local/bin/../share/yosys/ice40/ff_map.v' to AST representation.

Generating RTLIL representation for module `\$_DFF_N_'.

Generating RTLIL representation for module `\$_DFF_P_'.

Generating RTLIL representation for module `\$_DFFE_NP_'.

Generating RTLIL representation for module `\$_DFFE_PP_'.

Generating RTLIL representation for module `\$_DFF_NP0_'.

Generating RTLIL representation for module `\$_DFF_NP1_'.

Generating RTLIL representation for module `\$_DFF_PP0_'.

Generating RTLIL representation for module `\$_DFF_PP1_'.

Generating RTLIL representation for module `\$_DFFE_NP0P_'.

Generating RTLIL representation for module `\$_DFFE_NP1P_'.

Generating RTLIL representation for module `\$_DFFE_PP0P_'.

Generating RTLIL representation for module `\$_DFFE_PP1P_'.

Generating RTLIL representation for module `\$_SDFF_NP0_'.

Generating RTLIL representation for module `\$_SDFF_NP1_'.

Generating RTLIL representation for module `\$_SDFF_PP0_'.

Generating RTLIL representation for module `\$_SDFF_PP1_'.

Generating RTLIL representation for module `\$_SDFFCE_NP0P_'.

Generating RTLIL representation for module `\$_SDFFCE_NP1P_'.

Generating RTLIL representation for module `\$_SDFFCE_PP0P_'.

Generating RTLIL representation for module `\$_SDFFCE_PP1P_'.

Successfully finished Verilog frontend.

2.36.2. Continuing TECHMAP pass.

No more expansions possible.

<suppressed ~22 debug messages>

2.37. Executing OPT_EXPR pass (perform const folding).

Optimizing module top.

2.38. Executing SIMPLEMAP pass (map simple cells to gate primitives).

2.39. Executing ICE40_OPT pass (performing simple optimizations).

2.39.1. Running ICE40 specific optimizations.

2.39.2. Executing OPT_EXPR pass (perform const folding).

Optimizing module top.

2.39.3. Executing OPT_MERGE pass (detect identical cells).

Finding identical cells in module `\top'.

Removed a total of 0 cells.

2.39.4. Executing OPT_DFF pass (perform DFF optimizations).

2.39.5. Executing OPT_CLEAN pass (remove unused cells and wires).

Finding unused cells or wires in module \top..

2.39.6. Finished OPT passes. (There is nothing left to do.)

2.40. Executing TECHMAP pass (map to technology primitives).

2.40.1. Executing Verilog-2005 frontend: /usr/local/bin/../share/yosys/ice40/latches_map.v

Parsing Verilog input from `/usr/local/bin/../share/yosys/ice40/latches_map.v' to AST representation.

Generating RTLIL representation for module `\$_DLATCH_N_'.

Generating RTLIL representation for module `\$_DLATCH_P_'.

Successfully finished Verilog frontend.

2.40.2. Continuing TECHMAP pass.

No more expansions possible.

<suppressed ~4 debug messages>

2.41. Executing Verilog-2005 frontend: /usr/local/bin/../share/yosys/ice40/abc9_model.v

Parsing Verilog input from `/usr/local/bin/../share/yosys/ice40/abc9_model.v' to AST representation.

Generating RTLIL representation for module `$__ICE40_CARRY_WRAPPER'.

Successfully finished Verilog frontend.

2.42. Executing ABC9 pass.

2.42.1. Executing ABC9_OPS pass (helper functions for ABC9).

2.42.2. Executing ABC9_OPS pass (helper functions for ABC9).

2.42.3. Executing SCC pass (detecting logic loops).

Found 0 SCCs in module top.

Found 0 SCCs.

2.42.4. Executing ABC9_OPS pass (helper functions for ABC9).

2.42.5. Executing PROC pass (convert processes to netlists).

2.42.5.1. Executing PROC_CLEAN pass (remove empty switches from decision trees).

Cleaned up 0 empty switches.

2.42.5.2. Executing PROC_RMDEAD pass (remove dead branches from decision trees).

Removed a total of 0 dead cases.

2.42.5.3. Executing PROC_PRUNE pass (remove redundant assignments in processes).

Removed 0 redundant assignments.

Promoted 0 assignments to connections.

2.42.5.4. Executing PROC_INIT pass (extract init attributes).

2.42.5.5. Executing PROC_ARST pass (detect async resets in processes).

2.42.5.6. Executing PROC_ROM pass (convert switches to ROMs).

Converted 0 switches.

2.42.5.7. Executing PROC_MUX pass (convert decision trees to multiplexers).

2.42.5.8. Executing PROC_DLATCH pass (convert process syncs to latches).

2.42.5.9. Executing PROC_DFF pass (convert process syncs to FFs).

2.42.5.10. Executing PROC_MEMWR pass (convert process memory writes to cells).

2.42.5.11. Executing PROC_CLEAN pass (remove empty switches from decision trees).

Cleaned up 0 empty switches.

2.42.5.12. Executing OPT_EXPR pass (perform const folding).

2.42.6. Executing TECHMAP pass (map to technology primitives).

2.42.6.1. Executing Verilog-2005 frontend: /usr/local/bin/../share/yosys/techmap.v

Parsing Verilog input from `/usr/local/bin/../share/yosys/techmap.v' to AST representation.

Generating RTLIL representation for module `\_90_simplemap_bool_ops'.

Generating RTLIL representation for module `\_90_simplemap_reduce_ops'.

Generating RTLIL representation for module `\_90_simplemap_logic_ops'.

Generating RTLIL representation for module `\_90_simplemap_compare_ops'.

Generating RTLIL representation for module `\_90_simplemap_various'.

Generating RTLIL representation for module `\_90_simplemap_registers'.

Generating RTLIL representation for module `\_90_shift_ops_shr_shl_sshl_sshr'.

Generating RTLIL representation for module `\_90_shift_shiftx'.

Generating RTLIL representation for module `\_90_fa'.

Generating RTLIL representation for module `\_90_lcu_brent_kung'.

Generating RTLIL representation for module `\_90_alu'.

Generating RTLIL representation for module `\_90_macc'.

Generating RTLIL representation for module `\_90_alumacc'.

Generating RTLIL representation for module `\$__div_mod_u'.

Generating RTLIL representation for module `\$__div_mod_trunc'.

Generating RTLIL representation for module `\_90_div'.

Generating RTLIL representation for module `\_90_mod'.

Generating RTLIL representation for module `\$__div_mod_floor'.

Generating RTLIL representation for module `\_90_divfloor'.

Generating RTLIL representation for module `\_90_modfloor'.

Generating RTLIL representation for module `\_90_pow'.

Generating RTLIL representation for module `\_90_pmux'.

Generating RTLIL representation for module `\_90_demux'.

Generating RTLIL representation for module `\_90_lut'.

Successfully finished Verilog frontend.

2.42.6.2. Continuing TECHMAP pass.

No more expansions possible.

<suppressed ~125 debug messages>

2.42.7. Executing OPT pass (performing simple optimizations).

2.42.7.1. Executing OPT_EXPR pass (perform const folding).

2.42.7.2. Executing OPT_MERGE pass (detect identical cells).

Removed a total of 0 cells.

2.42.7.3. Executing OPT_MUXTREE pass (detect dead branches in mux trees).

Removed 0 multiplexer ports.

2.42.7.4. Executing OPT_REDUCE pass (consolidate $*mux and $reduce_* inputs).

Performed a total of 0 changes.

2.42.7.5. Executing OPT_MERGE pass (detect identical cells).

Removed a total of 0 cells.

2.42.7.6. Executing OPT_DFF pass (perform DFF optimizations).

2.42.7.7. Executing OPT_CLEAN pass (remove unused cells and wires).

2.42.7.8. Executing OPT_EXPR pass (perform const folding).

2.42.7.9. Finished OPT passes. (There is nothing left to do.)

2.42.8. Executing TECHMAP pass (map to technology primitives).

2.42.8.1. Executing Verilog-2005 frontend: /usr/local/bin/../share/yosys/abc9_map.v

Parsing Verilog input from `/usr/local/bin/../share/yosys/abc9_map.v' to AST representation.

Successfully finished Verilog frontend.

2.42.8.2. Continuing TECHMAP pass.

No more expansions possible.

<suppressed ~2 debug messages>

2.42.9. Executing Verilog-2005 frontend: /usr/local/bin/../share/yosys/abc9_model.v

Parsing Verilog input from `/usr/local/bin/../share/yosys/abc9_model.v' to AST representation.

Generating RTLIL representation for module `$__ABC9_DELAY'.

Generating RTLIL representation for module `$__ABC9_SCC_BREAKER'.

Generating RTLIL representation for module `$__DFF_N__$abc9_flop'.

Generating RTLIL representation for module `$__DFF_P__$abc9_flop'.

Successfully finished Verilog frontend.

2.42.10. Executing ABC9_OPS pass (helper functions for ABC9).

2.42.11. Executing ABC9_OPS pass (helper functions for ABC9).

2.42.12. Executing ABC9_OPS pass (helper functions for ABC9).

<suppressed ~2 debug messages>

2.42.13. Executing AIGMAP pass (map logic to AIG).

2.42.13.1. Executing ABC9_OPS pass (helper functions for ABC9).

2.42.13.2. Executing ABC9_OPS pass (helper functions for ABC9).

2.42.13.3. Executing XAIGER backend.

<suppressed ~5 debug messages>

Extracted 0 AND gates and 7 wires from module `top' to a netlist network with 0 inputs and 5 outputs.

2.42.13.4. Executing ABC9_EXE pass (technology mapping using ABC9).

2.42.13.5. Executing ABC9.

Running ABC command: "<yosys-exe-dir>/yosys-abc" -s -f <abc-temp-dir>/abc.script 2>&1

ABC: ABC command line: "source <abc-temp-dir>/abc.script".

ABC:

ABC: + read_lut <abc-temp-dir>/input.lut

ABC: + read_box <abc-temp-dir>/input.box

ABC: + &read <abc-temp-dir>/input.xaig

ABC: + &ps

ABC: <abc-temp-dir>/input : i/o = 0/ 5 and = 0 lev = 0 (0.00) mem = 0.00 MB box = 0 bb = 0

ABC: + &scorr

ABC: Warning: The network is combinational.

ABC: + &sweep

ABC: + &dc2

ABC: + &dch -f

ABC: + &ps

ABC: <abc-temp-dir>/input : i/o = 0/ 5 and = 0 lev = 0 (0.00) mem = 0.00 MB ch = 0 box = 0 bb = 0

ABC: + &if -W 250 -v

ABC: K = 4. Memory (bytes): Truth = 0. Cut = 52. Obj = 136. Set = 564. CutMin = no

ABC: Node = 0. Ch = 0. Total mem = 0.00 MB. Peak cut mem = 0.00 MB.

ABC: P: Del = -100000000.00. Ar = 0.0. Edge = 0. Cut = 0. T = 0.00 sec

ABC: P: Del = -100000000.00. Ar = 0.0. Edge = 0. Cut = 0. T = 0.00 sec

ABC: P: Del = -100000000.00. Ar = 0.0. Edge = 0. Cut = 0. T = 0.00 sec

ABC: F: Del = -100000000.00. Ar = 0.0. Edge = 0. Cut = 0. T = 0.00 sec

ABC: A: Del = -100000000.00. Ar = 0.0. Edge = 0. Cut = 0. T = 0.00 sec

ABC: A: Del = -100000000.00. Ar = 0.0. Edge = 0. Cut = 0. T = 0.00 sec

ABC: Total time = 0.00 sec

ABC: + &write -n <abc-temp-dir>/output.aig

ABC: + &mfs

ABC: The network is not changed by "&mfs".

ABC: + &ps -l

ABC: <abc-temp-dir>/input : i/o = 0/ 5 and = 0 lev = 0 (0.00) mem = 0.00 MB box = 0 bb = 0

ABC: Mapping (K=0) : lut = 0 edge = 0 lev = 0 (0.00) mem = 0.00 MB

ABC: LUT = 0 : Ave = 0.00

ABC: + &write -n <abc-temp-dir>/output.aig

ABC: + time

ABC: elapse: 0.00 seconds, total: 0.00 seconds

2.42.13.6. Executing AIGER frontend.

<suppressed ~18 debug messages>

Removed 0 unused cells and 2 unused wires.

2.42.13.7. Executing ABC9_OPS pass (helper functions for ABC9).

ABC RESULTS: input signals: 0

ABC RESULTS: output signals: 5

Removing temp directory.

2.42.14. Executing TECHMAP pass (map to technology primitives).

2.42.14.1. Executing Verilog-2005 frontend: /usr/local/bin/../share/yosys/abc9_unmap.v

Parsing Verilog input from `/usr/local/bin/../share/yosys/abc9_unmap.v' to AST representation.

Generating RTLIL representation for module `\$__DFF_x__$abc9_flop'.

Generating RTLIL representation for module `\$__ABC9_SCC_BREAKER'.

Successfully finished Verilog frontend.

2.42.14.2. Continuing TECHMAP pass.

No more expansions possible.

<suppressed ~5 debug messages>

2.43. Executing ICE40_WRAPCARRY pass (wrap carries).

2.44. Executing TECHMAP pass (map to technology primitives).

2.44.1. Executing Verilog-2005 frontend: /usr/local/bin/../share/yosys/ice40/ff_map.v

Parsing Verilog input from `/usr/local/bin/../share/yosys/ice40/ff_map.v' to AST representation.

Generating RTLIL representation for module `\$_DFF_N_'.

Generating RTLIL representation for module `\$_DFF_P_'.

Generating RTLIL representation for module `\$_DFFE_NP_'.

Generating RTLIL representation for module `\$_DFFE_PP_'.

Generating RTLIL representation for module `\$_DFF_NP0_'.

Generating RTLIL representation for module `\$_DFF_NP1_'.

Generating RTLIL representation for module `\$_DFF_PP0_'.

Generating RTLIL representation for module `\$_DFF_PP1_'.

Generating RTLIL representation for module `\$_DFFE_NP0P_'.

Generating RTLIL representation for module `\$_DFFE_NP1P_'.

Generating RTLIL representation for module `\$_DFFE_PP0P_'.

Generating RTLIL representation for module `\$_DFFE_PP1P_'.

Generating RTLIL representation for module `\$_SDFF_NP0_'.

Generating RTLIL representation for module `\$_SDFF_NP1_'.

Generating RTLIL representation for module `\$_SDFF_PP0_'.

Generating RTLIL representation for module `\$_SDFF_PP1_'.

Generating RTLIL representation for module `\$_SDFFCE_NP0P_'.

Generating RTLIL representation for module `\$_SDFFCE_NP1P_'.

Generating RTLIL representation for module `\$_SDFFCE_PP0P_'.

Generating RTLIL representation for module `\$_SDFFCE_PP1P_'.

Successfully finished Verilog frontend.

2.44.2. Continuing TECHMAP pass.

No more expansions possible.

<suppressed ~22 debug messages>

Removed 0 unused cells and 6 unused wires.

2.45. Executing OPT_LUT pass (optimize LUTs).

Discovering LUTs.

Number of LUTs: 0

with \SB_CARRY (#0) 0

with \SB_CARRY (#1) 0

Eliminating LUTs.

Number of LUTs: 0

with \SB_CARRY (#0) 0

with \SB_CARRY (#1) 0

Combining LUTs.

Number of LUTs: 0

with \SB_CARRY (#0) 0

with \SB_CARRY (#1) 0

Eliminated 0 LUTs.

Combined 0 LUTs.

2.46. Executing TECHMAP pass (map to technology primitives).

2.46.1. Executing Verilog-2005 frontend: /usr/local/bin/../share/yosys/ice40/cells_map.v

Parsing Verilog input from `/usr/local/bin/../share/yosys/ice40/cells_map.v' to AST representation.

Generating RTLIL representation for module `\$lut'.

Successfully finished Verilog frontend.

2.46.2. Continuing TECHMAP pass.

No more expansions possible.

<suppressed ~3 debug messages>

2.47. Executing AUTONAME pass.

2.48. Executing HIERARCHY pass (managing design hierarchy).

2.48.1. Analyzing design hierarchy..

Top module: \top

2.48.2. Analyzing design hierarchy..

Top module: \top

Removed 0 unused modules.

2.49. Printing statistics.

=== top ===

Number of wires: 5

Number of wire bits: 5

Number of public wires: 5

Number of public wire bits: 5

Number of ports: 5

Number of port bits: 5

Number of memories: 0

Number of memory bits: 0

Number of processes: 0

Number of cells: 0

2.50. Executing CHECK pass (checking for obvious problems).

Checking module top...

Found and reported 0 problems.

2.51. Executing BLIF backend.

2.52. Executing JSON backend.

End of script. Logfile hash: 3186c3d711, CPU: user 0.63s system 0.02s, MEM: 24.38 MB peak

Yosys 0.40+45 (git sha1 dd2195543, g++ 11.4.0-1ubuntu1~22.04 -fPIC -Os)

Time spent: 69% 20x read_verilog (0 sec), 6% 1x synth_ice40 (0 sec), ...

输出很多,这里简单解释几个要点:

- Verilog 前端解析:

-- Parsing 'top.v' using frontend ' -vlog2k' --

解析 Verilog 文件 top.v 并将其转换为抽象语法树 (AST) 表示。

- synth_ice40 过程:

-- Running command 'synth_ice40 -top top -blif blink_on.blif -json blink_on.json' --

这是专门为 Lattice iCE40 FPGA 进行综合的命令。综合过程中生成了 .blif 和 .json 文件,分别用于逻辑综合中间表示和 JSON 格式的综合输出。

- RTLIL 表示生成:

Generating RTLIL representation for module '\SB_DFF' 等等。

将 Verilog 模块转换为 RTLIL (Register Transfer Level Intermediate Language) 表示,这是一种中间表示,用于后续的综合和优化步骤。

- 技术映射 (TECHMAP) 和优化:

-

2.46. Executing TECHMAP pass (map to technology primitives).

这一阶段将 RTLIL 表示映射到具体的 FPGA 技术原语,例如查找表 (LUT)、触发器等。 -

2.45. Executing OPT_LUT pass (optimize LUTs).

优化查找表以减少逻辑资源使用。

- 层次管理 (HIERARCHY) 和统计:

-

2.48. Executing HIERARCHY pass (managing design hierarchy).

管理设计的层次结构,确定顶层模块并移除未使用的模块。 -

2.49. Printing statistics.

打印设计的统计信息,例如线数、端口数、单元数等。

Copy code

=== top ===

Number of wires: 5

Number of wire bits: 5

Number of public wires: 5

Number of public wire bits: 5

Number of ports: 5

Number of port bits: 5

Number of memories: 0

Number of memory bits: 0

Number of processes: 0

Number of cells: 0

- 检查 (CHECK):

2.50. Executing CHECK pass (checking for obvious problems).

检查设计中的明显问题,确保综合后的设计没有错误。

- 生成 BLIF 和 JSON:

- 2.51. Executing BLIF backend.

- 2.52. Executing JSON backend.

- 生成 BLIF 和 JSON 格式的输出文件,这些文件可以用于后续的 FPGA 实现步骤。

这些步骤和信息表明 Yosys 对 top.v 进行了综合,并生成了相应的输出文件,同时进行了各种优化和检查,以确保设计的正确性和效率 。

实现(implementation)

使用nextpnr-ice40进行实现:

$ nextpnr-ice40 --hx1k --json blink_on.json --pcf pinmap.pcf --asc blink_on.asc

该命令会将综合后的设计映射到具体的硬件上,并生成相应的位流文件。以下是命令输出:

Warning: Use of default value for --package is deprecated. Please add '--package tq144' to arguments.

Info: constrained 'D1' to bel 'X13/Y12/io1'

Info: constrained 'D2' to bel 'X13/Y12/io0'

Info: constrained 'D3' to bel 'X13/Y11/io1'

Info: constrained 'D4' to bel 'X13/Y11/io0'

Info: constrained 'D5' to bel 'X13/Y9/io1'

Info: Packing constants..

Info: Packing IOs..

Info: Packing LUT-FFs..

Info: 0 LCs used as LUT4 only

Info: 0 LCs used as LUT4 and DFF

Info: Packing non-LUT FFs..

Info: 0 LCs used as DFF only

Info: Packing carries..

Info: 0 LCs used as CARRY only

Info: Packing indirect carry+LUT pairs...

Info: 0 LUTs merged into carry LCs

Info: Packing RAMs..

Info: Placing PLLs..

Info: Packing special functions..

Info: Packing PLLs..

Info: Promoting globals..

Info: Constraining chains...

Info: 0 LCs used to legalise carry chains.

Info: Checksum: 0xbe76442d

Info: Device utilisation:

Info: ICESTORM_LC: 1/ 1280 0%

Info: ICESTORM_RAM: 0/ 16 0%

Info: SB_IO: 5/ 112 4%

Info: SB_GB: 0/ 8 0%

Info: ICESTORM_PLL: 0/ 1 0%

Info: SB_WARMBOOT: 0/ 1 0%

Info: Placed 5 cells based on constraints.

Info: Creating initial analytic placement for 1 cells, random placement wirelen = 11.

Info: at initial placer iter 0, wirelen = 3

Info: at initial placer iter 1, wirelen = 3

Info: at initial placer iter 2, wirelen = 3

Info: at initial placer iter 3, wirelen = 3

Info: Running main analytical placer, max placement attempts per cell = 10000.

Info: at iteration #1, type ICESTORM_LC: wirelen solved = 3, spread = 3, legal = 4; time = 0.00s

Info: at iteration #2, type ICESTORM_LC: wirelen solved = 4, spread = 4, legal = 4; time = 0.00s

Info: HeAP Placer Time: 0.00s

Info: of which solving equations: 0.00s

Info: of which spreading cells: 0.00s

Info: of which strict legalisation: 0.00s

Info: Running simulated annealing placer for refinement.

Info: at iteration #1: temp = 0.000000, timing cost = 0, wirelen = 4

Info: at iteration #2: temp = 0.000000, timing cost = 0, wirelen = 4

Info: SA placement time 0.00s

Info: No Fmax available; no interior timing paths found in design.

Info: Checksum: 0xcd48b0e8

Info: Routing..

Info: Setting up routing queue.

Info: Routing 5 arcs.

Info: | (re-)routed arcs | delta | remaining| time spent |

Info: IterCnt | w/ripup wo/ripup | w/r wo/r | arcs| batch(sec) total(sec)|

Info: 5 | 0 5 | 0 5 | 0| 0.00 0.00|

Info: Routing complete.

Info: Router1 time 0.00s

Info: Checksum: 0xabe39d2c

Info: No Fmax available; no interior timing paths found in design.

1 warning, 0 errors

Info: Program finished normally.

时序分析(可选)

- 可以使用icetime进行时序分析,以确保设计满足时序要求:

$ icetime -tmd hx1k blink_on.asc

输出如下:

// Reading input .asc file..

// Reading 1k chipdb file..

// Creating timing netlist..

icetime topological timing analysis report

==========================================

Info: max_span_hack is enabled: estimate is conservative.

Report for critical path:

-------------------------

pre_io_13_11_0 (PRE_IO) [clk] -> PADOUT: 0.240 ns

0.240 ns io_pad_13_11_0_din

Total number of logic levels: 0

Total path delay: 0.24 ns (4161.98 MHz)

烧写

最后一步是将生成的位流文件烧写到ICESTICK上,使用iceprog工具:

$ iceprog blink_on.bin

输出如下:

init..

cdone: high

reset..

cdone: low

flash ID: 0x20 0xBA 0x16 0x10 0x00 0x00 0x23 0x72 0x21 0x19 0x05 0x00 0x58 0x00 0x21 0x16 0x07 0x17 0xCE 0x6D

file size: 32220

erase 64kB sector at 0x000000..

programming..

done.

reading..

VERIFY OK

cdone: high

Bye.

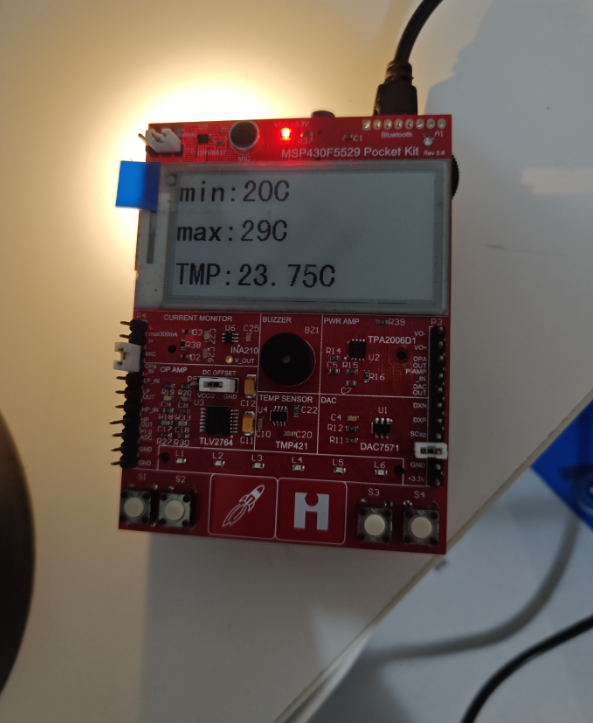

效果

![[数据集][目标检测]老鼠检测数据集VOC+YOLO格式4107张1类别](https://img-blog.csdnimg.cn/direct/9290e202057b41ab83eae6cfd8f50f0e.png)