FPGA大型设计中推荐使用同步时序电路,同步时序电路基于时钟触发沿设计,对时钟的周期、占空比、延时和抖动有更高的要求。为满足时序的要求,一般采用全局时钟资源驱动设计的主时钟,FPGA的主时钟一般使用全铜层工艺实现,并设计了专用时钟缓冲与驱动结构。

缓冲和驱动

缓冲

输入输出缓冲,主要用于片外输入时钟或者片外差分输入的信号。

差分信号和差分时钟进入片内后如果不经过IBUFGDS、IBUFDS缓冲就无法直接处理

驱动

当信号扇出过大时可以通过加BUFG增加信号稳定性

过一次BUFG有10ns左右的延时,但是通过BUFG后输出到片上所有单元的延时都可以忽略不记

Buffer的类别和作用

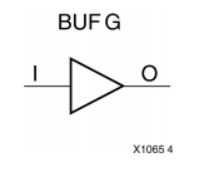

BUFG

BUFG是一个高扇出缓冲器,将信号连接到全局布线资源上,使得信号的延时和抖动最小

通常用于时钟网络以及其他高扇出网络,比如复位和使能信号

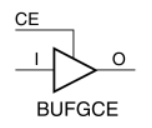

BUFGCE

BUFGCE具有单门控输入的全局时钟缓冲器,CE高电平有效

当CE为低电平时 O 端口输出0

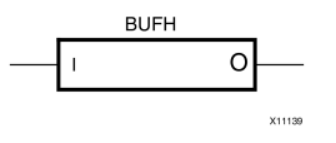

BUFH

BUFH原语允许直接访问BUFG的时钟区域入口,允许访问全局时钟网络中未使用的部分,作为高速低偏移的本地路由资源(单时钟区域)

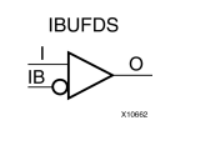

IBUFDS

支持低压差分信号输入的缓冲器,有两个输入的端口,一个为主端口一个为从端口,输入的信号相位相反

IBUFDS_GTE2

7系列器件中的Gbit 收发器输入缓冲,REFCLK应连接到串行收发器的专用参考时钟输入引脚

OBUFDS

差分信号输出缓冲器