目录

1. 简介

2. 详细分析

2.1 使用场景区别

2.2 ap_continue 行为详解

2.3 ap_ctrl_chain 行为详解

3. 总结

1. 简介

块级控制协议允许硬件模块表明:

- 何时可以开始处理数据。

- 何时完成了数据处理。

- 以及何时处于空闲状态,准备接受新的数据输入。

这些信号用于本模块在与其他硬件组件交互时,同步和控制硬件模块的行为。例如,ap_start信号可以触发模块开始执行操作,而ap_done信号则表明操作已经完成,输出数据可以被读取。

区分端口级I/O协议,负责管理数据的实际输入和输出。端口级I/O协议涉及到如何将数据传递给模块的输入端口,以及如何从模块的输出端口获取数据。

块级控制协议是Vitis HLS设计中的一个关键组成部分,它确保了硬件模块能够有效地同步和控制其操作流程。

2. 详细分析

2.1 使用场景区别

ap_ctrl_chain 协议和 ap_ctrl_hs 协议

- 这两种协议用于控制驱动的TLP。

- 它们可以用于顺序执行和流水线执行。

- ap_ctrl_chain 协议与 ap_ctrl_hs 类似,但它增加了一个 ap_continue 信号,允许下游模块控制上游模块的运行或终止。

ap_ctrl_none 协议

对于数据驱动的TLP,必须使用 ap_ctrl_none 协议。

ap_ctrl_none 没有握手信号 ap_start、ap_idle、ap_ready 和 ap_done。这允许硬件模块完全由数据可用性来驱动,而不是由控制信号来驱动。

注:可以观察到 ap_ctrl_none 有 ap_start、ap_idle、ap_ready 和 ap_done 等信号,但会被设为高电平并且会被优化掉。

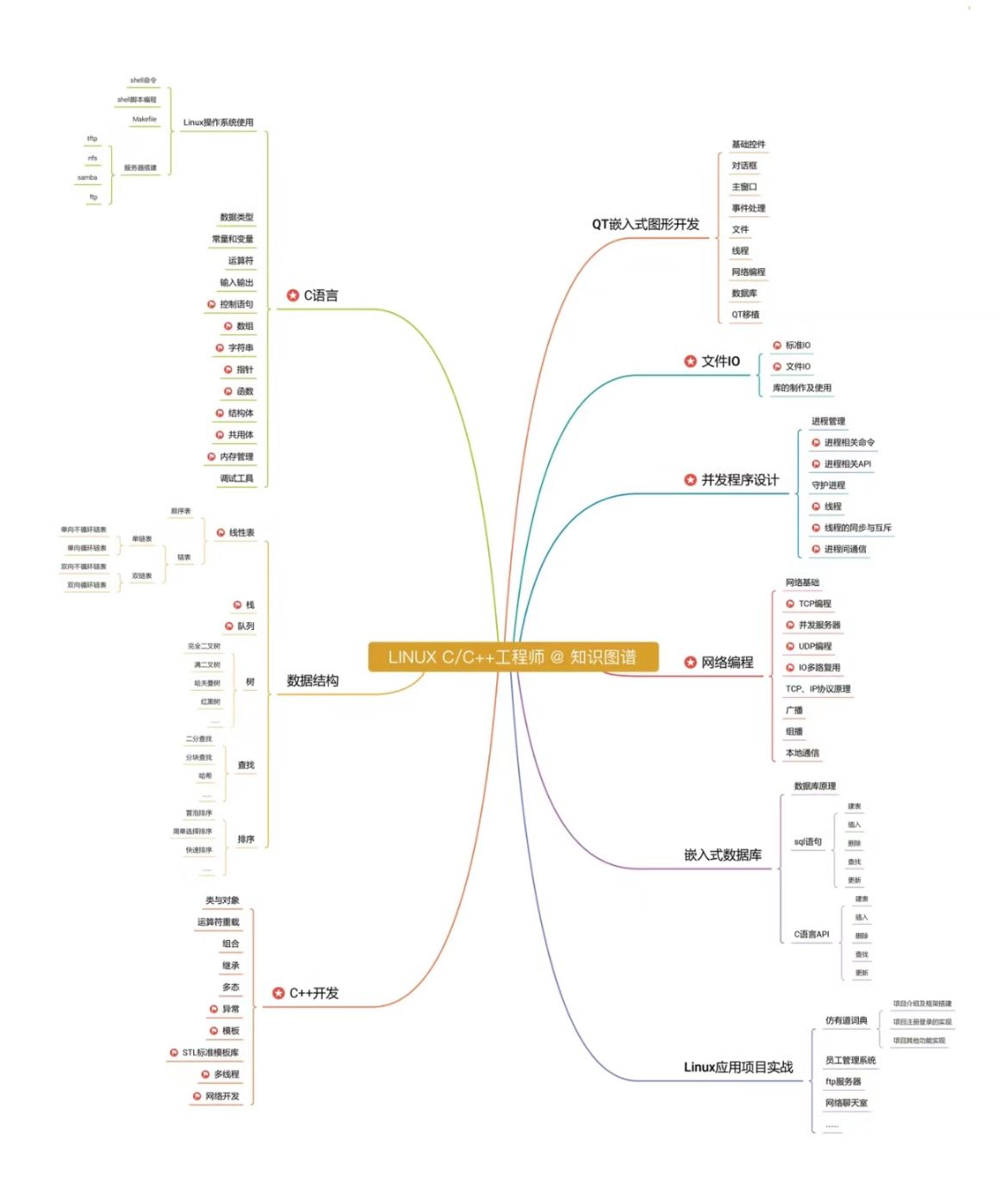

2.2 ap_continue 行为详解

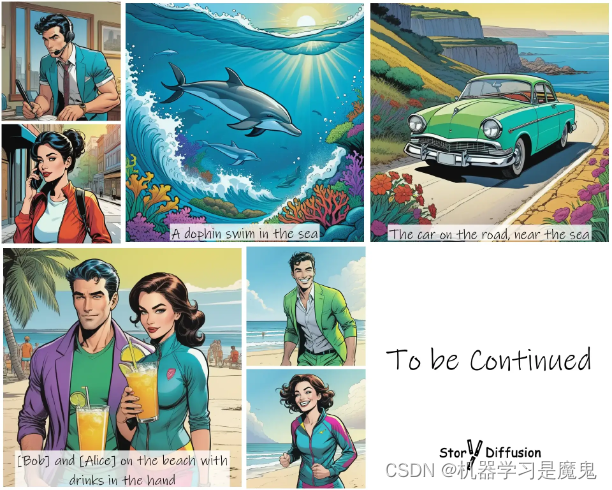

使用示例说明,ap_continue 信号的行为:

- 内核的第 1 项传输事务完成后,第 2 项传输事务立即启动,因为 ap_continue 为高电平状态,且 ap_done 为高电平状态。

- 内核的第 2 项传输事务结束后将停止,直至 ap_continue 断言为高电平有效为止。

图片引用自《UG1399》

2.3 ap_ctrl_chain 行为详解

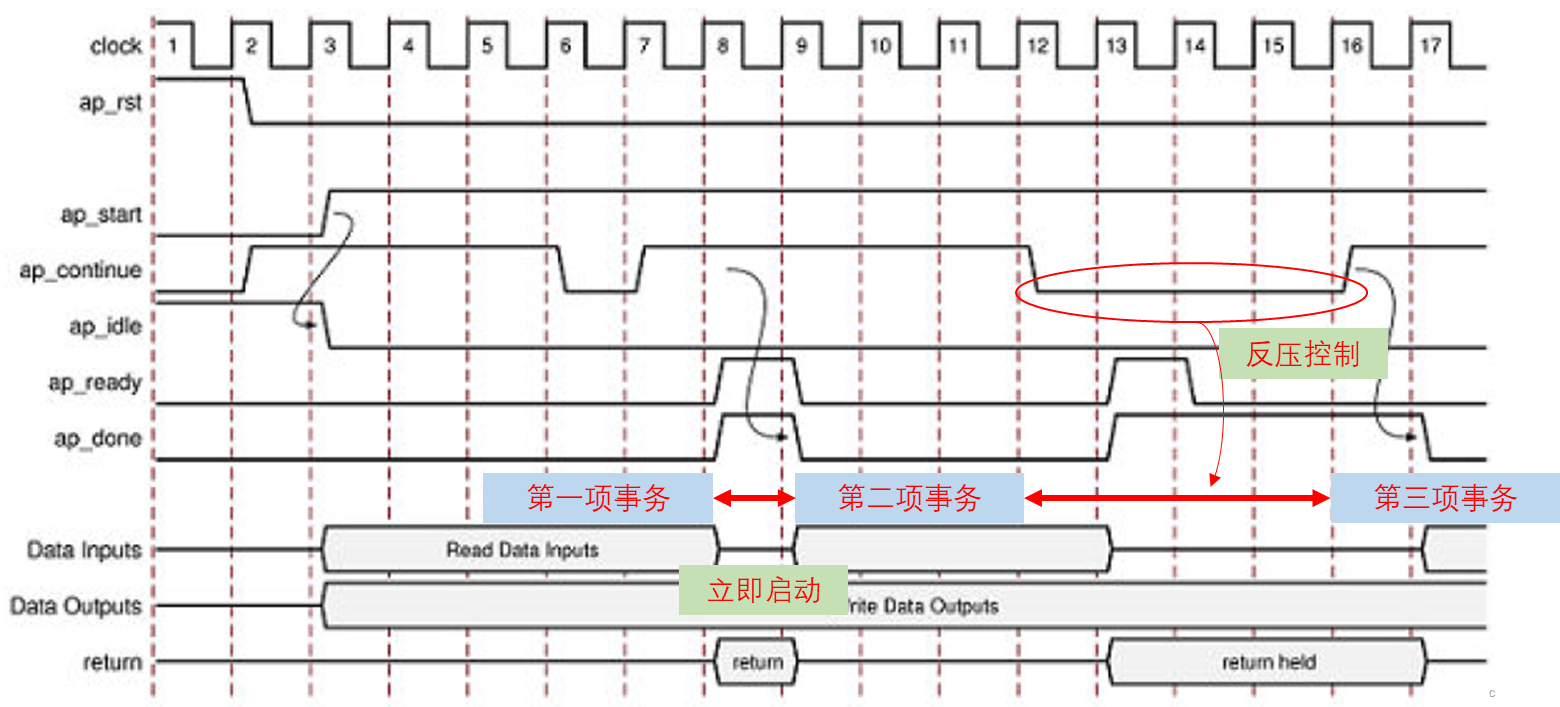

时序图会在复位后显示以下行为:

1. ap_start 变高电平,模块激活。

2. ap_idle 立即变为低电平,退出空闲状态。

3. ap_start 信号必须保持处于高电平状态,直至下游模块 ap_ready 信号传递高电平状态。当 ap_ready 达到高电平状态后:

- 如果 ap_start 保持高电平,设计将启动下一项传输事务。

- 如果 ap_start 变为低电平,设计将完成当前传输事务,然后停止操作。

4. 本模块可读取输入端口上的数据(来自上游模块)。

5. 本模块可将数据写入输出端口(传递至下游模块)。

注释:输入和输出端口还可指定独立于控制协议的端口级 I/O 协议。

6. 当模块完成操作后,ap_done 输出会变为高电平状态。

注释:如果存在 ap_return 端口,那么当 ap_done 处于高电平状态时,此端口上的数据将变为有效。因此,ap_done 信号还用于指示 ap_return 输出上的数据有效。

7. ap_continue 反压信号解释:

- 如果 ap_continue 为高电平,且 ap_done 也为高电平,那么内核将继续操作。

- 如果下游块无法接收新数据输入,则下游模块控制 ap_continue 保持低电平,控制 ap_done 信号保持高电平状,直到下游模块处理完毕,控制 ap_continue 变为高电平状态后继续执行。

8. ap_ready 信号解释:

- 下游块的 ap_ready 信号可直接驱动 ap_continue 信号。

- ap_ready 信号处于不活动状态,直至设计开始操作为止。

- 在非流水打拍设计中,ap_ready 信号与 ap_done 同时断言有效。

- 在流水打拍设计中,当 ap_start 采样结果为高电平后,ap_ready 信号可能在任意周期变为高电平状态。这取决于设计的流水打拍方式。

- 如果 ap_start 信号为低电平状态,而 ap_ready 为高电平状态,那么设计将持续执行操作,直至 ap_done 变为高电平状态后停止操作。

- 如果 ap_start 信号为高电平状态,且 ap_ready 为高电平状态,那么下一项传输事务将立即启动,且设计将继续操作。

9. ap_idle 信号解释:

- 用于指示设计何时处于空闲且不执行操作状态。

- 如果 ap_start 信号为低电平状态,而 ap_ready 为高电平状态,那么设计将停止操作,而 ap_idle 信号将在达成 ap_done 后,再经过 1 个周期后变为高电平状态。

- 如果 ap_start 信号为高电平状态,且 ap_ready 为高电平状态,那么设计将继续操作,且 ap_idle 信号保持处于低电平状态。

3. 总结

当设计硬件模块时,块级控制协议是至关重要的组成部分。这些协议允许模块同步和控制其操作流程,包括何时开始处理数据、何时完成数据处理以及何时处于空闲状态准备接受新的数据输入。其中,ap_ctrl_chain 和 ap_ctrl_hs 协议用于控制驱动的TLP,可以用于顺序执行和流水线执行。而 ap_ctrl_none 协议适用于数据驱动的TLP,它不包含握手信号,完全由数据可用性来驱动模块操作。