phrase-20230117184107

内存一致性模型(Memory Consistency Models)提供内存一致性保证,一致性结果体现在程序内存操作是可预测的。例如在多核或多处理器硬件上,在编写并行的程序时,如果理解当前系统所使用的一致性模型,有助于使程序按的预期运行,有助于减少性能开销。可参考词条 Memory Consistency

通俗一点讲内存一致性就是指一个CPU核上的内存修改操作,在什么时候可以在其它核上反映出来(比如通过一个读操作),我们需要知道不同的CPU架构(甚至相同架构下的不同实现)可能采用不同的内存模型,CPU的内存模型与CPU指令集一样,也是软件与硬件之间的一个契约,只是这个契约对一般的软件人员是透明的,除非你从事的是比较偏底层软件的研发工作,比如开发编译器(gcc, llvm等),开发某种计算机语言(java, go, 等),开发操作系统(实现某些操作系统原语)等。——shawn, 知乎

1 顺序一致性(SC)

顺序一致性模型(Sequential Consistency Models)下访存操作顺序执行,CPU 按照程序中内存操作顺序读取(load)和写入(store)内存。可参考词条 Sequential consistency

1.1 多处理器

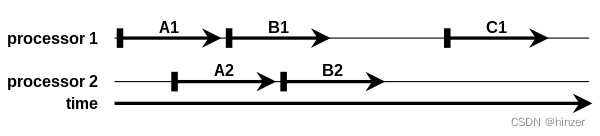

程序在同一个处理器(或线程)中的执行顺序与程序顺序相同,而程序在不同处理器(或线程)中的执行顺序是不确定的。

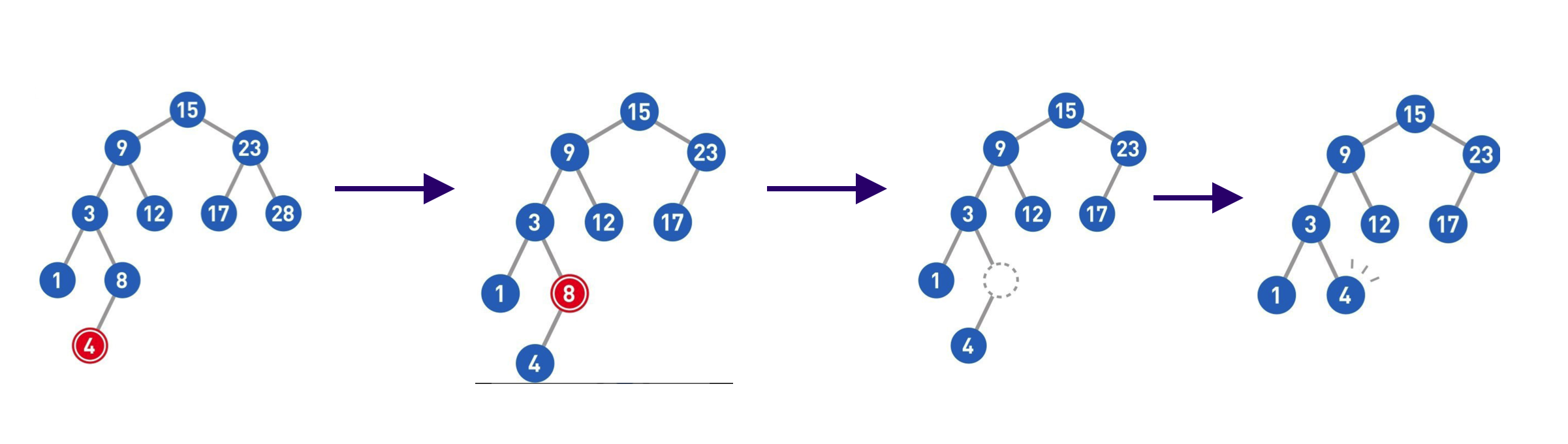

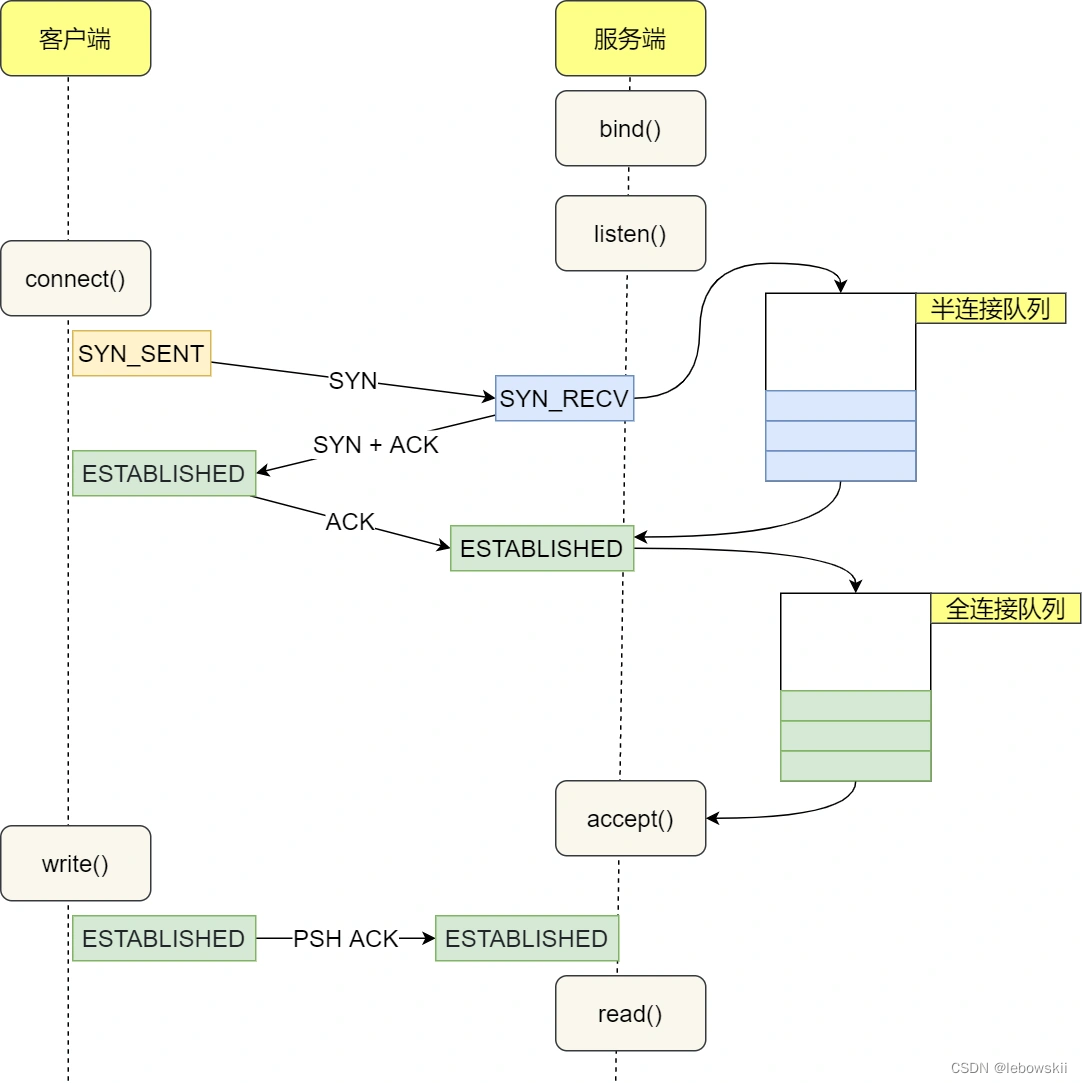

如图,运行在不同的处理器上的任务中,B2 的执行可能在 C1 前或者后。

1.2 共享内存

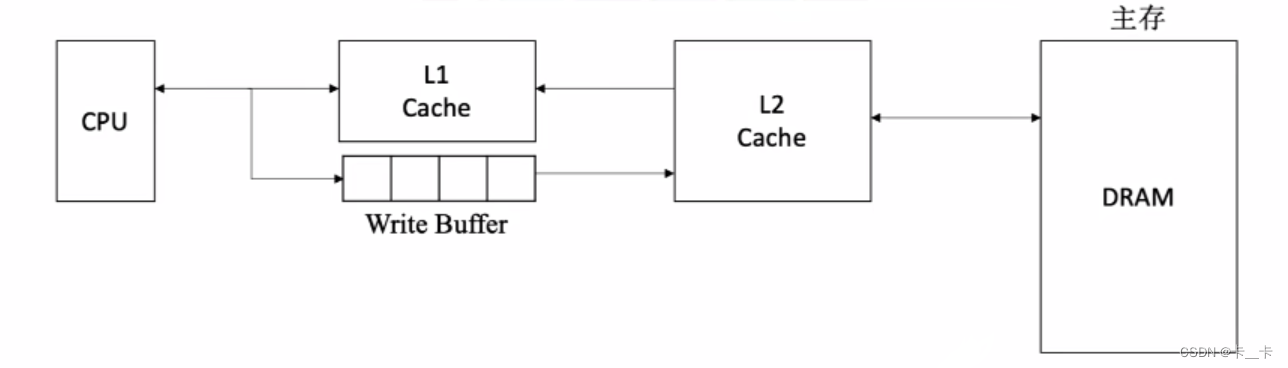

概念上,有一个全局的内存和一个’开关’在任一时刻连接任一处理器,此时处理器按程序顺序发出内存操作,'开关’提供所有内存操作之间的全局串口。

2 弱一致性(WC)

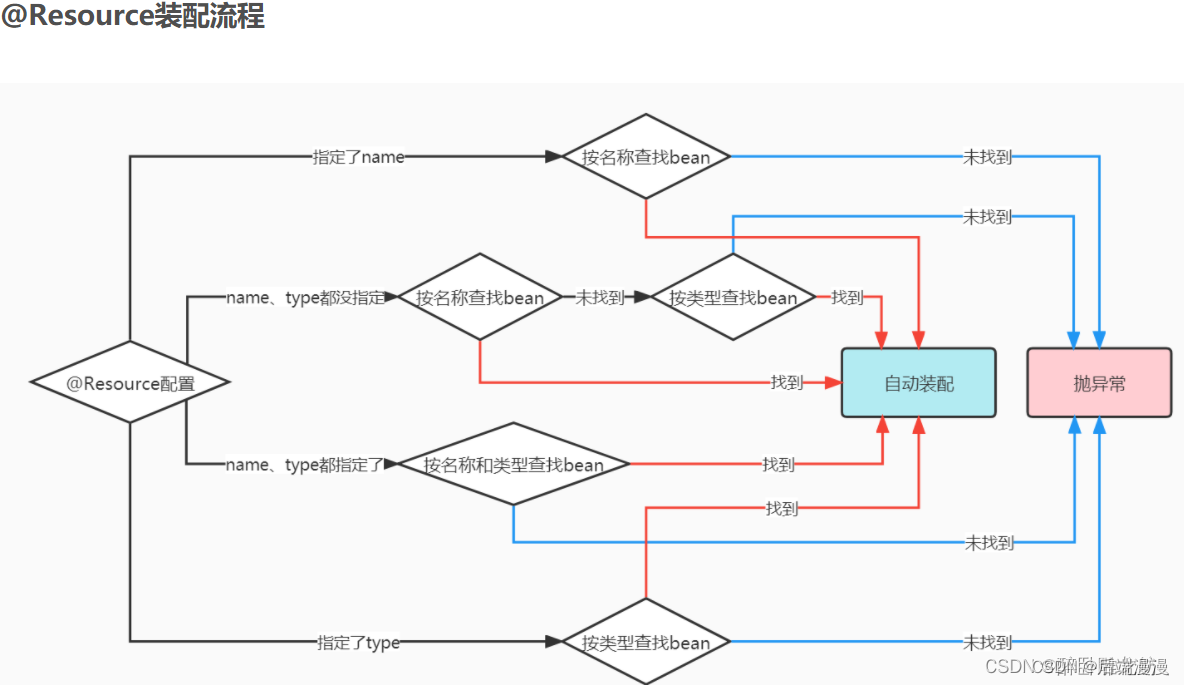

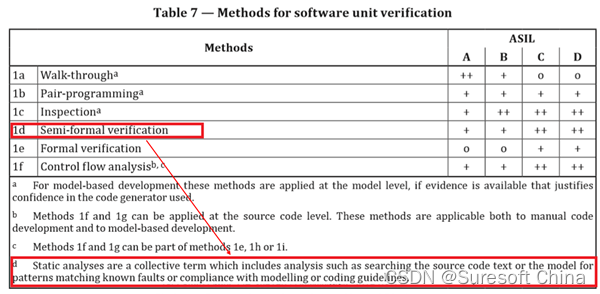

弱一致性模型(Weak Consistency Models)将同步操作和普通访存操作区分开来,硬件不保证内存的一致性,需要程序员遵循平台架构提供的同步操作来保证内存一致性。其中一个同步方法是内存屏障,例如

| 方法 | 描述 |

|---|---|

| rmb() | 阻止跨越屏障的载入动作发生重排序 |

| read_barrier_depends() | 阻止跨越屏障的具有数据依赖关系的载入动作重排序 |

| wmb() | 阻止跨越屏障的存储动作发生重排序 |

| mb() | 阻止跨越屏障的载入和存储动作重新排序 |

| smp_rmb() | 在SMP上提供rmb()功能,在UP上提供barrier()功能 |

| smp_read_barrier_depends() | 在SMP上提供read_barrier_depends()功能,在UP上提供barrier()功能 |

| smp_wmb() | 在SMP上提供wmb()功能,在UP上提供barrier()功能 |

| smp_mb() | 在SMP上提供mb()功能,在UP上提供barrier()功能 |

| barrier() | 阻止编译器跨越屏障对载入或存储操作进行优化 |

3 参考资料

- 《Linux内核设计与实现》

- Consistency_model | wikipedia

- 内存一致性(Memory Consistency) | 知乎