关于SPI

SPI(串行外设接口)是板载设备间通信接口之一。它是由摩托罗拉公司(飞思卡尔半导体)推出的。由于其简单性和通用性,它被纳入各种外围设备中,并与飞利浦I2C总线并列。 SPI的三线或四线信号数量比IIC的两线多,但传输速率可以升至20 Mbps或更高,具体取决于设备的能力(比IIC快5-50倍)。因此,它主要用于需要尽可能高数据传输速率的应用,ADC、DAC或通信IC。

SPI的结构

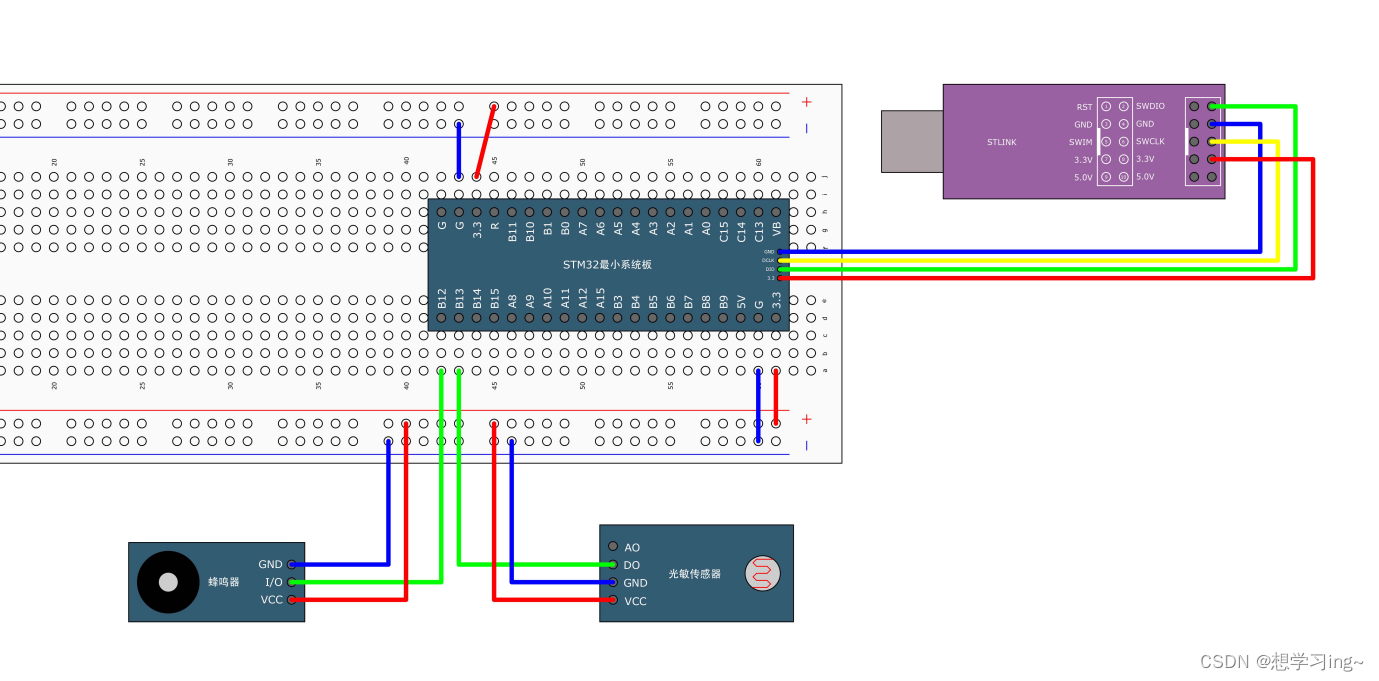

SPI的基本结构如上图所示。主设备和从设备通过SCLK(串行时钟)、MISO(主输入从输出)和MOSI(主输出从输入)三个信号线连接,两个8位移位寄存器的内容为与主设备驱动的移位时钟交换。另外,除上述三个之外的SS(从机选择)信号用于同步数据包或字节边界的开始,并用于同时实现多从机配置。大多数从机设备为 SPI 接口分配不同的引脚名称,例如 DI、DO 和 CS。对于单向传输器件,例如DAC和单通道 ADC,可以省略任一数据线。数据位首先以 MSB 方式移位。

当将一些从属设备连接到 SPI 时,从属设备并行连接,主设备的CS信号连接到每个从属设备。由CS信号选择的从属设备的数据输出被启用,而未选择的设备与MISO 断开连接。

SPI的传输时序

对于SPI,数据移位和数据锁存分别在相反的时钟沿进行,移位和锁存操作分开可以避免两个操作之间的关键时序,从而减轻芯片设计和电路板设计的时序考虑。但另一方面,由于时钟极性和时钟相位的组合,存在四种操作模式,主设备必须将其SPI接口配置为从设备所需的SPI模式。

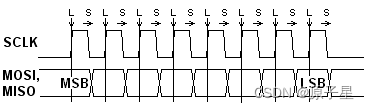

模式0

时钟极性(CPOL)为0,时钟相位(CPHA)为0,SCK在空闲状态时为低电平,数据的采样和传输分别发生在SCK的上升沿和下降沿。即正脉冲,锁定,然后移位,如下图:

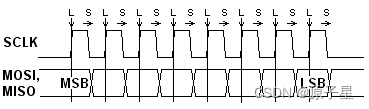

模式1

时钟极性(CPOL)为0,时钟相位(CPHA)为1,SCK在空闲状态仍保持低电平,但是数据的采样和传输分别发生在SCK的下降沿和上升沿。即:正脉冲,先移动,然后锁定,如下图:

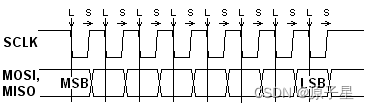

模式2

时钟极性(CPOL)为1,时钟相位(CPHA)为0,SCK信号在空闲状态时为高电平,数据在SCK的下降沿被采样,并在上升沿传输。即:负脉冲,锁定,然后移动。如下图:

模式3

时钟极性(CPOL)为1,时钟相位(CPHA)为1,SCK在空闲状态为高电平,与模式2相反,数据在SCK的上升沿被采样,在下降沿进行传输。即:负脉冲。移位,然后锁存。如下图:

父子通信,传递元素内容](https://img-blog.csdnimg.cn/direct/23bf7a05a7bf4326a6d08994873350e5.png)