零中频的本振泄露会降低发射机的EVM,本文我们将会对SX1255和AD9361的本振泄露问题进行简单的讨论。

1.SX1255载波馈通问题

表1.1中的-8dBc测试结果的前提是PAD输出功率为-5dBm,那么此时根据-8dBc的载波本振抑制可以知道Driver输出的载波馈通功率为-13dBm,又由于Driver具有9dB增益,所以实际混频器和DAC等电路所造成的的载波馈通为-22dBm。然后确定排除数字部分可调增益之后的DAC(-3dBFS)到混频器输出端的功率范围:-8.48dBm~-38.48dBm,由此可以看到不校准的情况下,混频器输出端的本振泄露的功率为-22dBm,它比最小输出功率都大10dB以上。载波馈通抑制变成负值。

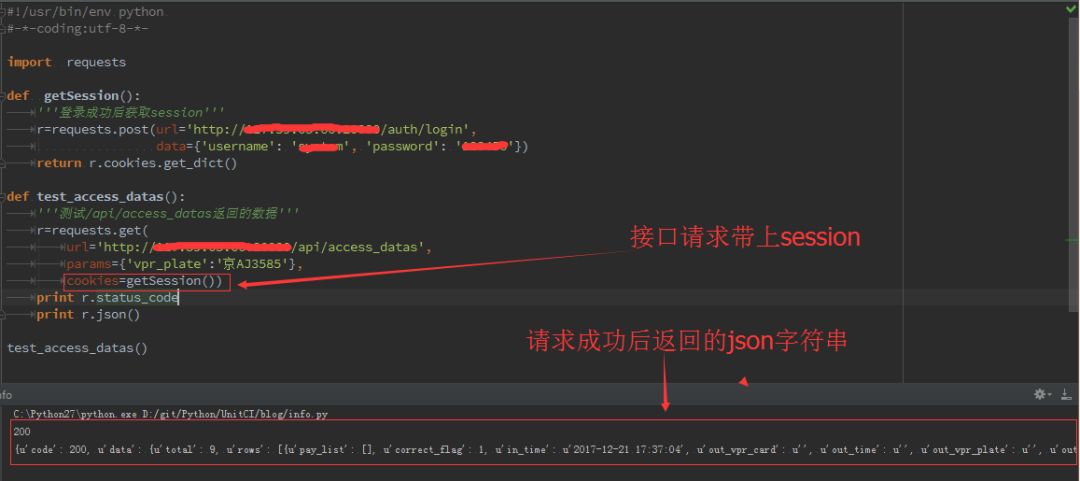

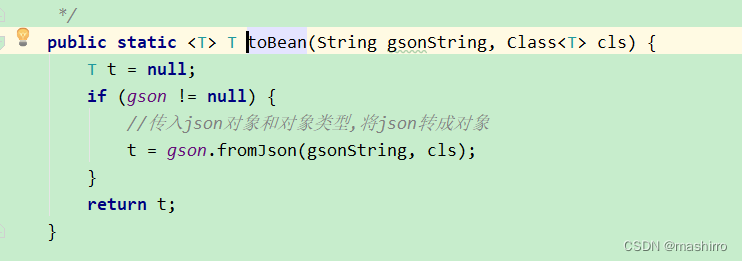

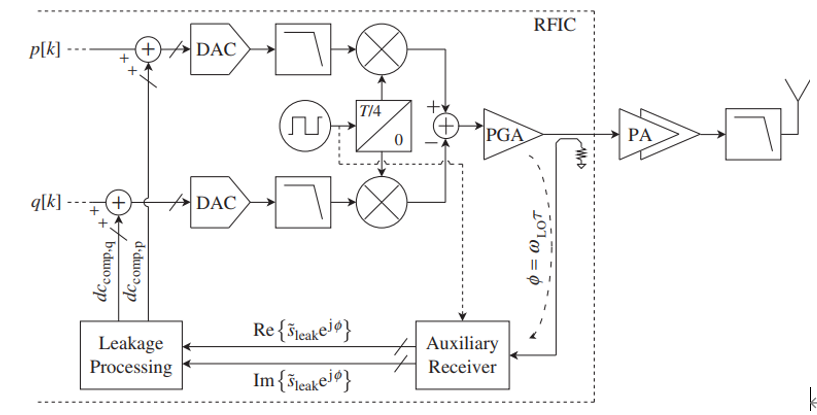

很明显如果不做载波馈通校准,该芯片几乎没有办法使用的,那么载波馈通如何校准?下图来源于《无线算法与架构设计桥梁》,可以看到在闭环校准系统重,需要辅助接收机来进行DAC输出直流的调整来规避LO泄露问题。在半双工收发机中,也可以使用接收闲置状态进行校准。

一般的产品数据手册会给出最小功率输出下的载波馈通值,比如下表1.3:

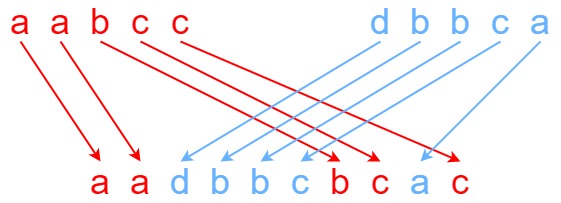

表1.4呈现的内容告诉我们AD9361的本振泄漏呈现以下几点特征:

(1)载波抑制比会随着外部衰减器的变化而变化,即使混频器处的载波抑制比是固定的。

(2)随着衰减值减小(大功率输出),载波抑制比会逐渐增大。

(3)随着输出功率的减小,AD9361自身也不能保证其有优秀的载波抑制比,毕竟剩下的50dB衰减情况下的载波抑制比没有给出。

2.如何规避及解决此问题

(1)从使用角度考虑,比如认为载波抑制比小于30dBc的情况是不可接受的,这样对于SX1255来说,-20dBm以下的功率范围就不能使用(在使用校准算法后)。低载波抑制比的可接受性,会拓展低功率范围的输出。

(2)载波抑制比在全发送功率范围内满足要求的一般硬件措施:

使用SX1255的那种实现方式,会导致随着发送功率的减小,载波抑制比线性下降,也就是下降的比较快。而AD9361这种通过射频端衰减器的方式,则载波抑制比不会随着输出功率的减小而线性下降,从AD9361的载波抑制比数据来看输出功率减小40dB,载波抑制比仅下降20dB。如有必要使用到-40dBm,对于SX1255这种架构,则需要采用外部VGA的方案实现,让SX1255工作在最佳载波抑制情况下,然后通过外部VGA控制输出功率大小。