在Xilinx FPGA中,要实现FIFO的功能时,大部分时候会使用两种方法:

- FIFO Generator IP核

- XPM_FIFO原语

FIFO Generator IP核的优点是有图形化界面,配置参数非常直观;缺点是参数一旦固定,想要更改的化就只能重新generate IP核。

XPM_FIFO原语的优点就是参数配置方便。

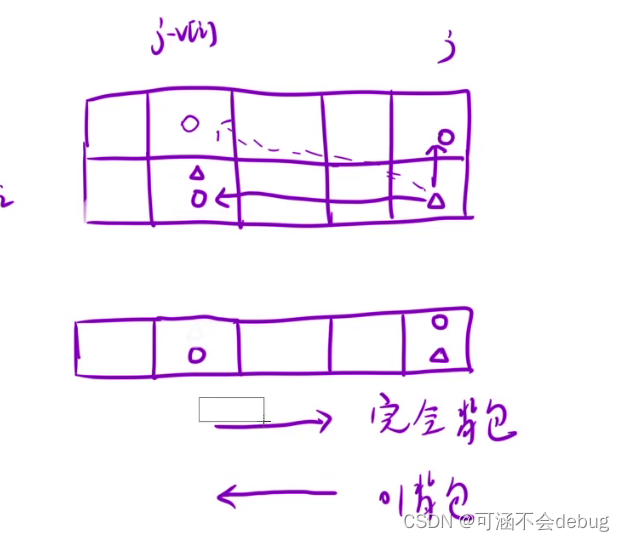

对于两者,还有一个非常重要的区别。!!!大小端不一样!!!

当din的位宽和dout的位宽非对称时。举个栗子:当din的位宽为8bit,dout的位宽为32bit时。

FIFO Generator IP核按大端输出,即先写进去的数据放在高8bit

XPM_FIFO原语按小端输出,即先写进去的数据放在低8bit

下面为RTL设计文件和测试结果。

//-----------------------------------------------------------------------------

//

// Copyright (c) JoeJoe.

//

// Project : fifo_test

// Module : fifo_test.v

// Parent : None

// Children : None

//

// Description:

//

//

//

//

// Parameters:

//

//

//

//

// Local Parameters:

//

// Notes :

//

// Multicycle and False Paths

// Some exist, embedded within the submodules. See the submodule

// descriptions.

//

`timescale 1ns/1ps

module fifo_test (

input sclk

,input srst_n

);

//***************************************************************************

// Parameter definitions

//***************************************************************************

//***************************************************************************

// Reg declarations

//***************************************************************************

reg [2:0] wait_cnt;

reg wr_en;

reg [7:0] din;

wire rd_en;

wire prog_full;

wire full;

wire empty;

wire [31:0] dout;

reg xpm_wr_en;

reg [7:0] xpm_din;

wire xpm_rd_en;

wire xpm_prog_full;

wire xpm_full;

wire xpm_empty;

wire [31:0] xpm_dout;

//***************************************************************************

// Wire declarations

//***************************************************************************

//***************************************************************************

// Code

//***************************************************************************

// 等待XPM FIFO not busy

always @(posedge sclk) begin

if (srst_n == 1'b0) begin

wait_cnt <= 'd0;

end

else begin

if (wait_cnt == 'd7) begin

wait_cnt <= wait_cnt;

end

else begin

wait_cnt <= wait_cnt + 'd1;

end

end

end

// 非满就写

always @(posedge sclk) begin

if (srst_n == 1'b0) begin

wr_en <= 1'b0;

din <= 'd0;

end

else begin

if (prog_full == 1'b1) begin

wr_en <= 1'b0;

din <= 'd0;

end

else if (wait_cnt == 'd7) begin

wr_en <= 1'b1;

din <= din + 'd1;

end

else begin

wr_en <= 1'b0;

din <= 'd0;

end

end

end

// 非空就读

assign rd_en = ~empty;

// 非满就写

always @(posedge sclk) begin

if (srst_n == 1'b0) begin

xpm_wr_en <= 1'b0;

xpm_din <= 'd0;

end

else begin

if (xpm_prog_full == 1'b1) begin

xpm_wr_en <= 1'b0;

xpm_din <= 'd0;

end

else if (wait_cnt == 'd7) begin

xpm_wr_en <= 1'b1;

xpm_din <= din + 'd1;

end

else begin

xpm_wr_en <= 1'b0;

xpm_din <= 'd0;

end

end

end

// 非空就读

assign xpm_rd_en = ~xpm_empty;

fifo_generator_0 U_FIFO_GENERATOR_0 (

.clk ( sclk ) // input wire clk

,.srst ( ~srst_n ) // input wire srst

,.din ( din ) // input wire [7 : 0] din

,.wr_en ( wr_en ) // input wire wr_en

,.rd_en ( rd_en ) // input wire rd_en

,.dout ( dout ) // output wire [31 : 0] dout

,.full ( full ) // output wire full

,.empty ( empty ) // output wire empty

,.prog_full ( prog_full ) // output wire prog_full

);

xpm_fifo_sync #(

.DOUT_RESET_VALUE ( "0" ), // String

.ECC_MODE ( "no_ecc" ), // String

.FIFO_MEMORY_TYPE ( "block" ), // String

.FIFO_READ_LATENCY ( 0 ), // DECIMAL

.FIFO_WRITE_DEPTH ( 1024 ), // DECIMAL

.FULL_RESET_VALUE ( 0 ), // DECIMAL

.PROG_EMPTY_THRESH ( 10 ), // DECIMAL

.PROG_FULL_THRESH ( 500 ), // DECIMAL

.RD_DATA_COUNT_WIDTH( 1 ), // DECIMAL

.READ_DATA_WIDTH ( 32 ), // DECIMAL

.READ_MODE ( "fwft" ), // String

.SIM_ASSERT_CHK ( 0 ), // DECIMAL; 0=disable simulation messages, 1=enable simulation messages

.USE_ADV_FEATURES ( "0707" ), // String

.WAKEUP_TIME ( 0 ), // DECIMAL

.WRITE_DATA_WIDTH ( 8 ), // DECIMAL

.WR_DATA_COUNT_WIDTH( 1 ) // DECIMAL

)

U_XPM_FIFO_SYNC (

.almost_empty ( ), // 1-bit output: Almost Empty : When asserted, this signal indicates that

// only one more read can be performed before the FIFO goes to empty.

.almost_full ( ), // 1-bit output: Almost Full: When asserted, this signal indicates that

// only one more write can be performed before the FIFO is full.

.data_valid ( ), // 1-bit output: Read Data Valid: When asserted, this signal indicates

// that valid data is available on the output bus (dout ).

.dbiterr ( ), // 1-bit output: Double Bit Error: Indicates that the ECC decoder detected

// a double-bit error and data in the FIFO core is corrupted.

.dout (xpm_dout ), // READ_DATA_WIDTH-bit output: Read Data: The output data bus is driven

// when reading the FIFO.

.empty (xpm_empty ), // 1-bit output: Empty Flag: When asserted, this signal indicates that the

// FIFO is empty. Read requests are ignored when the FIFO is empty,

// initiating a read while empty is not destructive to the FIFO.

.full (xpm_full ), // 1-bit output: Full Flag: When asserted, this signal indicates that the

// FIFO is full. Write requests are ignored when the FIFO is full,

// initiating a write when the FIFO is full is not destructive to the

// contents of the FIFO.

.overflow ( ), // 1-bit output: Overflow: This signal indicates that a write request

// (wren) during the prior clock cycle was rejected, because the FIFO is

// full. Overflowing the FIFO is not destructive to the contents of the

// FIFO.

.prog_empty ( ), // 1-bit output: Programmable Empty: This signal is asserted when the

// number of words in the FIFO is less than or equal to the programmable

// empty threshold value. It is de-asserted when the number of words in

// the FIFO exceeds the programmable empty threshold value.

.prog_full (xpm_prog_full), // 1-bit output: Programmable Full: This signal is asserted when the

// number of words in the FIFO is greater than or equal to the

// programmable full threshold value. It is de-asserted when the number of

// words in the FIFO is less than the programmable full threshold value.

.rd_data_count ( ), // RD_DATA_COUNT_WIDTH-bit output: Read Data Count: This bus indicates the

// number of words read from the FIFO.

.rd_rst_busy ( ), // 1-bit output: Read Reset Busy: Active-High indicator that the FIFO read

// domain is currently in a reset state.

.sbiterr ( ), // 1-bit output: Single Bit Error: Indicates that the ECC decoder detected

// and fixed a single-bit error.

.underflow ( ), // 1-bit output: Underflow: Indicates that the read request (rd_en) during

// the previous clock cycle was rejected because the FIFO is empty. Under

// flowing the FIFO is not destructive to the FIFO.

.wr_ack ( ), // 1-bit output: Write Acknowledge: This signal indicates that a write

// request(wr_en) during the prior clock cycle is succeeded.

.wr_data_count ( ), // WR_DATA_COUNT_WIDTH-bit output: Write Data Count: This bus indicates

// the number of words written into the FIFO.

.wr_rst_busy ( ), // 1-bit output: Write Reset Busy: Active-High indicator that the FIFO

// write domain is currently in a reset state.

.din (xpm_din ), // WRITE_DATA_WIDTH-bit input: Write Data: The input data bus used when

// writing the FIFO.

.injectdbiterr (1'b0 ), // 1-bit input: Double Bit Error Injection: Injects a double bit error if

// the ECC feature is used on block RAMs or UltraRAM macros.

.injectsbiterr (1'b0 ), // 1-bit input: Single Bit Error Injection: Injects a single bit error if

// the ECC feature is used on block RAMs or UltraRAM macros.

.rd_en (xpm_rd_en ), // 1-bit input: Read Enable: If the FIFO is not empty, asserting this

// signal causes data(on dout) to be read from the FIFO. Must be held

// active-low when rd_rst_busy is active high.

.rst (~srst_n ), // 1-bit input: Reset: Must be synchronous to wr_clk. The clock(s) can be

// unstable at the time of applying reset, but reset must be released only

// after the clock(s) is/are stable.

.sleep (1'b0 ), // 1-bit input: Dynamic power saving- If sleep is High, the memory/fifo

// block is in power saving mode.

.wr_clk (sclk ), // 1-bit input: Write clock: Used for write operation. wr_clk must be a

// free running clock.

.wr_en (xpm_wr_en ) // 1-bit input: Write Enable: If the FIFO is not full, asserting this

// signal causes data(on din) to be written to the FIFO Must be held

// active-low when rst or wr_rst_busy or rd_rst_busy is active high

);

endmodule

当din的位宽和dout的位宽非对称时。举个栗子:当din的位宽为32bit,dout的位宽为8bit时。

FIFO Generator IP核 高8bit先输出,低8bit最后输出

XPM_FIFO原语 低8bit先输出,高8bit最后输出

下面为RTL设计文件和测试结果。

//-----------------------------------------------------------------------------

//

// Copyright (c) JoeJoe.

//

// Project : fifo_test

// Module : fifo_test.v

// Parent : None

// Children : None

//

// Description:

//

//

//

//

// Parameters:

//

//

//

//

// Local Parameters:

//

// Notes :

//

// Multicycle and False Paths

// Some exist, embedded within the submodules. See the submodule

// descriptions.

//

`timescale 1ns/1ps

module fifo_test (

input sclk

,input srst_n

);

//***************************************************************************

// Parameter definitions

//***************************************************************************

//***************************************************************************

// Reg declarations

//***************************************************************************

reg [2:0] wait_cnt;

reg wr_en;

reg [31:0] din;

wire rd_en;

wire prog_full;

wire full;

wire empty;

wire [7:0] dout;

reg xpm_wr_en;

reg [31:0] xpm_din;

wire xpm_rd_en;

wire xpm_prog_full;

wire xpm_full;

wire xpm_empty;

wire [7:0] xpm_dout;

//***************************************************************************

// Wire declarations

//***************************************************************************

//***************************************************************************

// Code

//***************************************************************************

// 等待XPM FIFO not busy

always @(posedge sclk) begin

if (srst_n == 1'b0) begin

wait_cnt <= 'd0;

end

else begin

if (wait_cnt == 'd7) begin

wait_cnt <= wait_cnt;

end

else begin

wait_cnt <= wait_cnt + 'd1;

end

end

end

// 非满就写

always @(posedge sclk) begin

if (srst_n == 1'b0) begin

wr_en <= 1'b0;

din <= 'd0;

end

else begin

if (prog_full == 1'b1) begin

wr_en <= 1'b0;

din <= din;

end

else if (wait_cnt == 'd7) begin

wr_en <= 1'b1;

din <= din + 'd1;

end

else begin

wr_en <= 1'b0;

din <= 'd0;

end

end

end

// 非空就读

assign rd_en = ~empty;

// 非满就写

always @(posedge sclk) begin

if (srst_n == 1'b0) begin

xpm_wr_en <= 1'b0;

xpm_din <= 'd0;

end

else begin

if (xpm_prog_full == 1'b1) begin

xpm_wr_en <= 1'b0;

xpm_din <= xpm_din;

end

else if (wait_cnt == 'd7) begin

xpm_wr_en <= 1'b1;

xpm_din <= xpm_din + 'd1;

end

else begin

xpm_wr_en <= 1'b0;

xpm_din <= 'd0;

end

end

end

// 非空就读

assign xpm_rd_en = ~xpm_empty;

// fifo_generator_0 U_FIFO_GENERATOR_0 (

// .clk ( sclk ) // input wire clk

// ,.srst ( ~srst_n ) // input wire srst

// ,.din ( din ) // input wire [7 : 0] din

// ,.wr_en ( wr_en ) // input wire wr_en

// ,.rd_en ( rd_en ) // input wire rd_en

// ,.dout ( dout ) // output wire [31 : 0] dout

// ,.full ( full ) // output wire full

// ,.empty ( empty ) // output wire empty

// ,.prog_full ( prog_full ) // output wire prog_full

// );

fifo_generator_1 U_FIFO_GENERATOR_1 (

.clk ( sclk ) // input wire clk

,.srst ( ~srst_n ) // input wire srst

,.din ( din ) // input wire [31 : 0] din

,.wr_en ( wr_en ) // input wire wr_en

,.rd_en ( rd_en ) // input wire rd_en

,.dout ( dout ) // output wire [7 : 0] dout

,.full ( full ) // output wire full

,.empty ( empty ) // output wire empty

,.prog_full ( prog_full ) // output wire prog_full

);

xpm_fifo_sync #(

.DOUT_RESET_VALUE ( "0" ), // String

.ECC_MODE ( "no_ecc" ), // String

.FIFO_MEMORY_TYPE ( "block" ), // String

.FIFO_READ_LATENCY ( 0 ), // DECIMAL

.FIFO_WRITE_DEPTH ( 256 ), // DECIMAL

.FULL_RESET_VALUE ( 0 ), // DECIMAL

.PROG_EMPTY_THRESH ( 10 ), // DECIMAL

.PROG_FULL_THRESH ( 125 ), // DECIMAL

.RD_DATA_COUNT_WIDTH( 1 ), // DECIMAL

.READ_DATA_WIDTH ( 8 ), // DECIMAL

.READ_MODE ( "fwft" ), // String

.SIM_ASSERT_CHK ( 0 ), // DECIMAL; 0=disable simulation messages, 1=enable simulation messages

.USE_ADV_FEATURES ( "0707" ), // String

.WAKEUP_TIME ( 0 ), // DECIMAL

.WRITE_DATA_WIDTH ( 32 ), // DECIMAL

.WR_DATA_COUNT_WIDTH( 1 ) // DECIMAL

)

U_XPM_FIFO_SYNC (

.almost_empty ( ), // 1-bit output: Almost Empty : When asserted, this signal indicates that

// only one more read can be performed before the FIFO goes to empty.

.almost_full ( ), // 1-bit output: Almost Full: When asserted, this signal indicates that

// only one more write can be performed before the FIFO is full.

.data_valid ( ), // 1-bit output: Read Data Valid: When asserted, this signal indicates

// that valid data is available on the output bus (dout ).

.dbiterr ( ), // 1-bit output: Double Bit Error: Indicates that the ECC decoder detected

// a double-bit error and data in the FIFO core is corrupted.

.dout (xpm_dout ), // READ_DATA_WIDTH-bit output: Read Data: The output data bus is driven

// when reading the FIFO.

.empty (xpm_empty ), // 1-bit output: Empty Flag: When asserted, this signal indicates that the

// FIFO is empty. Read requests are ignored when the FIFO is empty,

// initiating a read while empty is not destructive to the FIFO.

.full (xpm_full ), // 1-bit output: Full Flag: When asserted, this signal indicates that the

// FIFO is full. Write requests are ignored when the FIFO is full,

// initiating a write when the FIFO is full is not destructive to the

// contents of the FIFO.

.overflow ( ), // 1-bit output: Overflow: This signal indicates that a write request

// (wren) during the prior clock cycle was rejected, because the FIFO is

// full. Overflowing the FIFO is not destructive to the contents of the

// FIFO.

.prog_empty ( ), // 1-bit output: Programmable Empty: This signal is asserted when the

// number of words in the FIFO is less than or equal to the programmable

// empty threshold value. It is de-asserted when the number of words in

// the FIFO exceeds the programmable empty threshold value.

.prog_full (xpm_prog_full), // 1-bit output: Programmable Full: This signal is asserted when the

// number of words in the FIFO is greater than or equal to the

// programmable full threshold value. It is de-asserted when the number of

// words in the FIFO is less than the programmable full threshold value.

.rd_data_count ( ), // RD_DATA_COUNT_WIDTH-bit output: Read Data Count: This bus indicates the

// number of words read from the FIFO.

.rd_rst_busy ( ), // 1-bit output: Read Reset Busy: Active-High indicator that the FIFO read

// domain is currently in a reset state.

.sbiterr ( ), // 1-bit output: Single Bit Error: Indicates that the ECC decoder detected

// and fixed a single-bit error.

.underflow ( ), // 1-bit output: Underflow: Indicates that the read request (rd_en) during

// the previous clock cycle was rejected because the FIFO is empty. Under

// flowing the FIFO is not destructive to the FIFO.

.wr_ack ( ), // 1-bit output: Write Acknowledge: This signal indicates that a write

// request(wr_en) during the prior clock cycle is succeeded.

.wr_data_count ( ), // WR_DATA_COUNT_WIDTH-bit output: Write Data Count: This bus indicates

// the number of words written into the FIFO.

.wr_rst_busy ( ), // 1-bit output: Write Reset Busy: Active-High indicator that the FIFO

// write domain is currently in a reset state.

.din (xpm_din ), // WRITE_DATA_WIDTH-bit input: Write Data: The input data bus used when

// writing the FIFO.

.injectdbiterr (1'b0 ), // 1-bit input: Double Bit Error Injection: Injects a double bit error if

// the ECC feature is used on block RAMs or UltraRAM macros.

.injectsbiterr (1'b0 ), // 1-bit input: Single Bit Error Injection: Injects a single bit error if

// the ECC feature is used on block RAMs or UltraRAM macros.

.rd_en (xpm_rd_en ), // 1-bit input: Read Enable: If the FIFO is not empty, asserting this

// signal causes data(on dout) to be read from the FIFO. Must be held

// active-low when rd_rst_busy is active high.

.rst (~srst_n ), // 1-bit input: Reset: Must be synchronous to wr_clk. The clock(s) can be

// unstable at the time of applying reset, but reset must be released only

// after the clock(s) is/are stable.

.sleep (1'b0 ), // 1-bit input: Dynamic power saving- If sleep is High, the memory/fifo

// block is in power saving mode.

.wr_clk (sclk ), // 1-bit input: Write clock: Used for write operation. wr_clk must be a

// free running clock.

.wr_en (xpm_wr_en ) // 1-bit input: Write Enable: If the FIFO is not full, asserting this

// signal causes data(on din) to be written to the FIFO Must be held

// active-low when rst or wr_rst_busy or rd_rst_busy is active high

);

endmodule

参考文档如下:《FIFO Generator v13.2 Product Guide》(PG057)

FIFO Generator IP,小位宽写,大位宽读,大端。

FIFO Generator IP,大位宽写,小位宽读。

疑问:XPM_FIFO为什么不可以设置大小端,以及为什么不和FIFO Generator IP统一???