一、前言

PCIe总线是由PCI/PCI-X发展而来,但是两者之间有很大的不同。PCI/PCI-X采用的是并行总线,最大支持的频率为PCI-X2.0 的133MHz,传输速率最大仅为4262MB/s。同时使用并行总线,在PCB上也会造成布线资源紧张,线与线之间的串扰较大。因此在高速领域,由并行转换成串行已经成为了一种趋势。PCIe总线就是采用串行传输协议,传输速率极高,并且由于采用了8B/10B编码、128B/130B编码,所以抗干扰能力强,传输距远。

PCIe发展至今已经发展到第7代,1.0、2.0版本编码都采用的8B/10B编码,但是由于8B/10B编码带宽利用率低,所以在之后采用的是128B/130B编码。但是从PCIe6.0采用的是PAM-4,FLIT编码,之后的版本编码可能也会继续采用PAM编码。

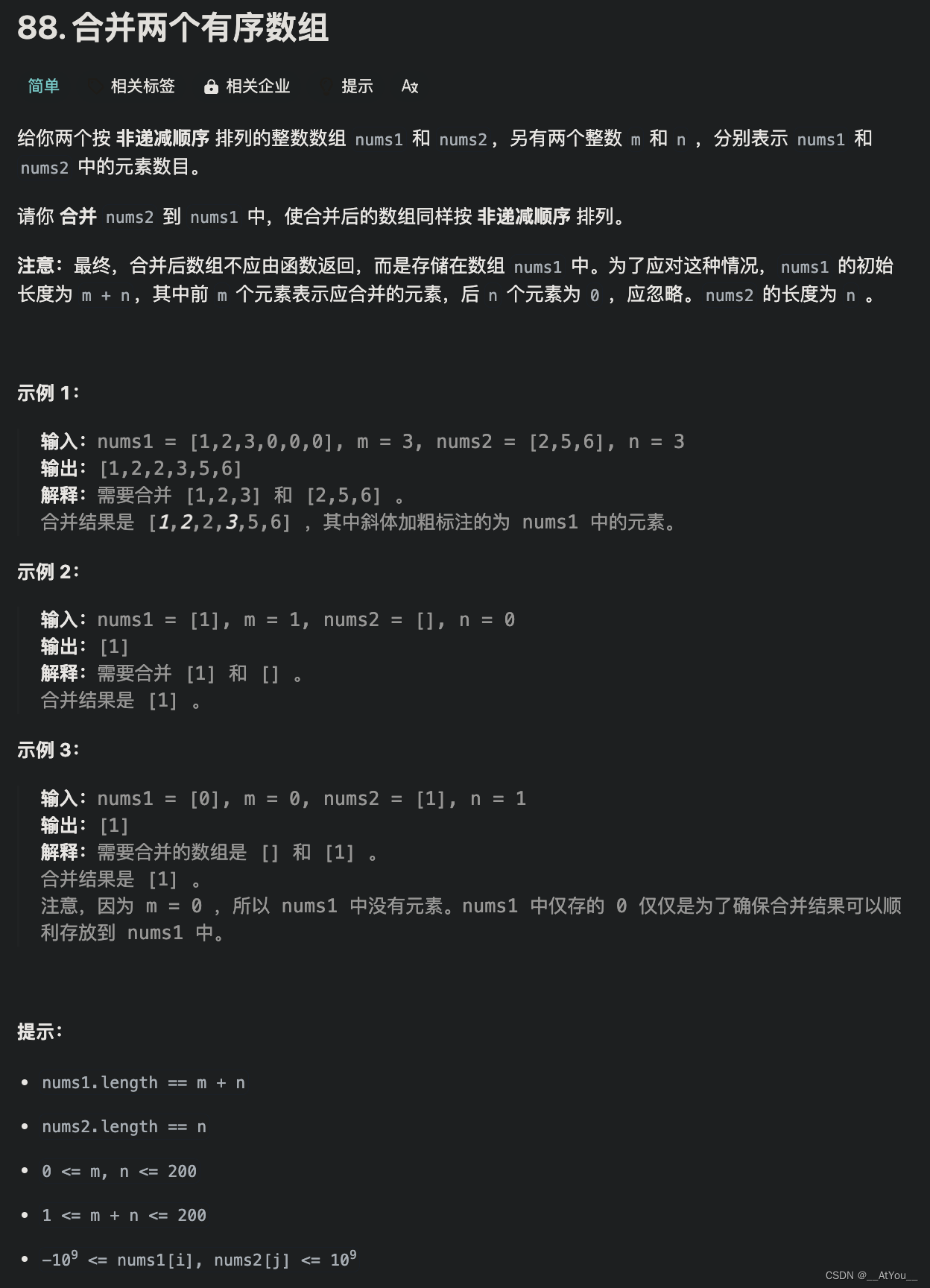

而PCIe常说的x1、x4、x8、x16代表的是通道的数量先来看一下PCIe1.0-PCIe5.6不同的通道个数的传输速率:

带宽计算:

GT/s代表的是“Giga Transfers Per Second”(编码后每秒传输多少个bit),对于PCIe1.0 x1来说,GT与GB之间的换算关系为:

(2.5GT / 10)*8 = 2000 Mbps = 250MB/s

所以x4就是1GB/s,x8就是2GB/s。

二、硬件设计

PCIe的引脚又被称为金手指,一个PCI Express连接可以被配置成x1, x2, x4, x8, x12, x16和x32的数据带宽。 (x2 and x12 link widths are optional) PCI-E 各种位宽Device可以自由搭配使用,比如x1 的卡可以插到x8的插槽中使用, x8 的卡可以插到x16的插槽中使用,升级方便。

1、Vcc、Vaux

PCIe设备使用两种电源信号供电,分别是Vcc与Vaux,其额定电压为3.3V。其中Vcc为主电源,PCIe设备使用的主要逻辑模块均使用Vcc供电,而一些与电源管理相关的逻辑使用 Vaux供电。在PCIe设备中,一些特殊的寄存器通常使用Vaux供电,如Sticky Register,.此时即使PCIe设备的Vcc被移除,这些与电源管理相关的逻辑状态和这些特殊寄存器的内容也不会发生改变。

在PCIe总线中,使用Vcc的主要原因是为了降低功耗和缩短系统恢复时间。因为Vaux在多数情况下并不会被移除,因此当PCIe设备的V恢复后,该设备不必重新恢复使用Vaux供电的逻辑,从而设备可以很快地恢复到正常工作状状态

2、 PERST信号

该信号为全局复位信号,由处理器系统提供,处理器系统需要为PCIe插槽和PCIe设备提供该复位信号。PCIe设备使用该信号复位内部逻辑。当该信号有效时,PCIe设备将进行复位操作。

3、REFCLK_P、REFCLK_N

这两个信号就是PCIe绑定的GT Bank的其中一个参考时钟,不过这个参考时钟的频率为100M。此时钟是由PCIe的插槽提供。

在一个处理器系统中,可能含有许多PCIe设备,这些设备可以作为Add-In卡与PCIe插槽连接,也可以作为内置模块,与处理器系统提供的PCIe链路直接相连,而不需要经过PCIe插槽。PCIe设备与PCIe插槽都具有REFCLK+和REFCLK-信号,其中PCIe插槽使用这组信号与处理器系统同步。

在一个处理器系统中,通常采用专用逻辑向PCIe插槽提供REFCLK+和REFCLK-信号,如下图所示。其中100Mhz的时钟源由晶振提供,并经过一个“一推多”的差分时钟驱动器生成多个同相位的时钟源,与PCIe插槽一一对应连接。

参考时钟与PCIE插槽的连接

PCIe插槽需要使用参考时钟,其频率范围为100MHz±300ppm。处理器系统需要为每一个PCIe插槽、MCH、ICH和Switch提供参考时钟。而且要求在一个处理器系统中,时钟驱动器产生的参考时钟信号到每一个PCIe插槽(MCH、ICH和Swith)的距离差在15英寸之内。通常信号的传播速度接近光速,约为6inch/ns,由此可见,不同PCIe插槽间REFCLK+和REFCLK-信号的传送延时差约为2.5ns。

4、PCIE_RX# 与 PCIE_TX#

RX与TX都是差分信号,都是成对出现的。这些信号也就是GT Transceiver中的收发信号。

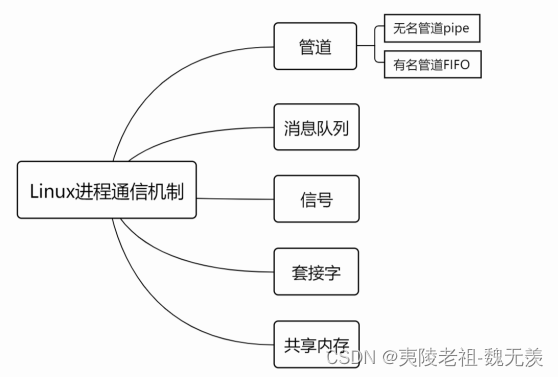

三、PCIe体系结构入门

典型的拓扑结构

Root Complex:可以简称为RC,他是CPU与内存、PCIe switch等PCIe之间的传输介质。它使用link training和状态机去管理PCIe设备之间的连接。从广义上讲,RC可以理解为系统CPU和PCle拓扑之间的接口,PCle端口在配置空间中被标记为“根端口”。主要作用是将CPU地址空间与PCIe系统地址的空间隔离,比如地址映射转换、映射等。

PCIe Bridge to PCI or PCI-X:主要作用是将PCIe传输的数据转换成PCI或者PCI-X形式的数据。

Switch:因为PCIe是点对点的连接,所以Switch相当于一个交换机,用于连接CPU与下面任意一个的PCIe设备之间的点对点之间的连接。大多数Switch包含一个Upstream Port和多个Downstream Port。

PCIe Endpoint:可以进行PCIe传输的设备,只能接受来自上级拓扑的数据包或者向上级拓扑发送数据包。例如声卡、网卡。

PCIe体系分层结构

以下全部引用自:PCIe扫盲——PCIe总线体系结构入门-Felix-电子技术应用-AET-中国科技核心期刊-最丰富的电子设计资源平台

和很多的串行传输协议一样,一个完整的PCIe体系结构包括应用层、事务层(Transaction Layer)、数据链路层(Data Link Layer)和物理层(Physical Layer)。其中,应用层并不是PCIe Spec所规定的内容,完全由用户根据自己的需求进行设计,另外三层都是PCIe Spec明确规范的,并要求设计者严格遵循的。

一个简化的PCIe总线体系结构如上图所示,其中Device Core and interface to Transaction Layer就是我们常说的应用层或者软件层。这一层决定了PCIe设备的类型和基础功能,可以由硬件(如FPGA)或者软硬件协同实现。如果该设备为Endpoint,则其最多可拥有8项功能(Function),且每项功能都有一个对应的配置空间(Configuration Space)。如果该设备为Switch,则应用层需要实现包路由(Packet Routing)等相关逻辑。如果该设备为Root,则应用层需要实现虚拟的PCIe总线0(Virtual PCIe Bus 0),并代表整个PCIe总线系统与CPU通信。

事务层(Transaction Layer):接收端的事务层负责事务层包(Transaction Layer Packet,TLP)的解码与校检,发送端的事务层负责TLP的创建。此外,事务层还有QoS(Quality of Service)和流量控制(Flow Control)以及Transaction Ordering等功能。

数据链路层(Data Link Layer):数据链路层负责数据链路层包(Data Link Layer Packet,DLLP)的创建,解码和校检。同时,本层还实现了Ack/Nak的应答机制。

物理层(Physical Layer):物理层负责Ordered-Set Packet的创建于解码。同时负责发送与接收所有类型的包(TLPs、DLLPs和Ordered-Sets)。当前在发送之前,还需要对包进行一些列的处理,如Byte Striping、Scramble(扰码)和Encoder(8b/10b for Gen1&Gen2, 128b/130b for Gen3& Gen4)。对应的,在接收端就需要进行相反的处理。此外,物理层还实现了链路训练(Link Training)和链路初始化(Link Initialization)的功能,这一般是通过链路训练状态机(Link Training and Status State Machine,LTSSM)来完成的。

需要注意的是,在PCIe体系结构中,事务层,数据链路层和物理层存在于每一个端口(Port)中,也就是说Switch中必然存在一个以上的这样的结构(包括事务层,数据链路层和物理层的)。一个简化的模型如下图所示:

关于事务层,数据链路层和物理层的详细的功能图标如下图所示:

![[muduo网络库]——muduo库TimeStamp类(剖析muduo网络库核心部分、设计思想)](https://img-blog.csdnimg.cn/direct/ed1723afa7c8426ca82ccf22bc341fb7.png)

![[力扣题解] 96. 不同的二叉搜索树](https://img-blog.csdnimg.cn/direct/a16c9c76eab2463d8055367737afdc32.png#pic_center)

![61、内蒙古工业大学、内蒙科学技术研究院:CBAM-CNN用于SSVEP - BCI的分类方法[脑机二区还是好发的]](https://img-blog.csdnimg.cn/direct/2bc65a9d10a542f48b141cfe6a0530dd.png)