今天简单总结下 TriCore 的中断路由模块。

名词缩写

| 缩写 | 全程 | 说明 |

| IR | Interrupt Router | |

| SR | Service Request | 包括: 1. External Resource 2. Internal Resource 3.SW(Software) |

| SP | Service Privoder | 包括: 1. CPU 2. DMA |

| SRN | Service Request Node | |

| SRC | Service Request Control Register | |

| GPSR | General Purpose Service Request | |

| SRB | Service Request Broadcast Register | |

| ICU | Interrupt Control Units | |

| TOS | Types of Service |

中断路由器

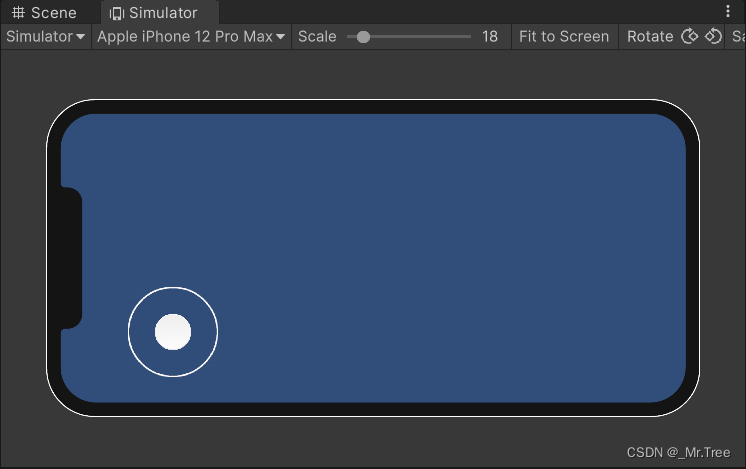

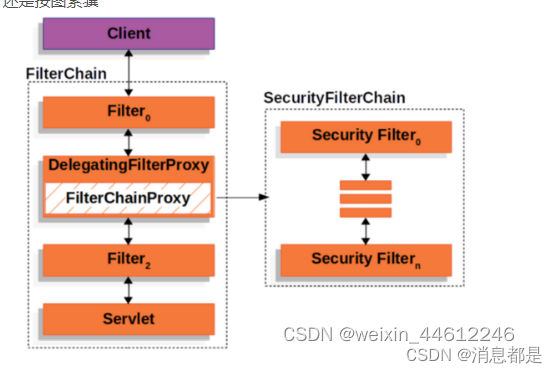

IR框架

如上图所示,每一个可以产生 SR(Service Request)的模块分别连接到 IR(Interrupt Router)中的一个或多个 SRN(Service Request Node)上,每一个SRN 内都有一个 SRC(Service Request Control Register)。每一路 SRN 都会连接到某一个 ICU(Interrupt Control Unit)上,一个 ICU 对应一个 SP(Service Privoder)。

比如TC39X系列,有 6 个CPU Core 和 1个 DMA,则 6 CPU + 1 DMA = 7SP 。上图中可以看到 CPU0 之后就是DMA,而不是CPU1,应该是对应 TriCore 家族的设计语言,不同子系列虽然资源不同,但是编址一致,因此不同芯片子系列的程序语言可以保持一致。

TC3XX系列最多支持 1024 个SR,不同的家族系列个数不一样,一般来说,Core 越多,支持的 SR 越多。

每一个 Core 中断向量表有256个入口,即最多支持 256 路 SR。

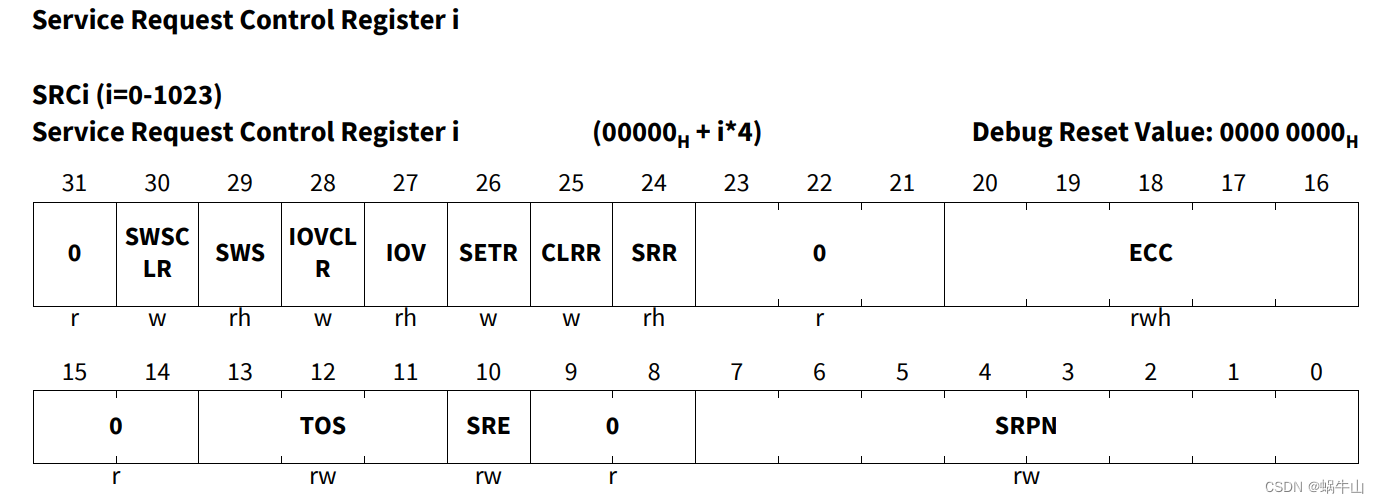

SRC 寄存器

| Field | Bits | Type | Description |

| SRPN | 7:0 | rw | 设置中断优先级,数字越大,优先级越高。取值范围:[0~255] 其中 优先级 0 专为 DMA使用,因此,用作 CPU的有效中断优先级范围是 [1, 255] |

| SRN | 10 | rw | 0:禁用中断 1:使能中断 |

| TOS | 13:11 | rw | 设置SP的类型,包括 CPU 和 DMA 0: CPU0 1: DMA 2: CPU1 3: CPU2 4: CPU3 5: CPU4 6: CPU5 |

| ECC | 20:16 | rwh | ECC检测,进行写操作时更新 |

| SRR | rh | 中断请求标志位(呈现结果,不可写入) 0: 无中断请求,not pending 1: 有中断请求 is pending | |

| CLRR | w | 清除中断请求 0: No action 1: 清除 SRR; (读取到的值都是0,因此不建议读。如果和 SETR 并行写入,则无效果). | |

| SETR | w | 发出中断请求 0: No action 1: 写 SRR 和 SWS; (读取到的值都是0,因此不建议读。如果和 CLRR 并行写入,则无效果) | |

| IOV | rh | 中断触发溢出标志位 0: 无溢出 1: 有溢出 | |

| IOVCLR | w | 清除中断触发溢出标志位 0: No action 1: 清除 IOV; (读取到的值都是0,因此不建议读) | |

| SWS | rh | 软件粘滞标志位 0: 中断未通过 SETR 触发 1: 中断通过 SETR 触发 | |

| SWSCLR | w | 清除软件粘滞标志位 0: No action 1: 清除 SWS; (读取到的值都是0,因此不建议读) | |

| Other | r | reserved |

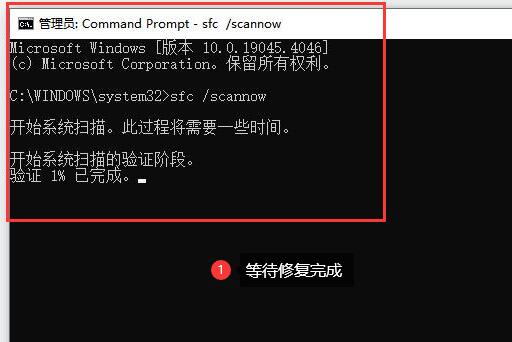

中断初始化

一般来说,中断初始化要进行的操作包括:

SRC.SRPN : 设置该路中断优先级,有效范围是 [1, 255]

SRC.SRN : 设置该路中断是否使能

SRC.TOS : 设置该路中断的 SP. 即进行相应的绑核操作

软中断

TriCore 的中断设计允许每一路中断都可以采用软件触发的方式触发,只需要另 SRC.SETR = 1 就可以触发该路中断。

写SRC.SETR = 1 后,会同时有:

1. SRC.SRR ==1,表明该路中断已经被成功触发,处于 Pending 状态;

2. SRC.SWS ==1,表明该路中断是由软件触发;

要清除软件触发,则需要写:

1. SRC.CLRR =1,清除该路中断的 Pending 状态;

2. SRC.SWSCLR =1,清除该路中断的软件触发粘滞标志位;

笔者认为,相对ARM架构来说,TriCore 的中断设计对软件开发人员来说更友好一些,只需要操作一个寄存器即可完成对该路中断的使能/禁用,触发/清除 等操作,定位问题的时候也相对友好一些。

参考资料:

AURIX TC3xx Family User's Manual Part 1 (infineon.com)