目录

1.指令的执行过程

2. ARM处理器概述

3.ARM指令集

4.ARM存储模型

5. ARM工作模式

6.ARM寄存器组织

(1)寄存器

(2) ARM寄存器

(3)CPSR寄存器

7. ARM异常处理

(1)异常

(2)异常源

(3)ARM异常模式

(4) ARM异常响应

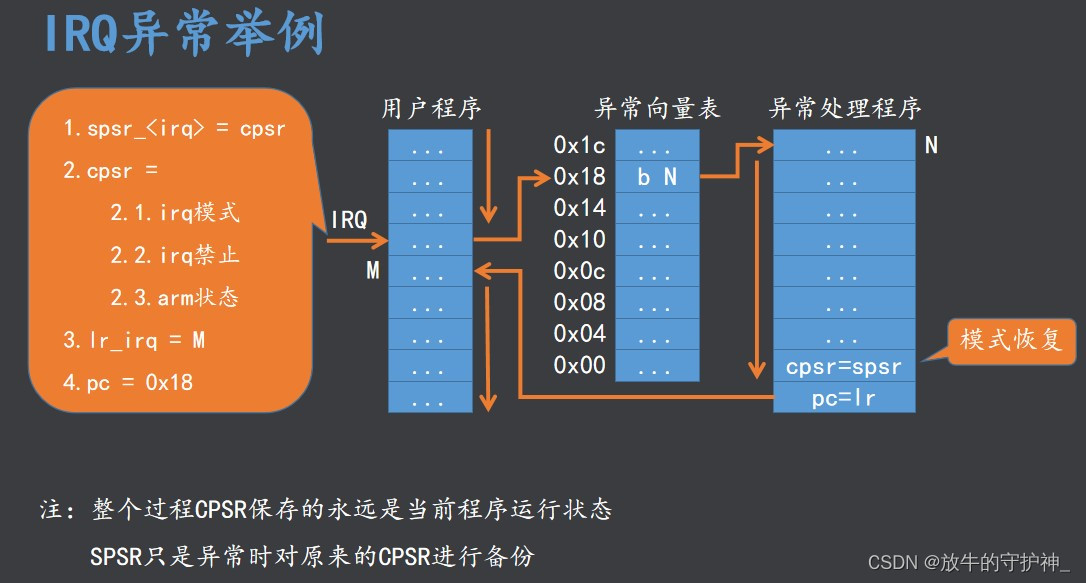

(5)IRQ异常举例

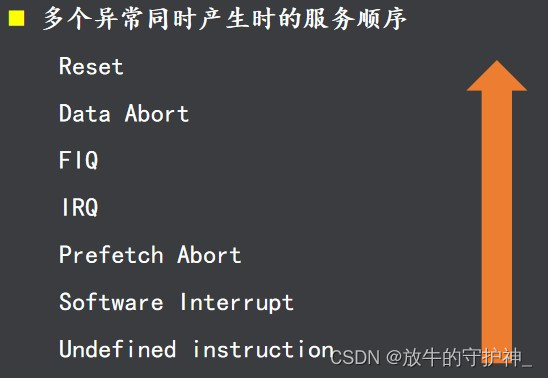

(6) 异常优先级

(7) FIQ和IRQ

1.指令的执行过程

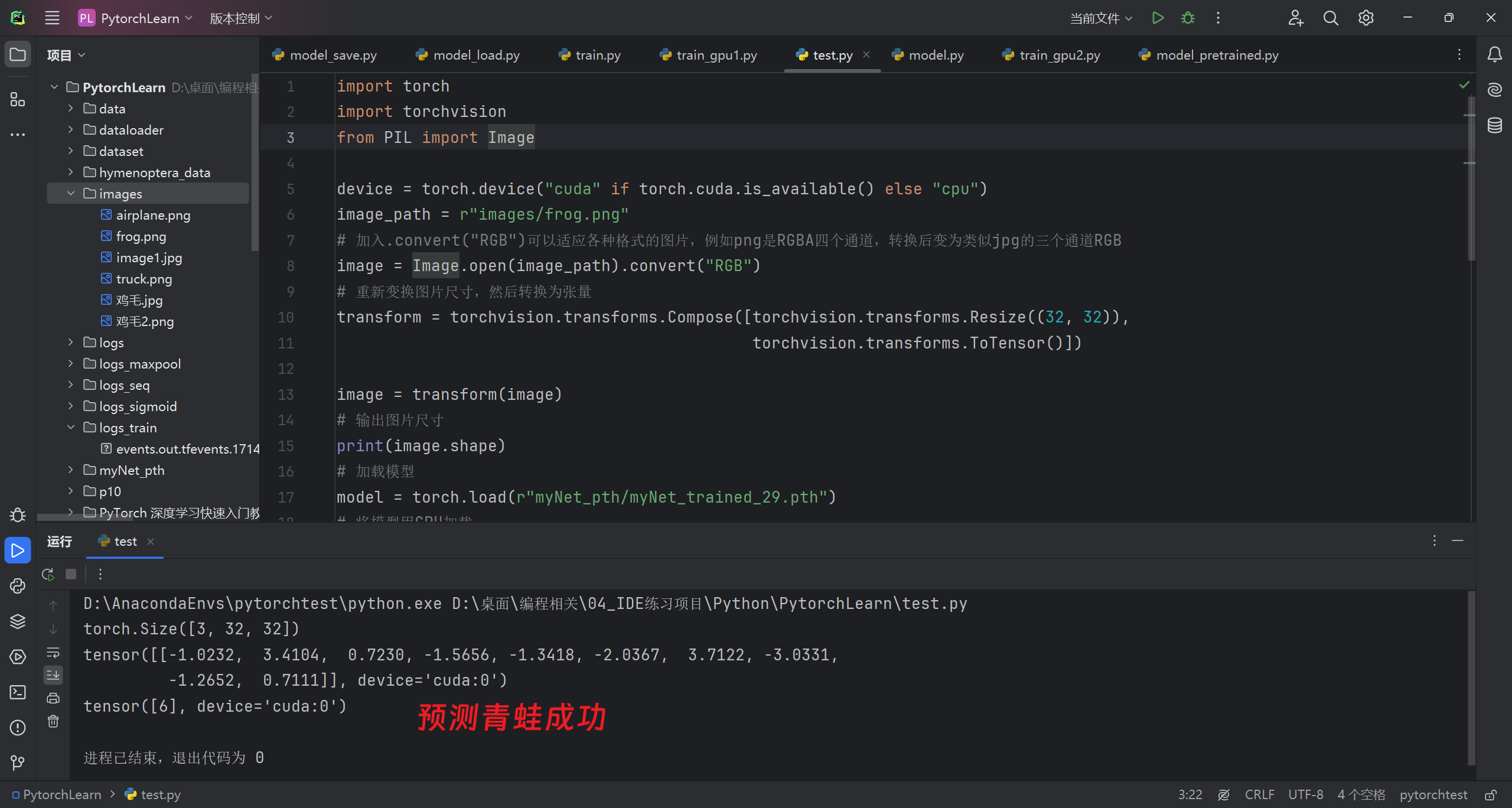

(1)一条指令的执行分为三个阶段

1.取址:

CPU将PC寄存器中的地址发送给内存,内存将其地址中对应的指令返回

到CPU中的指令寄存器(IR)

2.译码:

译码器对IR中的指令进行识别,将指令(机器码)解析成具体的运算

3.执行:

控制器控制运算器中对应的运算单元进行运算,运算结果写入寄存器

(2) 每执行一条指令后PC的值会自动增加指向下一条指令

2. ARM处理器概述

| 早先经典处理器 | 包括ARM7、ARM9、ARM11家族 |

| Cortex-A系列 | 针对开放式操作系统的高性能处理器 应用于智能手机、数字电视、智能本等高端运用 |

| Cortex-R系列 | 针对实时系统、满足实时性的控制需求 应于汽车制动系统、动力系统等 |

| Cortex-M系列 | 为单片机驱动的系统提供了低成本优化方案 应用于传统的微控制器市场、智能传感器、汽车周边等 |

3.ARM指令集

(1)指令集: 处理器能识别的指令的集合称为指令集,不同架构的处理器指令集不同,指令集是处理器对开发者提供的接口

(2)大多数ARM处理器都支持两种指令集:

| ARM指令集 | 所有指令(机器码)都占用32bit存储空间 代码灵活度高、简化了解码复杂度 执行ARM指令集时PC值每次自增4 |

| Thumb指令集 | 所有指令(机器码)都占用16bit存储空间 代码密度高、节省存储空间 执行Thumb指令集时PC值每次自增2 |

4.ARM存储模型

(1)ARM采用32位架构,基本数据类型有以下三种

| Byte(字节) | 8bits |

| Halfword(半字) | 16bits |

| Word(字) | 32bits |

(2)数据存储

Word型数据在内存的起始地址必须是4的整数倍

Halfword型数据在内存的起始地址必须是2的整数倍

注:即数据本身是多少位在内存存储时就应该多少位对齐,且ARM一般使用小端对齐

5. ARM工作模式

(1)ARM有8个基本的工作模式

| User | 非特权模式,一般在执行上层的应用程序时ARM处于该模式 |

| FIQ | 当一个高优先级中断产生后ARM将进入这种模式 |

| IRQ | 当一个低优先级中断产生后ARM将进入这种模式 |

| SVC | 当复位或执行软中断指令后ARM将进入这种模式 |

| Abort | 当产生存取异常时ARM将进入这种模式 |

| Undef | 当执行未定义的指令时ARM将进入这种模式 |

| System | 使用和User模式相同寄存器集的特权模式 |

| Monitor | 为了安全而扩展出的用于执行安全监控代码的模式 |

(2)工作模式的理解

不同模式拥有不同权限

不同模式执行不同代码

不同模式完成不同的功能

(3)ARM工作模式分类

| 按照权限 | User为非特权模式(权限较低),其余模式均为特权模式(权限较高) |

| 按照状态 | FIQ、IRQ、SVC、Abort、Undef属于异常模式,即当处理器遇到异常后 会进入对应的模式 |

6.ARM寄存器组织

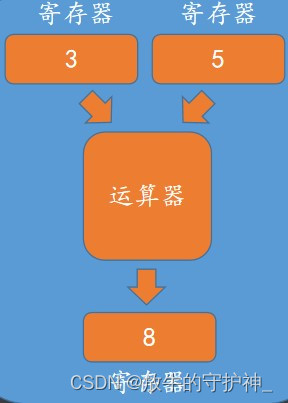

(1)寄存器

| 概念 | 寄存器是处理器内部的存储器,没有地址 |

| 作用 | 一般用于暂时存放参与运算的数据和运算结果 |

| 分类 | 包括通用寄存器、专用寄存器、控制寄存器 |

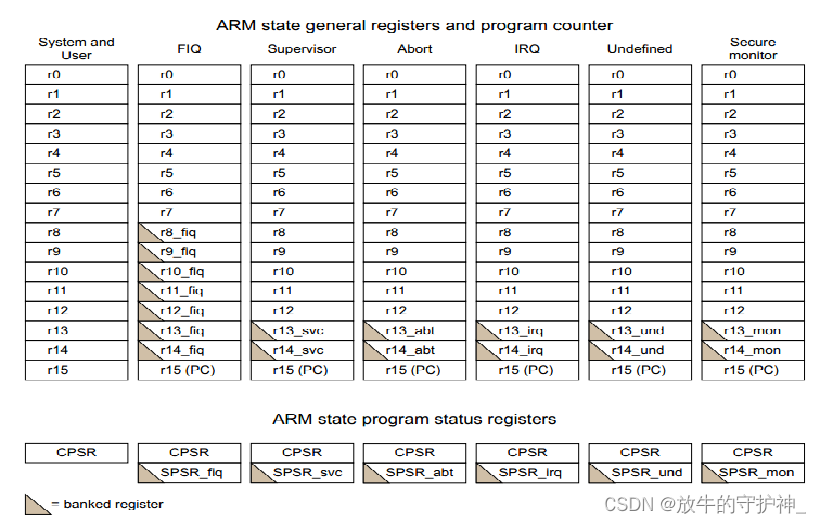

(2) ARM寄存器

在某个特定模式下只能使用当前模式下的寄存器,一个模式下特有的寄存器其他模式下不可使用

| R15(PC,Program Counter) | 程序计数器,用于存储当前取址指令的地址 |

| R14(LR,Link Register) | 链接寄存器,一般有以下两种用途: > 执行跳转指令(BL/BLX)时,LR会自动保存跳转指令下一条指令的地址,程序需要返回时将LR的值复制到PC即可实现 > 产生异常时,对应异常模式下的LR会自动保存被异常打断的指令的下一条指令的地址,异常处理结束后将LR的值复制到PC可实现程序返回 |

| R13(SP,Stack Pointer) | 栈指针,用于存储当前模式下的栈顶地址 |

| CPSR(Current Program Status Register) | 当前程序状态寄存器 |

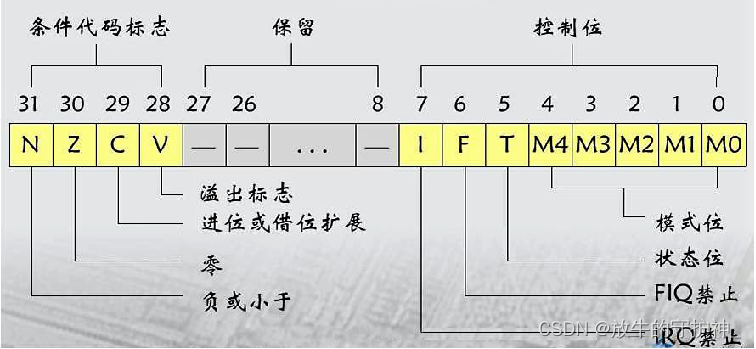

(3)CPSR寄存器

CPSR寄存器分为四个域,[31:24]为条件域用F表示、[23:16]为状态域用S表示、[15:8]为预留域用X表示、[8:0]为控制域用C表示

| Bit[4:0] | [10000]User [10001]FIQ [10010]IRQ [10011]SVC [10111]Abort [11011]Undef [11111]System [10110]Monitor |

| Bit[5] | [0]ARM状态 [1]Thumb状态 |

| Bit[6] | [0]开启FIQ [1]禁止FIQ |

| Bit[7] | [0]开启IRQ [1]禁止IRQ |

| Bit[28] | > 当运算器中进行加法运算且产生符号位进位时该位自动置1,否则为0 > 当运算器中进行减法运算且产生符号位借位时该位自动置0,否则为1 |

| Bit[29] | > 当运算器中进行加法运算且产生进位时该位自动置1,否则为0 > 当运算器中进行减法运算且产生借位时该位自动置0,否则为1 |

| Bit[30] | 当运算器中产生了0的结果该位自动置1,否则为0 |

| Bit[31] | 当运算器中产生了负数的结果该位自动置1,否则为0 |

7. ARM异常处理

(1)异常

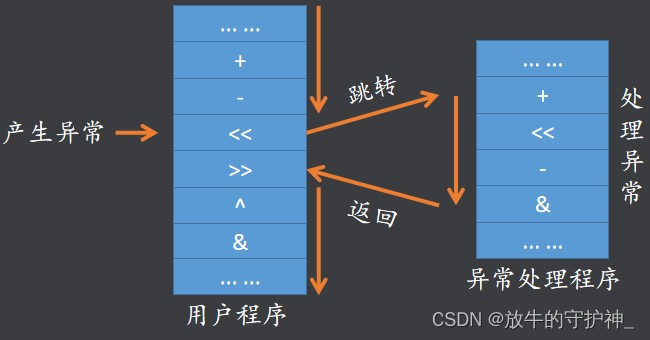

处理器在正常执行程序的过程中可能会遇到一些不正常的事件发生,这时处理器就要将当前的程序暂停下来转而去处理这个异常的事件,异常事件处理完成之后再返回到被异常打断的点继续执行程序

(2)异常源

导致异常产生的事件称为异常源

| FIQ | 快速中断请求引脚有效 |

| IRQ | 外部中断请求引脚有效 |

| Reset | 复位电平有效 |

| Software Interrupt | 执行swi指令 |

| Data Abort | 数据终止 |

| Prefetch Abort | 指令预取终止 |

| Undefined Instruction | 遇到不能处理的指令 |

(3)ARM异常模式

异常模式:在ARM的基本工作模式中有5个属于异常模式,即ARM遇到异常后会切换成对应的异常模式

(4) ARM异常响应

ARM产生异常后的动作(自动完成)

1.拷贝CPSR中的内容到对应异常模式下的SPSR_<mode>

2.修改CPSR的值

2.1.修改中断禁止位禁止相应的中断

2.2.修改模式位进入相应的异常模式

2.3.修改状态位进入ARM状态

3.保存返回地址到对应异常模式下的LR_<mode>

4.设置PC为相应的异常向量(异常向量表对应的地址)

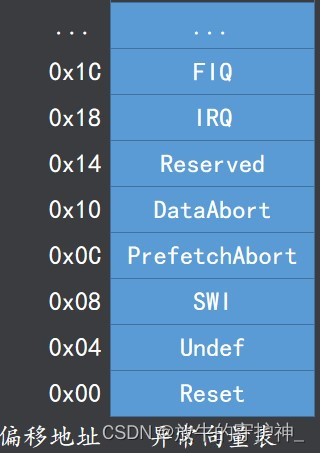

异常向量表

> 异常向量表的本质是内存中的一段代码

> 表中为每个异常源分配了四个字节的存储空间

> 遇到异常后处理器自动将PC修改为对应的地址

> 因为异常向量表空间有限一般我们不会再这里写异常处理程序,而是在对应的位置写一条跳 转指令使其跳转到指定的异常处理程序的入口

注:ARM的异常向量表的基地址默认在0x00地址但可以通过配置协处理器来修改其地址

ARM异常返回的动作(自己编写)

1.将SPSR_<mode>的值复制给CPSR, 使处理器恢复之前的状态

2.将LR_<mode>的值复制给PC ,使程序跳转回被打断的地址继续执行

(5)IRQ异常举例

(6) 异常优先级

(7) FIQ和IRQ

FIQ的响应速度比IRQ快

1. FIQ在异常向量表位于最末 ,可直接把异常处理写在异常向量表之后,省去跳转

2. FIQ模式有5个私有寄存器(R8-R12) ,执行中断处理程序前无需压栈保存寄存器,可直接处理中断

3. FIQ的优先级高于IRQ

3.1 两个中断同时发生时先响应FIQ

3.2 FIQ可以打断RIQ,但RIQ不能打断FIQ

![[Kubernetes] sealos部署 K8s 集群](https://img-blog.csdnimg.cn/direct/485bb6dbead64719a9f011cbf56d07df.png)