开发环境:Vivado2021.2 ; Windows with Cygwin

HDL版本:hdl_2021_r2 GitHub - analogdevicesinc/hdl at hdl_2021_r2

no-OS版本:no_OS-2021_R2 GitHub - analogdevicesinc/no-OS at 2021_R2

1.创建hdl

详细步骤参见参考链接1;下文记录了开发过程中遇到的问题和解决方法。

AD3552的工程名字是ad3552r_evb,位于hdl->projects目录下。但是该工程在hdl_2022_r2之前(包含HDL_2022_r2)的projects目录下是不存在的(本人猜测,有可能在其他目录下),在主干main中的hdl->projects目录中存在ad3552r_evb(查看日志,ad3552r_evb是2023年10月2日提交的)。

由于本人的开发环境是Vivado2021.2,因此不排除存在一定的兼容性问题。基于Vivado2021.2的开发步骤如下:

- 将hdl的main主干下载到本地电脑。

- 查看hdl-main>projects->ad3552r_evb中的makefile(zed文件夹下的makefile),看到建立工程的依赖项在hdl-hdl_2021_r2中均存在。考虑尝试将hdl-main>projects->ad3552r_evb拷贝至hdl-hdl_2021_r2->projects目录下,然后运行make,遇到问题再处理。

- 将hdl-main>projects->ad3552r_evb拷贝至hdl-hdl_2021_r2->projects目录下,然后运行make,处理工程建立中遇到的问题。

- 重新make,遇到问题再处理,直至make成功。

步骤3中遇到的问题:

综合过程中,提示up_dac_common的端口错误。比对hdl-hdl_2021_r2和hdl-main的代码,发现hdl-main中的up_dac_common.v新增了“DAC custom read/write interface”。将该文件中的改动同步至hdl-hdl_2021_r2中,重新make,综合、布局布线OK。

2. 创建no-OS

详细步骤参见参考链接2;下文记录了开发过程中遇到的问题和解决方法。

no_OS-2021_R2中包含了ad3552工程文件(no-OS->projects->ad3552r_fmcz)和驱动文件(no-OS->drivers->dac->ad3552r)。这里,与hdl中的情况不一样,也是奇怪的地方(所以推测hdl中的ad3552r_evb应该之前就存在,至少与no-OS中的ad3552r_fmcz同时存在,只是位置不在hdl中)。

基于Vitis2021.2的开发步骤:

1. 在Vivado2021.2中导出system_top.xsa文件至no-OS->projects->ad3552r_fmcz目录下

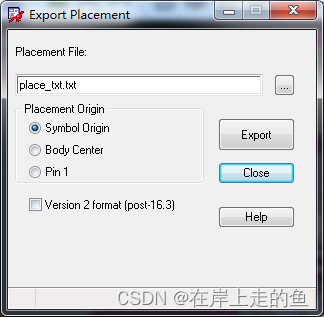

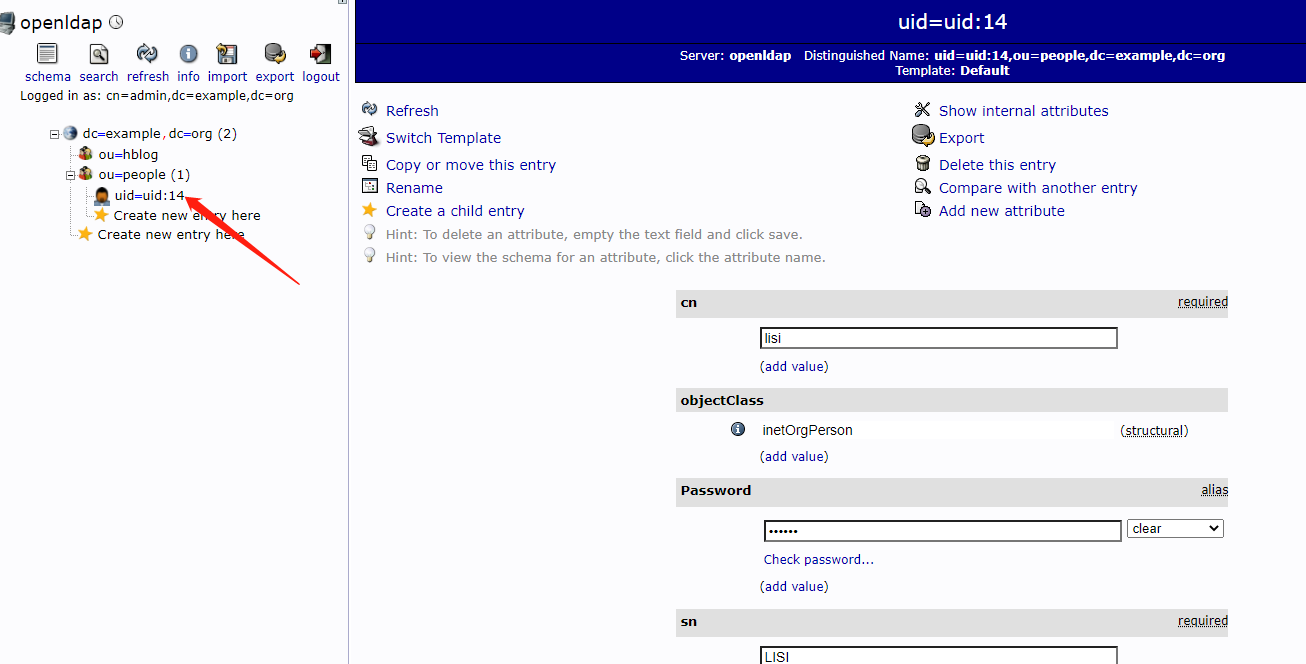

2. 打开CMD(重要注意:不要使用windows PowerShell;以管理员身份运行CMD),如下图所示。

3. 在CMD中运行 Vitis安装目录下的setting64.bat(具体位置举例: I:\Xilinx\Vitis\2021.2\settings64.bat);之后,在同一个CMD中,切换至no-OS->projects->ad3552r_fmcz目录下,运行make。

4. 处理make中遇到的问题。我所遇到的问题有两个。

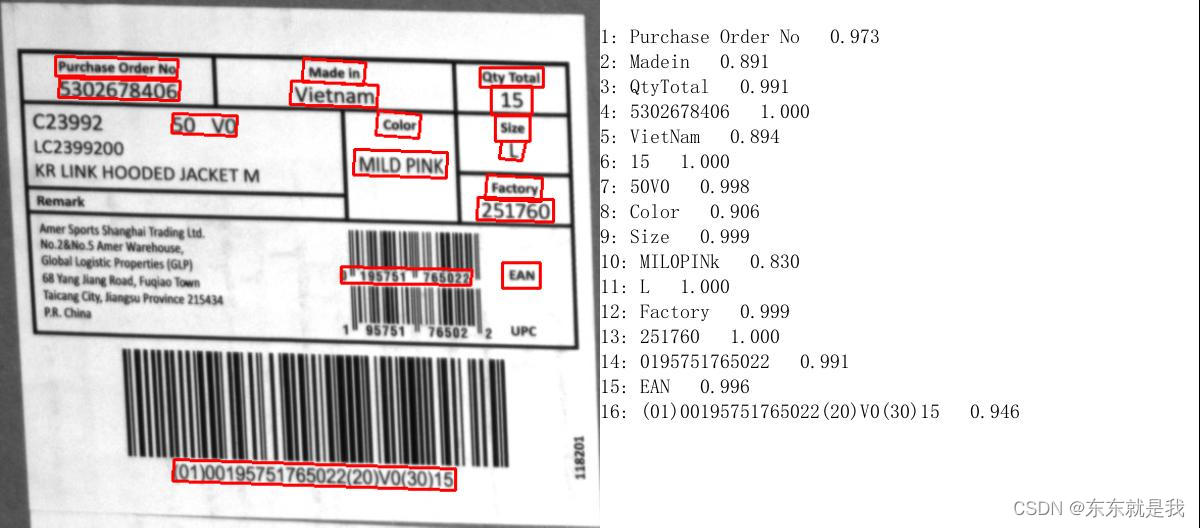

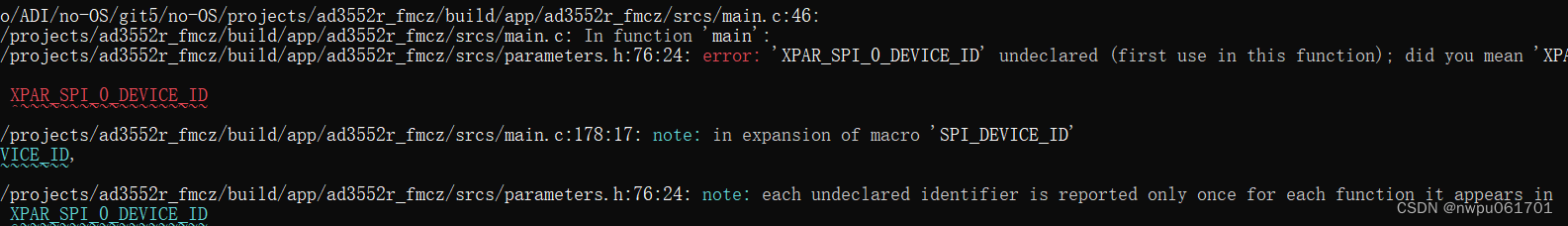

一个是ad3552r_fmcz->srcs文件夹下的parameters.h中XPAR_SPI_0_DEVICE_ID无法识别;解决方法是,查看github修改日志,将XPAR_SPI_0_DEVICE_ID替换为XPAR_PS7_SPI_0_DEVICE_ID。

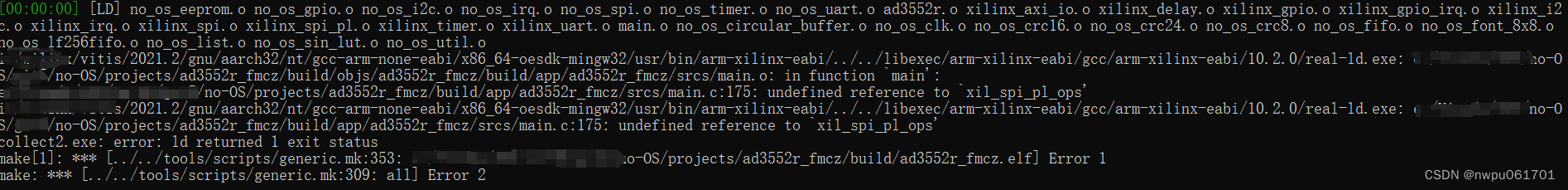

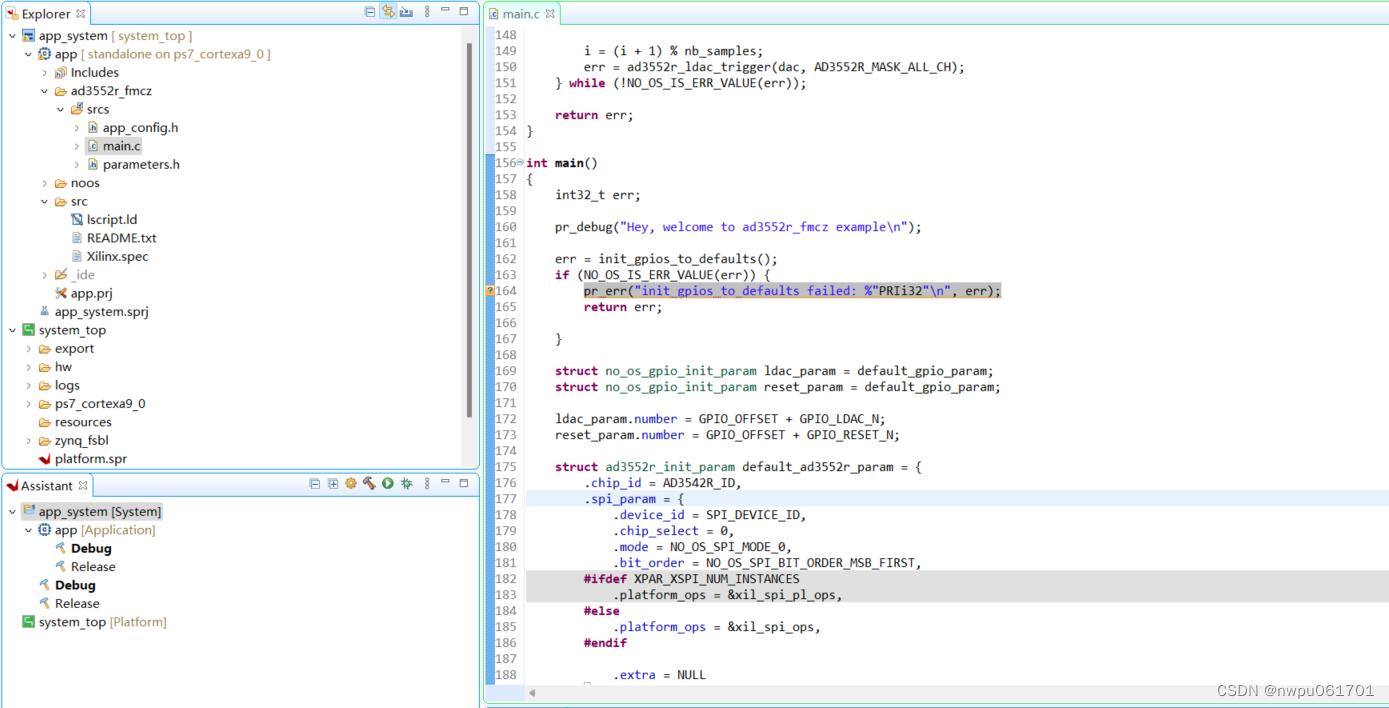

另一个问题是ad3552r_fmcz->srcs文件夹下的main.c中xil_spi_pl_ops在链接时无法识别。

查看github修改日志,对代码做如下修改。

.spi_param = {

.device_id = SPI_DEVICE_ID,

.chip_select = 0,

.mode = NO_OS_SPI_MODE_0,

.bit_order = NO_OS_SPI_BIT_ORDER_MSB_FIRST,

.platform_ops = &xil_spi_pl_ops,

.extra = NULL

},

//上述代码,修改为

.spi_param = {

.device_id = SPI_DEVICE_ID,

.chip_select = 0,

.mode = NO_OS_SPI_MODE_0,

.bit_order = NO_OS_SPI_BIT_ORDER_MSB_FIRST,

#ifdef XPAR_XSPI_NUM_INSTANCES

.platform_ops = &xil_spi_pl_ops,

#else

.platform_ops = &xil_spi_ops,

#endif

.extra = NULL

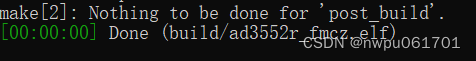

},5. make的过程中解决问题,最终make成功

6. 在同一个CMD中输入命令make sdkopen,打开Vitis。跳过Vitis的欢迎界面(需要手动点击),可以看到AD3552的Vitis工程。

后续

整体工程的运行还未开展,待验证。

参考链接

1. Building HDL [Analog Devices Wiki]

2. No-OS Build Guide [Analog Devices Wiki]

3. AXI_AD3552R [Analog Devices Wiki]

4. ADRV9002官方例程开发过程中遇到的问题_adrv9002内部arm无法启动-CSDN博客