目录

1、复位过程

1.1、概述

1.2、复位产生模块

1.2.1、上电复位

1.2.2、破坏性复位

1.2.3、功能复位

1.3、芯片复位及引导概述

1.4、重置和启动流程图

1.5、复位块序列

2、上电复位

3、破坏性复位

4、功能复位

5、设备配置格式(DCF)

6、重置专题

6.1、重置引脚行为和细节

6.2、复位后的设备状态

7、启动过程

7.1、SBAF中的引导流程图

7.2、应用程序启动顺序

8、STARTUP_ARMCM7.C文件解析

9、CMSIS_GCC.H文件解析

1、复位过程

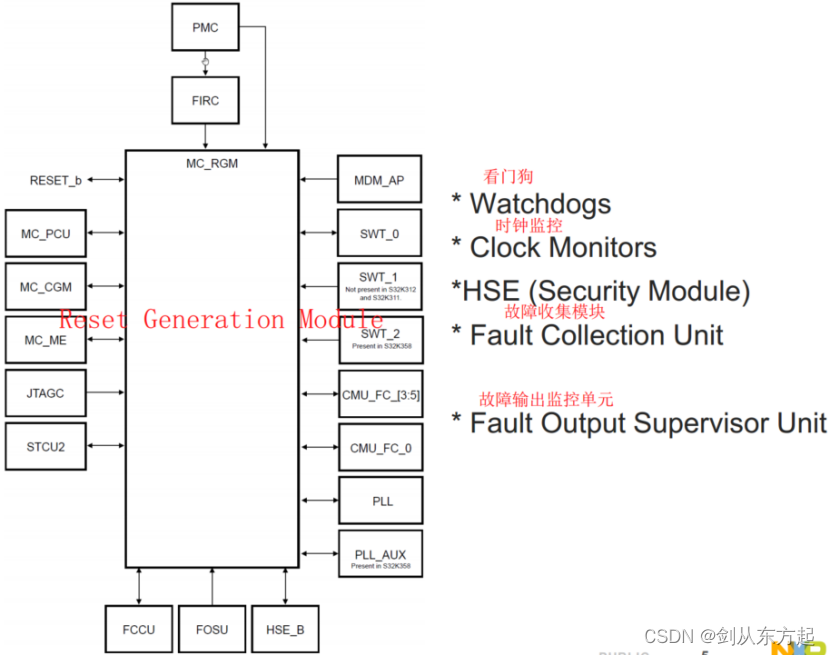

1.1、概述

从任何类型的重置到 HSE Core 第一条指令之前。

Power Managment(PMC):电源管理

Reset_b external signal :复位_b外部信号

Power control Unit (PCU):电源控制单元

Clock Generation Module (CGM):时钟产生模块

Mode_Entry(ME):模块入口

Self Test Control Unit (STCU):自检控制单元

顶层复位框图如下:

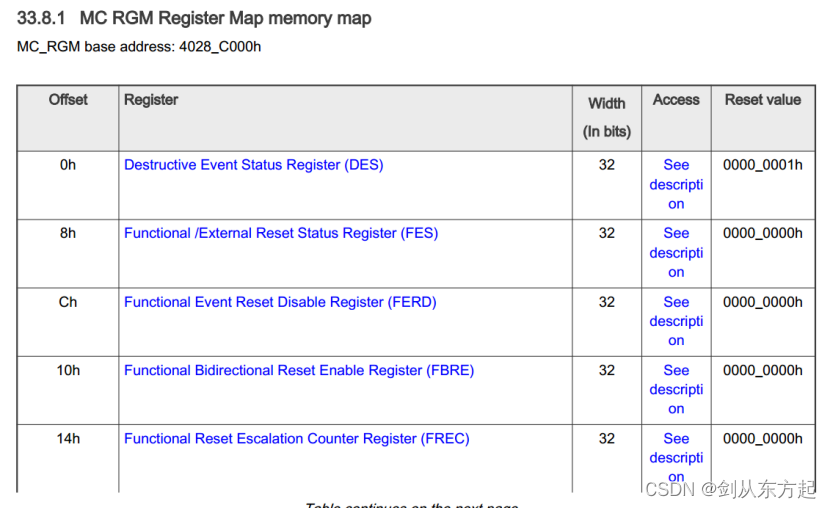

1.2、复位产生模块

·集中不同的复位源,管理芯片复位顺序

·各种寄存器监控和控制复位顺序

功能

·支持破坏性复位

·支持功能复位

·为重置事件提供状态标志

·将复位引脚事件转换为中断事件

·可编程的循环复位事件升级

·双向复位引脚配置

·软件可配置的外部复位断言控制

上述这些在寄存器里面有很明显的显示

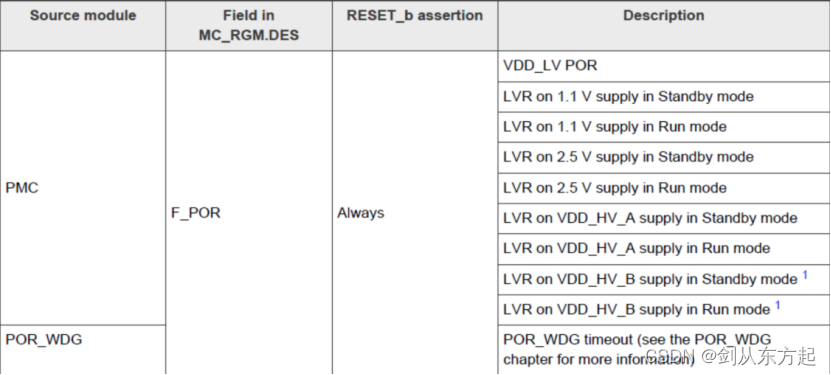

1.2.1、上电复位

·当电源被应用时,整个设备复位

· 所有PMC(电源管理控制器)POR和LVR被合并成一个单一的MCU POR。

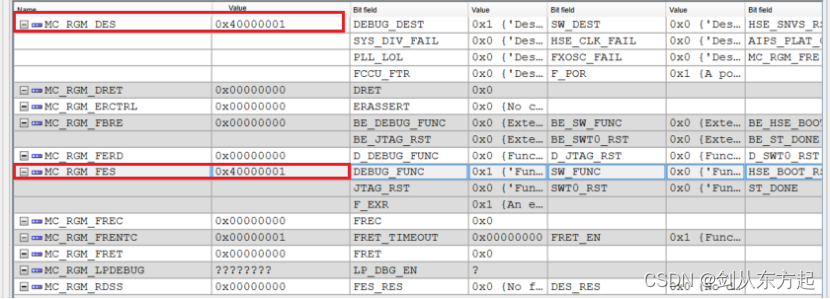

上电复位会有以下两个寄存器的数据位置位,其中第一个表示上电复位,第二个表示有外部复位动作发生,第二个相当于一个总的复位标识。

1.2.2、破坏性复位

·与严重错误或功能障碍有关的。

·应用完全复位序列,从DEST0开始,确保数字和模拟模块的安全启动状态。内存内容必须考虑为未知状态。

破坏性复位包含下面

所有破坏性复位都可以升级(这里的升级什么意思,不怎么明白),但只有PLL LOL破坏性复位可以降级为中断(参见破坏性复位事件旁路PLL LOL破坏性复位旁路详细信息)。

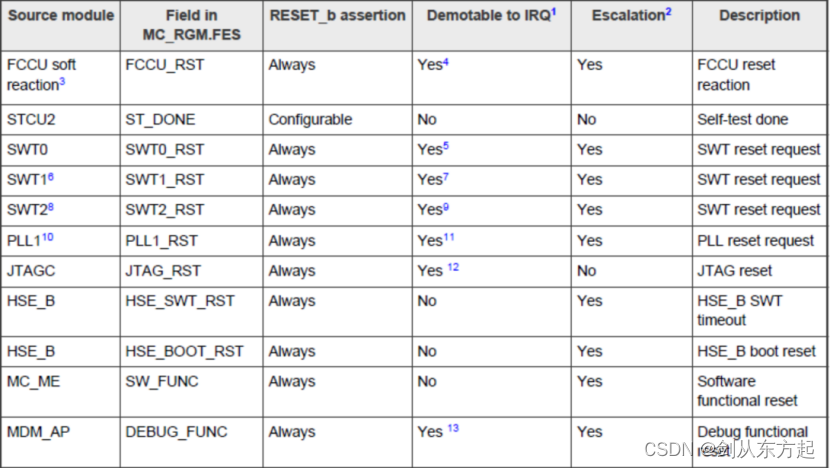

1.2.3、功能复位

·与不太严重的错误或功能障碍有关的

·部分复位序列应用,从FUNCm0开始。大多数数字模块正常复位,而模拟模块或特定数字模块(如调试模块、闪存模块)的状态以及系统内存内容被保留。

主动调用复位函数的时候产生以下标志位变化

Power_Ip_MC_ME_SocTriggerResetEvent(POWER_IP_FUNC_RESET_MODE);

看门狗复位产生以下标志位变化

注意以上标志位的变化,必须是断电才能清除,软复位并不可以清除

功能复位包含下面

1.3、芯片复位及引导概述

sBAF,或称为安全引导辅助固件(Secure Boot Assist Firmware),是NXP S32K3微控制器系列中的一个功能。它是一种固件,用于在微控制器启动时提供安全功能,如验证应用程序的完整性和真实性。这是确保系统安全的重要步骤,特别是在需要符合功能安全标准的汽车应用中。

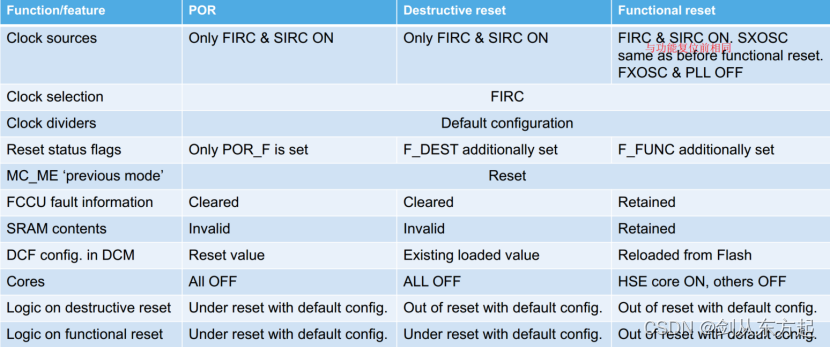

在S32K3系列中,如果主晶体出现故障导致设备复位,设备将以默认配置启动,并且默认的时钟源是FIRC(快速内部参考时钟)。因此,晶体故障不会影响看门狗在复位后的功能,看门狗计数器会从SIRC(慢速内部参考时钟)运行。

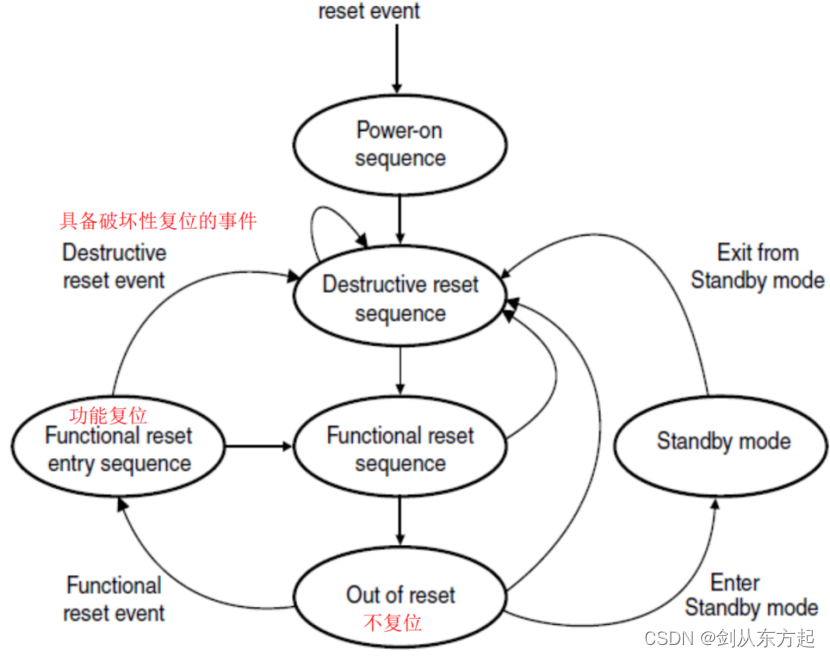

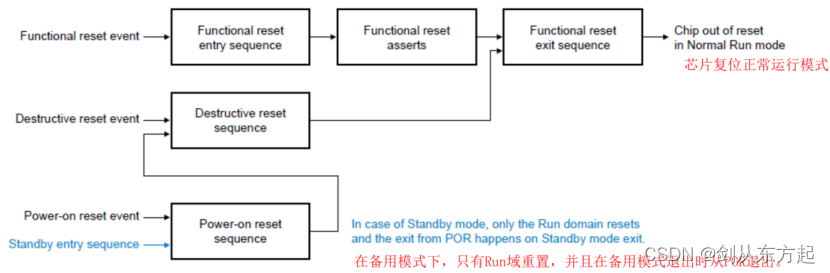

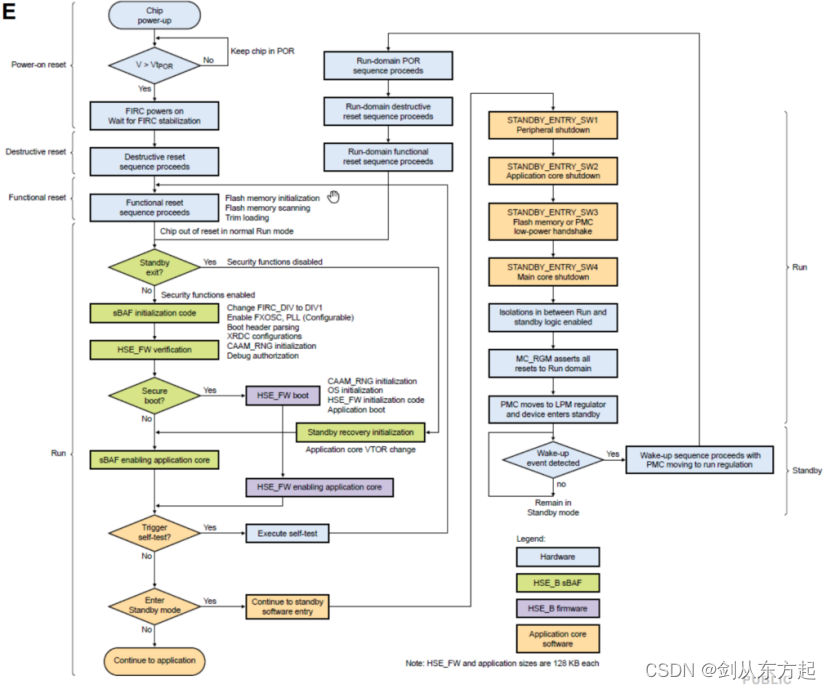

1.4、重置和启动流程图

对于每个重置事件,在被MC RGM捕获后,立即发生以下操作:

·相应的重置事件状态位将在 MC RGM 中设置。MC RGM.DES 寄存器和 MC RGM. FES 寄存器。

·芯片引脚进入默认状态。请参阅芯片《参考手册》中所附的 IO_Signal_Multiplexing 页面。

·RESET_b 引脚由芯片确认。

·根据当前状态和复位事件类型,按上表所述进入复位序列。

1.5、复位块序列

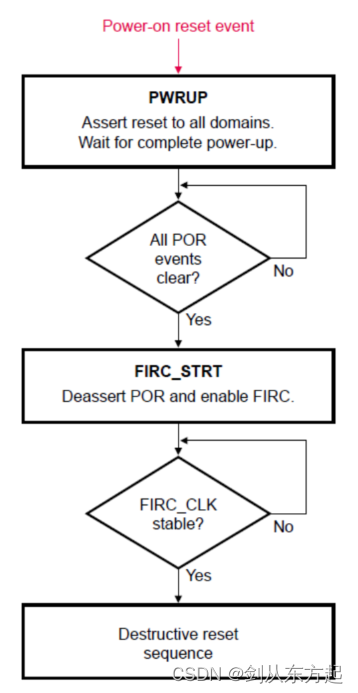

2、上电复位

上电阶段

当任何一个 POR 源被指定时输入,芯片等待上电序列完成,当所有的POR源被清除时退出。

FIRC_STRT阶段(快速时钟)

一旦芯片退出PWRUP阶段就进入,FIRC启用;时钟稳定后可用(此阶段的持续时间取决于FIRC稳定计数器的值),一旦FIRC时钟退出可用,破坏性重置程序进入此阶段出口。

PMC监控PMC 代表 电源管理控制器 (Power Management Controller)

MCU反应:功能复位或中断(通过裂化装置配置)

·PMC 1.1V GNG

·PMC 2.5V GNG

·GNG = Go/NoGo传感器,用于检测低电压状态

MCU反应:中断(通过PMC寄存器可配置)

·LVDIE: LVD5AF, LVD15F在进入LPM之前被禁用(

在S32K312单片机中,LPM 代表 低功耗模式 (Low Power Mode)。)

− HVDIE: HVDAF, HVDBF, HVD11F, etc.

3、破坏性复位

DEST0阶段(DEST 是指 Destructive Reset)

·对除POR和调试(JCOMP和POR)之外的所有域指定重置

·等待所有破坏性重置事件被清除

·等待FIRC_CLK的最小破坏性重置指定持续时间为8个周期

·破坏性重置在此阶段完成时被取消断言

4、功能复位

功能复位序列

进入时刻:·任何功能重置事件。·任何在DEST0阶段完成后的POR/破坏性复位事件。·备用输入协议序列

FUNC0 ~ FUNC6:功能复位进入顺序

FUNC7 ~ FUNC11:功能复位退出顺序

功能复位进入顺序

·FUNC0: HSE隔离HSE内存。对FLL事件的FCCU故障监控和CMU监控被屏蔽

·FUNC1: X-bar被禁用

·FUNC2: MC_CGM hw时钟复用器切换到FIRC时钟

·FUNC3: MC_CGM hw时钟多路分频器使用默认值

·FUNC4:锁相环同步关断

·FUNC5: FXOSC同步关闭

·FUNC6:使能LBIST模块和破坏性复位模块的时钟,以满足同步复位要求

功能复位退出顺序

·FUNC7:功能复位断言,触发64 FIRC时钟计数器,使时钟具有同步复位要求的模块。闪存在这个阶段完成后会被重置

·FUNC8: Flash-MC_RGM握手

·FUNC9: DCM发起扫描flash DCF记录,设备配置表在RM中作为《S32K3xx_dcf_sheet.xlsx》附件,描述了设备的DCF记录

·FUNC10:DCM启动模拟块的修整加载序列

·FUNC11: RGM停止驱动RESET_B并检查RESET_B是否没有在外部断言。

如果开启了低功耗调试,MC_RGM会等待调试确认。

5、设备配置格式(DCF)

设备配置格式(DCF)记录用于在系统启动期间配置设备中的某些寄存器,同时复位信号被断言。

详细细节定义在

DCF结构

S32K3的DCF功能是什么?

S32K3的DCF(Device Configuration File)功能是用于配置微控制器的一种机制。在NXP的S32K3系列微控制器中,DCF可以用来配置UTEST(User Test)区域的各种设置,例如禁用或启用锁步模式(lockstep mode)。根据NXP社区的讨论,DCF记录可以通过修改UTEST杂项寄存器(UTEST Miscellaneous Register)来实现这些配置。

例如,如果您想要在K344微控制器上禁用锁步模式,您可以查看参考手册中附带的S32K3xx_DCF_clients.xlsx文件,特别是Utest DCF Client Register Bits标签页,以了解如何清除LOCKSTEP_EN位。这个过程需要加载新的DCF记录,其中LOCKSTEP_EN位被清除,从而改变微控制器的行为。

此外,S32K3系列微控制器提供了高性能和功能安全,符合ISO26262标准,达到ASIL D安全等级,适用于需要高级功能安全、信息安全和软件支持的工业和汽车应用。DCF功能是实现这些安全要求的关键部分,允许开发者根据特定应用的需要来配置和调整微控制器的行为。

6、重置专题

破坏性复位升级

·破坏性复位升级条件导致设备保持复位状态。破坏性重置升级由DCF客户端配置。

功能复位升级

功能复位升级使设备经历破坏性复位,最终处于复位状态。重置升级阈值计数由RGM重置升级软件配置配置。

功能复位升级计数器示意图如下:

破坏性复位升级计数器:

6.1、重置引脚行为和细节

·RESET引脚功能混合到PTA5

·需要在DCM(设备配置模块)中配置

·从DCF记录中加载的默认设置被重置

·在破坏性复位期间,Pad状态=低

·双向功能

·所有 POR 源在激活时都会断言 RESET_B。POR 不能降级为 IRQ。

·所有破坏性重置源在激活时始终断言reset_B。破坏性重置

不能降级为IRQ。

6.2、复位后的设备状态

7、启动过程

SBAF(安全引导辅助流)功能

·安全和非安全启动模式

·应用程序引导核心选择

·芯片LC(生命周期)进步

·加密FDK (Firmware Delivery Key)发放

·调试授权

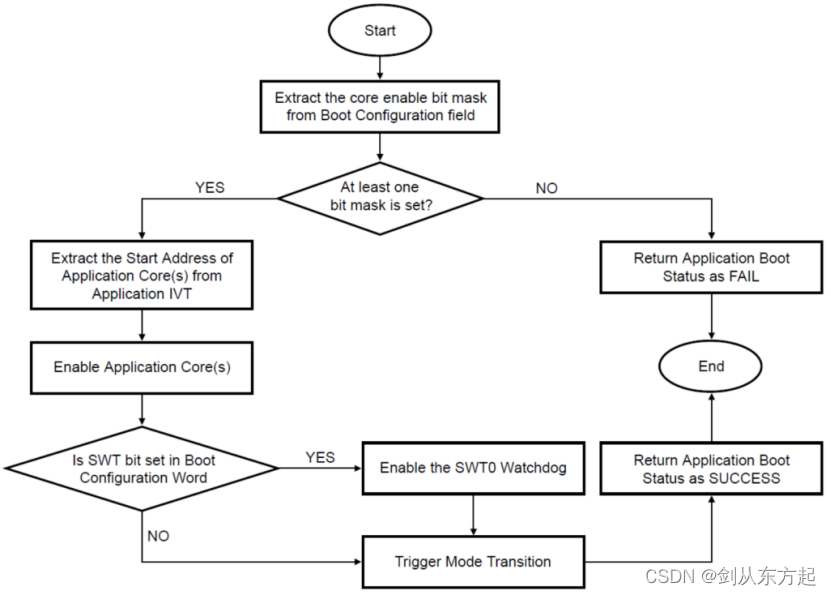

7.1、SBAF中的引导流程图

Ivt(图像向量表)头结构[boot_header.c]

/******************************************************************************

* Boot header

******************************************************************************/

typedef const struct

{

const uint32_t Header; /* Header of boot header structure */

const uint32_t BootConfig; /* Boot Configuration Word */

const uint32_t Reserved3; /* Reserved */

const uint32_t* CM7_0_StartAddress; /* Start address of application on CM7_0 core */

const uint32_t Reserved4; /* Reserved */

const uint32_t* CM7_1_StartAddress; /* Start address of application on CM7_1 core */

const uint32_t Reserved5; /* Reserved */

const uint32_t* CM7_2_StartAddress; /* Start address of application on CM7_2 core */

const uint32_t* XRDCConfig_StartAddress; /* Address of XRDC configuration data */

const uint32_t* LCConfig; /* Address of LC configuration */

const uint32_t Reserved1; /* Reserved */

const uint32_t* HseFwHeader_StartAddress; /* Start address of HSE-FW image */

const uint8_t Reserved[192]; /* Reserved for future use */

const uint8_t CMAC[16]; /* CMAC */

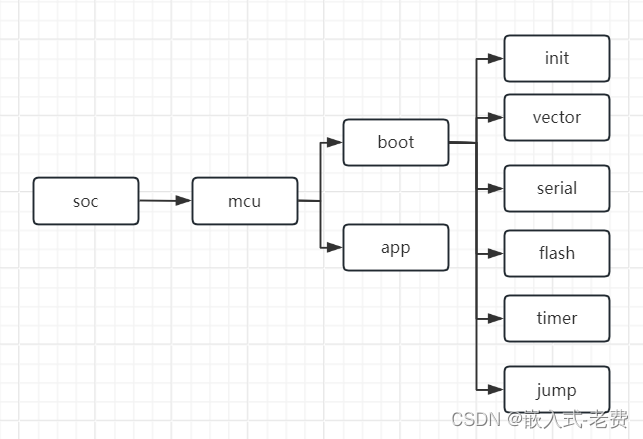

} boot_header_t;7.2、应用程序启动顺序

上电序列如下图

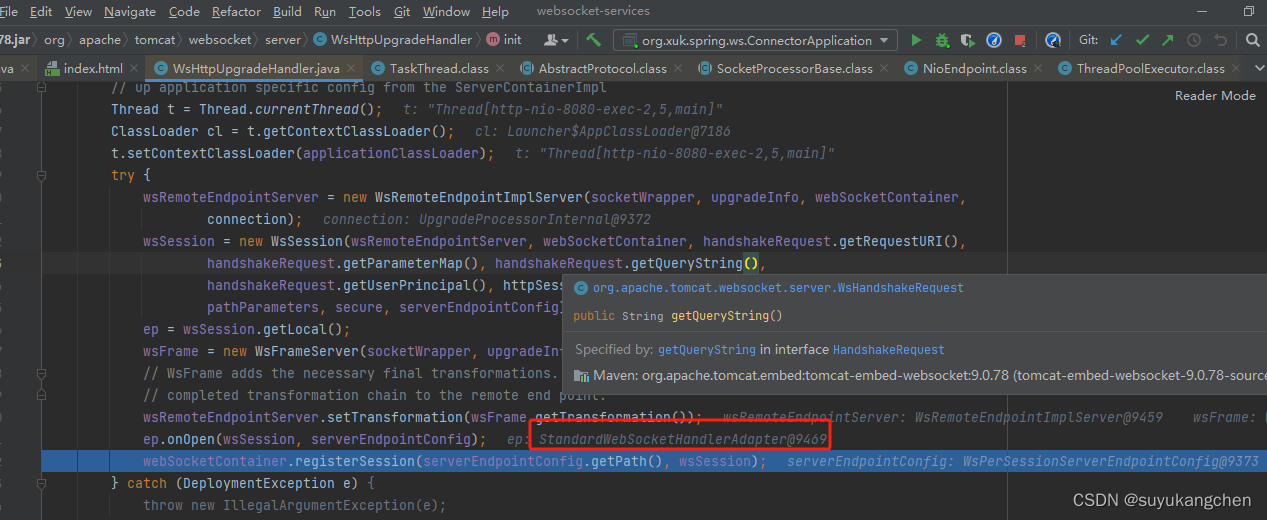

8、STARTUP_ARMCM7.C文件解析

extern const pFunc __VECTOR_TABLE[240];

const pFunc __VECTOR_TABLE[240] __VECTOR_TABLE_ATTRIBUTE =

{

(pFunc)(&__INITIAL_SP), /* Initial Stack Pointer */

Reset_Handler, /* Initial Program Counter: Reset Handler */

NMI_Handler, /* -14 NMI Handler */

HardFault_Handler, /* -13 Hard Fault Handler */

MemManage_Handler, /* -12 MPU Fault Handler */

BusFault_Handler, /* -11 Bus Fault Handler */

UsageFault_Handler, /* -10 Usage Fault Handler */

0, /* Reserved */

0, /* Reserved */

0, /* Reserved */

0, /* Reserved */

SVC_Handler, /* -5 SVCall Handler */

DebugMon_Handler, /* -4 Debug Monitor Handler */

0, /* Reserved */

PendSV_Handler, /* -2 PendSV Handler */

SysTick_Handler, /* -1 SysTick Handler */

/* Interrupst */

...

};

/*----------------------------------------------------------------------------

Reset Handler called on controller reset

*----------------------------------------------------------------------------*/

#if defined (__ICCARM__)

#pragma diag_suppress=Pe1305

#endif

void __NAKED __NO_RETURN Reset_Handler(void)

{

#ifdef INIT_STDBY_RAM

register uint32_t cnt;

register uint64_t *pDest;

/* Initialize STANDBY RAM if chip comes from POR */

if (MC_RGM->DES & MC_RGM_DES_F_POR_MASK)

{

/* Initialize STANDBY RAM */

cnt = (( uint32_t)(&__STDBYRAM_SIZE)) / 8U;

pDest = (uint64_t *)(&__STDBYRAM_START);

while (cnt--)

{

*pDest = (uint64_t)0xDEADBEEFCAFEFEEDULL;

pDest++;

}

MC_RGM->DES = MC_RGM_DES_F_POR_MASK; /* Write 1 to clear F_POR */

}

#endif

#ifndef __EARLY_INIT

/**

\brief Early system init: ECC, TCM etc.

\details This default implementation initializes ECC memory sections

relying on .ecc.table properly in the used linker script.

*/

__STATIC_FORCEINLINE void __cmsis_cpu_init(void)

{

#if defined (__ECC_PRESENT) && (__ECC_PRESENT == 1U)

typedef struct {

uint64_t* dest;

uint64_t wlen;

} __ecc_table_t;

extern const __ecc_table_t __ecc_table_start__;

extern const __ecc_table_t __ecc_table_end__;

for (__ecc_table_t const* pTable = &__ecc_table_start__; pTable < &__ecc_table_end__; ++pTable) {

for(uint64_t i=0u; i<pTable->wlen; ++i) {

pTable->dest[i] = 0xDEADBEEFFEEDCAFEUL;

}

}

#endif

}

*----------------------------------------------------------------------------

System initialization function

*----------------------------------------------------------------------------*/

void SystemInit (void)

{

#if defined (__VTOR_PRESENT) && (__VTOR_PRESENT == 1U)

SCB->VTOR = (uint32_t) &__VECTOR_TABLE;

#endif

#if defined (__FPU_USED) && (__FPU_USED == 1U)

SCB->CPACR |= ((3U << 10U*2U) | /* enable CP10 Full Access */

(3U << 11U*2U) ); /* enable CP11 Full Access */

#endif

#ifdef UNALIGNED_SUPPORT_DISABLE

SCB->CCR |= SCB_CCR_UNALIGN_TRP_Msk;

#endif

SystemCoreClock = SYSTEM_CLOCK;

}9、CMSIS_GCC.H文件解析

#ifndef __PROGRAM_START

/**

\brief Initializes data and bss sections

\details This default implementations initialized all data and additional bss

sections relying on .copy.table and .zero.table specified properly

in the used linker script.

*/

__STATIC_FORCEINLINE __NO_RETURN void __cmsis_start(void)

{

extern void _start(void) __NO_RETURN;

typedef struct {

uint32_t const* src;

uint32_t* dest;

uint32_t wlen;

} __copy_table_t;

typedef struct {

uint32_t* dest;

uint32_t wlen;

} __zero_table_t;

extern const __copy_table_t __copy_table_start__;

extern const __copy_table_t __copy_table_end__;

extern const __zero_table_t __zero_table_start__;

extern const __zero_table_t __zero_table_end__;

for (__copy_table_t const* pTable = &__copy_table_start__; pTable < &__copy_table_end__; ++pTable) {

for(uint32_t i=0u; i<pTable->wlen; ++i) {

pTable->dest[i] = pTable->src[i];

}

}

for (__zero_table_t const* pTable = &__zero_table_start__; pTable < &__zero_table_end__; ++pTable) {

for(uint32_t i=0u; i<pTable->wlen; ++i) {

pTable->dest[i] = 0u;

}

}

_start();

}