本文展示了MMCM的一些使用模型(同样适用于PLL),如时钟网络去偏斜、具有内部反馈的MMCM和零延迟缓冲区等。

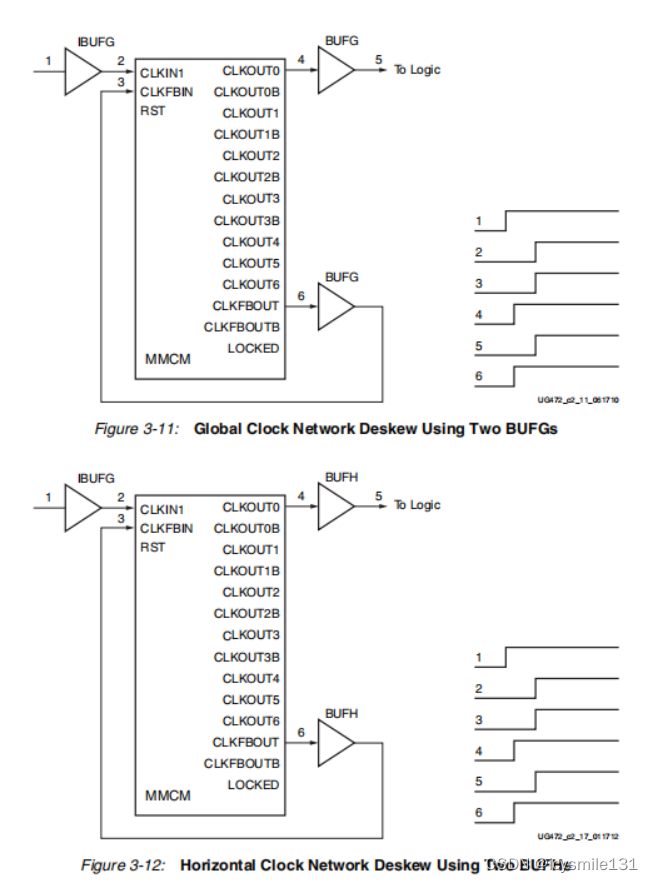

1、时钟网络去偏斜(Clock Network Deskew)

MMCM的主要用途之一是用于时钟网络去偏斜。图3-11和图3-12展示了在这种模式下的MMCM。来自CLKOUT计数器之一的时钟输出用于驱动fabric内部和(或)I/O的逻辑。反馈计数器用于控制输入时钟和输出时钟之间的精确相位关系(例如,如果需要90°相位偏移)。相关时钟波形显示在右侧,适用于输入时钟和输出时钟需要相位对齐的情况。图3-11中的配置最为灵活,但它确实需要两个全局时钟网络。

CLKFBOUT输出可用于提供反馈时钟信号。当MMCM驱动BUFG和BUFH时,只有同样在反馈路径中使用的那个时钟缓冲器会被去偏移。

在实际应用中,需要确保输入到PFD的两个时钟信号(即参考时钟和反馈时钟)具有相同的频率。这是因为PFD(相位频率检测器)是用来检测这两个时钟信号之间的相位差和频率差的,如果它们的频率不匹配,PFD将无法正常工作,从而导致MMCM无法正确地进行时钟去偏斜和相位对齐。

举一个例子,如果输入频率ƒIN为166 MHz,D=1,M=6,O=2,那么VCO的频率将是996 MHz,时钟输出频率将是498 MHz。由于在反馈路径中的M值为6,所以PFD的两个输入频率都是166 MHz。

在另一个更复杂的场景中,输入频率为66.66 MHz,D=2,M=30,O=4。在这种情况下,VCO的频率是1000 MHz,CLKOUT输出频率是250 MHz。因此,PFD的反馈频率是1000/30,即33.33 MHz,这与PFD的66.66 MHz/2输入时钟频率相匹配。

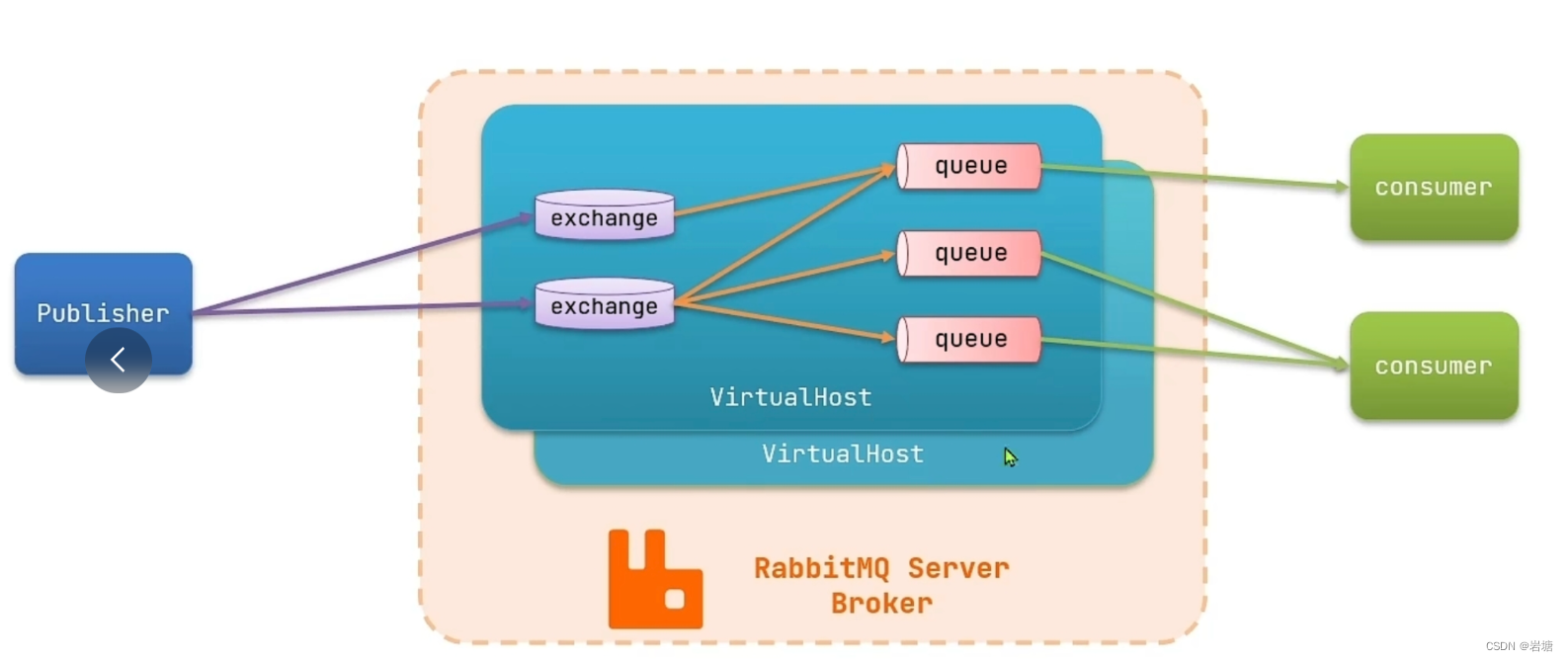

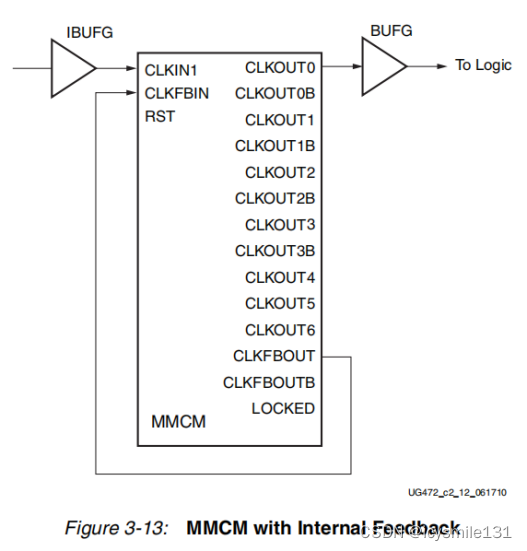

2、具有内部反馈的MMCM

当MMCM用作合成器或抖动滤波器,并且MMCM输入时钟和MMCM输出时钟之间不需要特定的相位关系时,MMCM的反馈可以是内部的。由于反馈时钟不会受到核心供电噪声的影响,MMCM的性能会得到提升。当然,CLKIN信号和BUFG上引入的噪声仍然存在(如图3-13所示)。

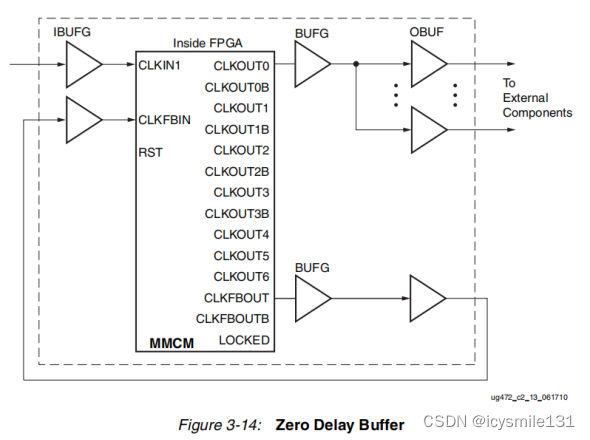

3、零延迟缓冲区

MMCM也可以用来生成零延迟缓冲时钟。零延迟缓冲区对于那些需要将单个时钟信号分发到多个目的地,且这些目的地之间需要低偏斜的应用来说是非常有用的。这种配置如图3-14所示。在这里,反馈信号驱动外部芯片,而板上的迹线反馈(the board trace feedback)被设计来匹配到外部组件的迹线(trace)。在这种配置中,假设时钟边沿在FPGA的输入端和外部组件的输入端是对齐的。CLKIN和CLKFBIN的输入时钟缓冲区必须位于同一bank中。

零延迟缓冲区的概念是指,通过适当的配置,使得时钟信号从MMCM的输出到外部组件的输入之间几乎没有延迟或偏斜。这通常通过精确匹配时钟信号路径的电气特性来实现,以确保时钟边沿在所有目的地同时到达。

但是,在某些情况下,由于外部组件的输入电容和FPGA的反馈路径电容之间的负载差异,精确的时钟对齐无法实现。例如,外部组件的输入电容可能是1 pF到4 pF,而FPGA的输入电容大约是8 pF。这种差异会导致信号斜率不同,本质上就是偏斜。设计师需要了解这种效应,以确保时序正确。

在实际应用中,使用零延迟缓冲区可以确保FPGA内部和外部组件之间的同步操作,从而优化系统性能。它有助于减少由于时钟偏斜引起的时序问题,特别是在需要高精度时钟同步的系统中。

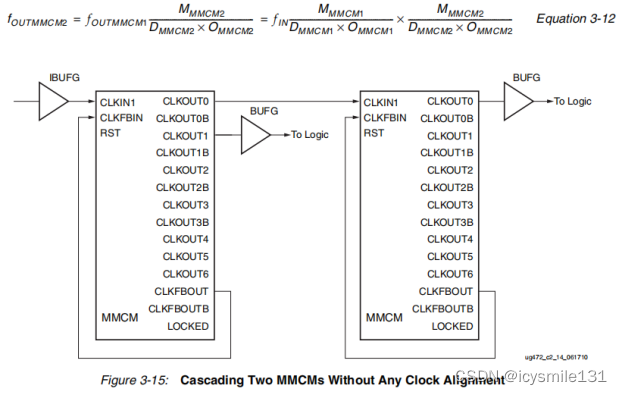

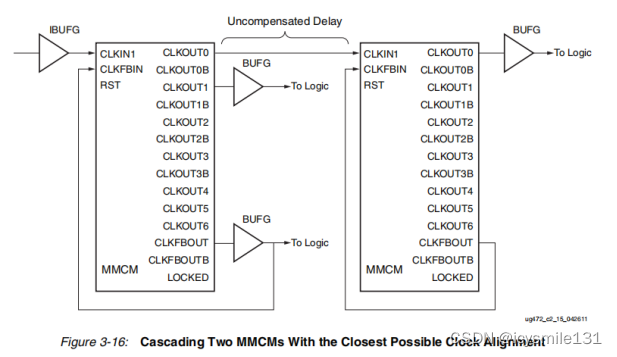

4、CMT到CMT的连接

MMCM和PLL可以通过CMT主干线使用CLKOUT0到CLKOUT3进行级联,从而允许生成更大范围的时钟频率。当使用CMT主干线时,不需要额外的缓冲区(如图3-15和图3-16所示)。由于主干线的延迟未被补偿,因此两个MMCM的输出时钟之间将存在相位偏移。

方程3-12显示了最终输出频率与两个MMCM的输入频率和计数器设置之间的关系。第二个MMCM的输出时钟与输入时钟之间的相位关系是不确定的,因为主干线连接未被补偿,所以在两个MMCM之间会存在一个额外的相位偏移。为了级联MMCM,需要将第一个MMCM的输出路由到第二个MMCM的CLKIN引脚。这条路径提供了最低的设备抖动。使用反相CLKOUTxB输出进行级联是不可用的。

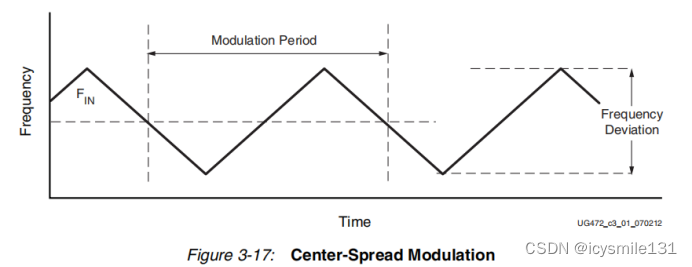

5、扩频时钟生成(Spread-Spectrum Clock Generation)

扩频时钟生成(SSCG)被电子设备制造商广泛使用,以减少这些设备产生的电磁干扰(EMI)的频谱密度。制造商必须确保发出的电磁能量水平不会干扰附近其他电子设备的运行。例如,当电话靠近视频显示器时,电话通话的清晰度不应降低。同样,当使用电话时,显示器也不应受到影响。

SSCG通过将电磁能量分散到较大的频率范围内,有效地降低了在窄频率窗口内测量的电场和磁场强度。通过调制SSCG输出,可以降低任何单一频率的峰值电磁能量。

当将SS_EN设置为TRUE时,MMCME2可以从标准固定频率振荡器生成扩频时钟(如图3-17所示)。在MMCME2内部,VCO频率与CLKFBOUT和CLKOUT[6:4,1,0]一起调制。时钟输出CLKOUT[3:2]用于控制调制周期,并不用于一般用途。只要时钟频率调整缓慢,扩频就不会影响MMCME2的周期抖动。

调整调制周期SS_MOD_PERIOD允许FPGA设计师根据MMCME2的设置选择最接近的调制周期。只要调制频率高于可听频率范围(30 kHz),扩频调制就会减少电磁干扰(EMI)。通常,设计师会选择较低的调制频率,以最大限度地减少引入扩频的影响。

通过SS_MODE(CENTER_HIGH或DOWN_HIGH)增加频率偏差,会增强总体EMI的减少效果,但必须小心确保增加的频率范围不会影响到整个系统的运行。由于扩频时钟和输入时钟以不同的频率运行,因此在时钟域之间传输的任何数据都应使用异步FIFO,以确保数据不会丢失。增加频率偏差将需要更大的FIFO。

另一个设计权衡点在于选择使用中心扩频还是下扩频。选择SS_MODE(DOWN_HIGH,DOWN_LOW)会将频率扩展到较低的频率范围。DOWN_HIGH的频率偏差与CENTER_LOW相似。使用下扩频的决策通常是考虑到扩频对时序分析的影响。

在使用扩频时钟时,设计必须在频率偏差中的最高频率处满足时序要求。因此,如果一个100 MHz的时钟在SS_MODE(CENTER_LOW)下产生3%(±1.5%)的中心扩频,那么这个100 MHz时钟加上3%的中心扩频必须通过时序分析,就像它是一个101.5 MHz的时钟一样。然而,如果SS_MODE(DOWN_HIGH)产生3%的下扩频,则输入频率是频率偏差中的最高频率。因此,对于一个具有3%下扩频的100 MHz时钟,该下扩频时钟在时序分析中仍然被视为100 MHz的时钟。