1 简介

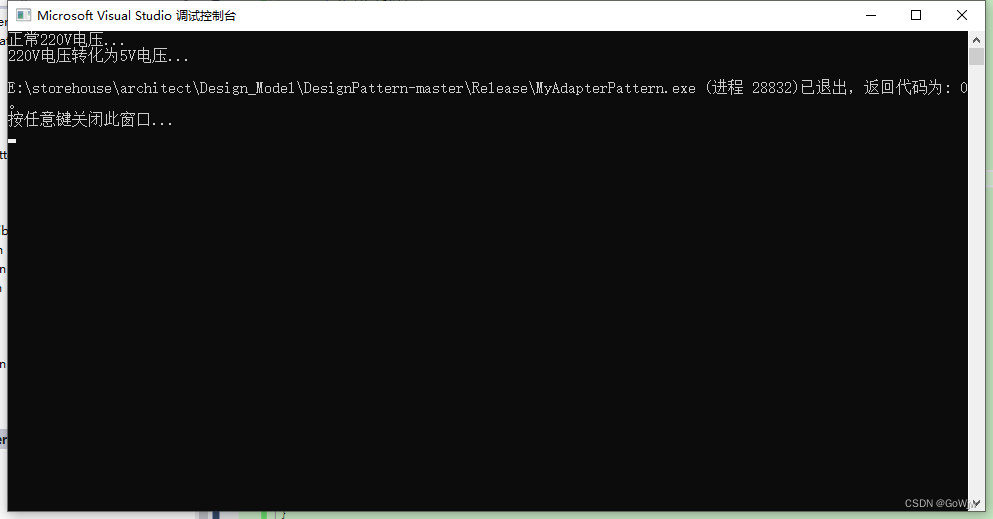

FPGA对于外部的时钟以及数据的延时信息是不知道的,在低速时钟且时钟发射沿在数据正中心的时候,一般可以不做约束来直接使用。但是到了高速时钟或者双沿采样或者发射沿和数据对齐的情况下,这时候就需要告诉VIVADO外部的时钟与数据情况来让VIVADO分析能否满足建立时间与保持时间。INPUT约束仅仅只是告诉VIVADO外部的时钟情况,而内部的布局布线并不会因此改变。

2 INPUT模型

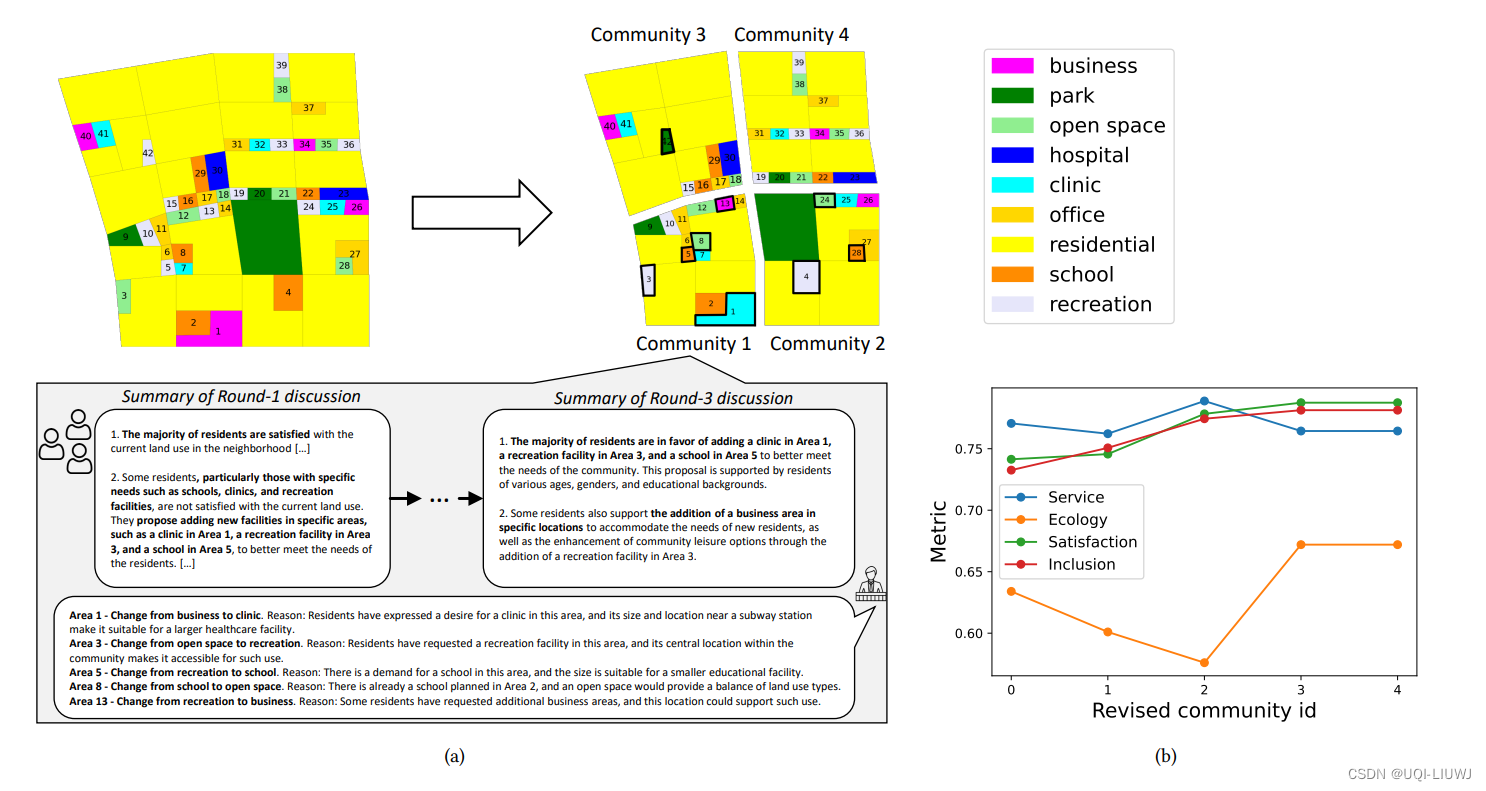

上图两个图是外部时钟的两种模型,一种是源同步模型,源同步模型是指时钟给上游芯片,芯片发出时钟与数据给FPGA,这样的好处是时钟和数据同源,有利于时序分析。另一个是系统同步的FPGA输入模型,时钟分别给上游器件和FPGA,这种不好分析FPGA端口的数据与时钟关系,不利于时序约束。现在电路一般采用源同步模式,所以一般情况下只分析源同步模式。

上游器件一般都是数据采集器件,如AD转换芯片,摄像头芯片。然后通过PCB走线进入到FPGA内部,其中,对于VIVADO来说,FPGA内部的延时是已知的,但是不知道外部数据与时钟的关系,这个时候就需要对外部的时钟以及数据进行约束来告诉FPGA时钟与数据的关系来看是否能正确采集到数据。

外部的时钟与数据的延时一般情况下包含两个部分,一个是芯片在发射数据的时候,时钟与数据之间的时间延时,另一个就是数据与时钟在PCB走线的时候经过的延时,一般情况下,PCB在布线的时候数据和时钟会做等长设计,这里我们就先不考虑PCB延时。

源同步模型如下:

时钟给上游器件,然后上游器件发出时钟与数据经过PCB走线进入FPGA。这里我们主要分析的就是时钟的采样沿与数据到来的时间,这两个参数是需要给到VIVADO的。我们来在前面的基础上继续分析这个模型的数据实际到达时间与数据要求到达时间。

数据实际到达的时间有:

D

a

t

a

a

r

r

i

v

a

l

t

i

m

e

=

T

c

o

+

T

d

_

b

d

+

T

d

_

f

i

(1)

Data \;arrival\;time=T_{co}+T_{d\_bd}+T_{d\_fi}\tag{1}

Dataarrivaltime=Tco+Td_bd+Td_fi(1)

数据要求到达的时间有:

D

a

t

a

R

e

q

u

i

r

e

a

r

r

i

v

a

l

t

i

m

e

=

T

c

y

c

l

e

+

T

c

_

d

+

T

c

_

b

d

+

T

c

_

f

i

−

T

s

u

(2)

Data\;Require\;arrival\;time=T_{cycle}+T_{c\_d}+T_{c\_bd}+T_{c\_fi}-T_{su}\tag{2}

DataRequirearrivaltime=Tcycle+Tc_d+Tc_bd+Tc_fi−Tsu(2)

建立时间裕量有:

S

e

t

u

p

S

l

a

c

k

=

D

a

t

a

R

e

q

u

i

r

e

t

i

m

e

−

D

a

t

a

a

r

r

i

v

a

l

t

i

m

e

=

T

c

y

c

l

e

+

T

c

_

d

+

T

c

_

b

d

+

T

c

_

f

i

−

T

s

u

−

(

T

c

o

+

T

d

_

b

d

+

T

d

_

f

i

)

(3)

Setup \;Slack= Data \;Require\;time-Data \;arrival\;time\\ \,\\\qquad\qquad\qquad=T_{cycle}+T_{c\_d}+T_{c\_bd}+T_{c\_fi}-T_{su}-(T_{co}+T_{d\_bd}+T_{d\_fi})\tag{3}

SetupSlack=DataRequiretime−Dataarrivaltime=Tcycle+Tc_d+Tc_bd+Tc_fi−Tsu−(Tco+Td_bd+Td_fi)(3)

由于数据一般是多bit并行输出的,且输出的时间与时钟并不是固定的延时,所以一般情况下,

T

c

o

T_{co}

Tco与

T

d

_

b

d

T_{d\_bd}

Td_bd存在一个最大最小值,在分析建立时间裕量的时候,从公式中可以看出当数据延时取最大值的时候,建立时间裕量最小。

下面是保持时间分析:

数据实际结束的时间有:

D

a

t

a

f

i

n

i

s

h

t

i

m

e

=

T

c

o

+

T

d

_

b

d

+

T

d

_

f

i

+

T

c

y

c

l

e

(4)

Data \;finish\;time=T_{co}+T_{d\_bd}+T_{d\_fi}+T_{cycle}\tag{4}

Datafinishtime=Tco+Td_bd+Td_fi+Tcycle(4)

数据要求结束的时间有:

D

a

t

a

R

e

q

u

i

r

e

f

i

n

i

s

h

t

i

m

e

=

T

c

y

c

l

e

+

T

c

_

d

+

T

c

_

b

d

+

T

c

_

f

i

+

T

h

(5)

Data\;Require\;finish\;time=T_{cycle}+T_{c\_d}+T_{c\_bd}+T_{c\_fi}+T_{h}\tag{5}

DataRequirefinishtime=Tcycle+Tc_d+Tc_bd+Tc_fi+Th(5)

保持时间裕量有:

H

o

l

d

S

l

a

c

k

=

D

a

t

a

R

e

q

u

i

r

e

f

i

n

i

s

h

t

i

m

e

−

D

a

t

a

f

i

n

i

s

h

t

i

m

e

=

T

c

o

+

T

d

_

b

d

+

T

d

_

f

i

+

T

c

y

c

l

e

−

(

T

c

y

c

l

e

+

T

c

_

d

+

T

c

_

b

d

+

T

c

_

f

i

+

T

h

)

(6)

Hold \;Slack= Data \;Require\;finish\;time-Data \;finish\;time\\ \,\\\qquad\qquad\qquad=T_{co}+T_{d\_bd}+T_{d\_fi}+T_{cycle}-(T_{cycle}+T_{c\_d}+T_{c\_bd}+T_{c\_fi}+T_{h})\tag{6}

HoldSlack=DataRequirefinishtime−Datafinishtime=Tco+Td_bd+Td_fi+Tcycle−(Tcycle+Tc_d+Tc_bd+Tc_fi+Th)(6)

从公式中可以看出当数据延时取最小值的时候,保持时间裕量最小。

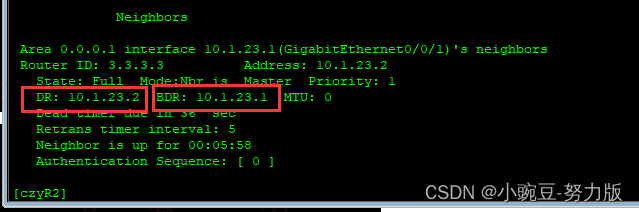

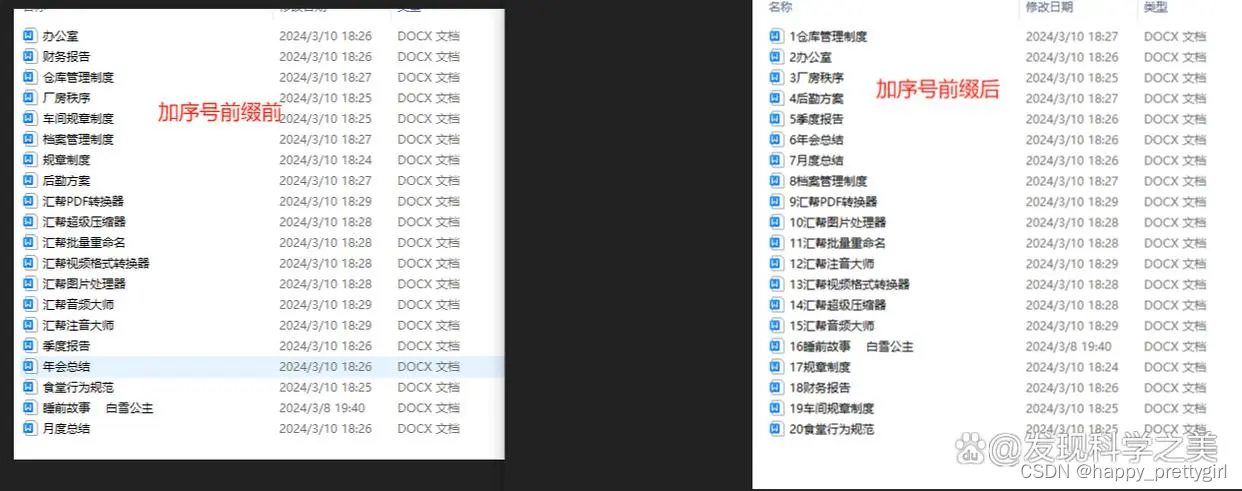

3 INPUT时序约束

上游器件的时钟和数据一般有两种关系,一种是时钟发射沿和数据的起始对齐,另一种是时钟的发射沿与数据的保持时间中心对齐。一般情况下,数据在两个采样沿中心的时候,对于FPGA是时序最好的时候,而时钟的发射沿与数据对齐的时候,时序最容易出现违例的情况,而且建立时间和保持时间都有可能出现违例。

input delay 描述的是发射沿与数据的起始位之间的关系。

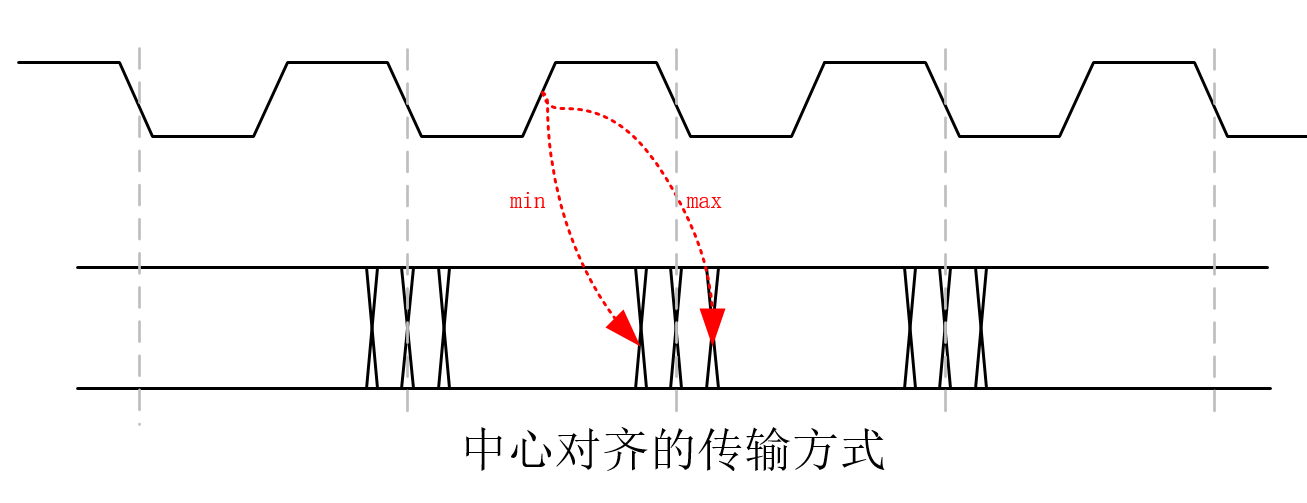

3.1 input delay 中心对齐

当时钟的发射沿与数据的正中心对齐时,这时候的只需要在时序约束中填上数据正中心的发射沿分别距离数据最小以及最大的延时即可,例如一个占空比50%的50MHz时钟,数据采用中心对齐的方式发送,数据的最小以及最大延时均为2ns,那么就要在时序约束的时候约束数据距离时钟的上升沿为8ns和12ns,采样时钟为上升沿。具体的时序约束在最后做,这里先略过。

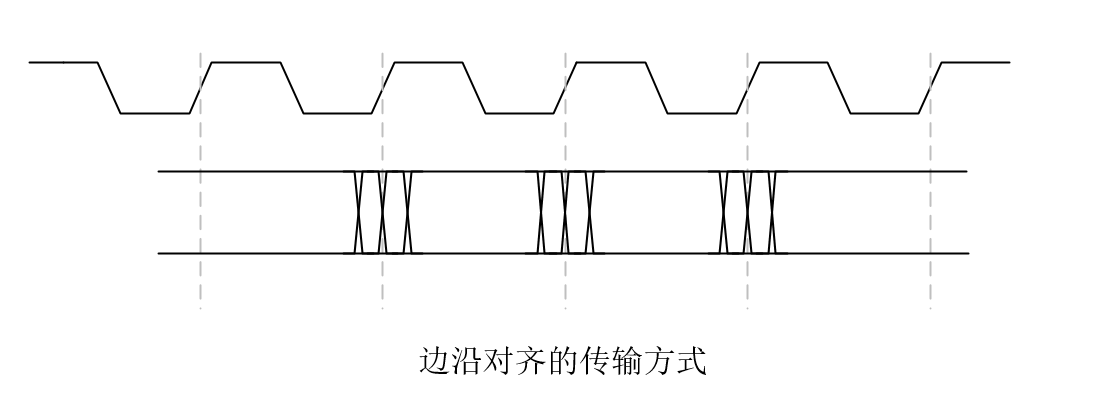

3.2 input delay 边沿对齐

上图是就是边沿对齐的传输方式,这种方式下就会有一个问题,时钟的发射沿相对于数据的延时时多少?

3.2.1 发射时钟与数据起始位对齐

当将发射时钟与数据起始位对齐时,时序较容易出现保持时序违例,此时的约束里面应该填的就是±2ns,此时看时序报告,是非常容易出现违例的。

当发射时钟比数据起始位快一个时钟的时候,此时的时序约束就应该填写18ns和22ns。此时看时序报告,时序报告最有可能出现建立时序违例。为什么会出现这种情况呢,首先需要搞明白当我们把最大最小的延时给到VIVADO后,VIVADO是怎么分析的。

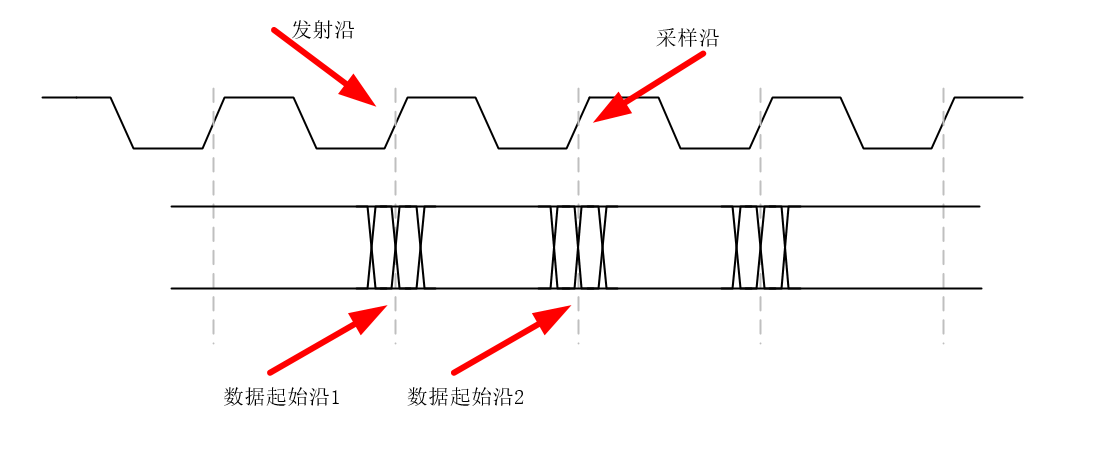

如图所示,当对时钟进行约束时,假设填的参数中最大最小延时的参考是发射沿与数据起始沿1,那么VIVADO就会默认采样沿采集的数据是数据起始沿1到数据起始沿2之间的数据,假如进入FPGA后时钟比数据快,建立时间能满足要求,但是保持时间不能满足;假如数据比时钟快,数据必须比时钟快2ns+保持时间门限以上保持时间才能满足保持时间的要求。

假设填的参数中最大最小延时的参考是发射沿与数据起始沿12,那么VIVADO就会默认采样沿采集的数据是数据起始沿2后的一个数据,假如进入FPGA后时钟比数据快,即时钟左移,建立时间一定不能满足要求,但是保持时间能满足;假如数据比时钟快,即时钟右移,保持时间能满足要求,除非数据快2ns+建立时间门限,不然还是违例状态。

综上所述,在发射沿与数据对齐的时候,一般时序较难满足,会用一些其他方式来调整时序以达到时序收敛。如PLL来调整时钟,或者原语来调整数据。

3.3 PLL调整input delay

加入PLL后,即使不设置相移,时钟都会出现移相,一般情况下是时钟左移,在时序分析中经过PLL时序会有负数。加入在调节PLL左移,也就是负相的话不需要multicycle设置,而正相移动则需要multicycle设置。

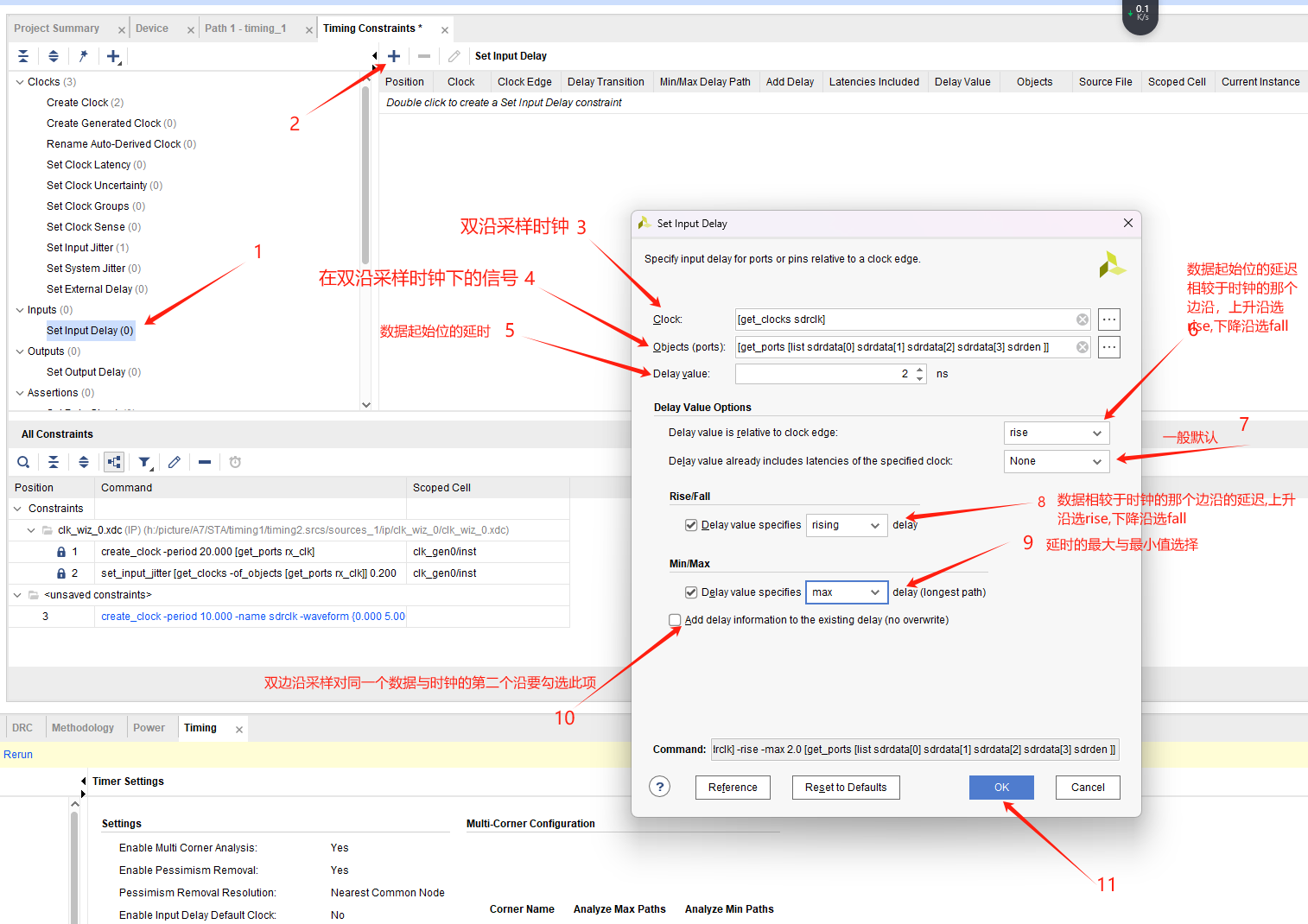

3.4 DDR的input delay

前面都是单沿采样,也就是都是上升沿采样,但是在实际中会有双沿采样的时候,也就是上升沿与下降沿都发射与采集数据。这时候就需要多做一组时序约束,用来约束下降沿的时序。

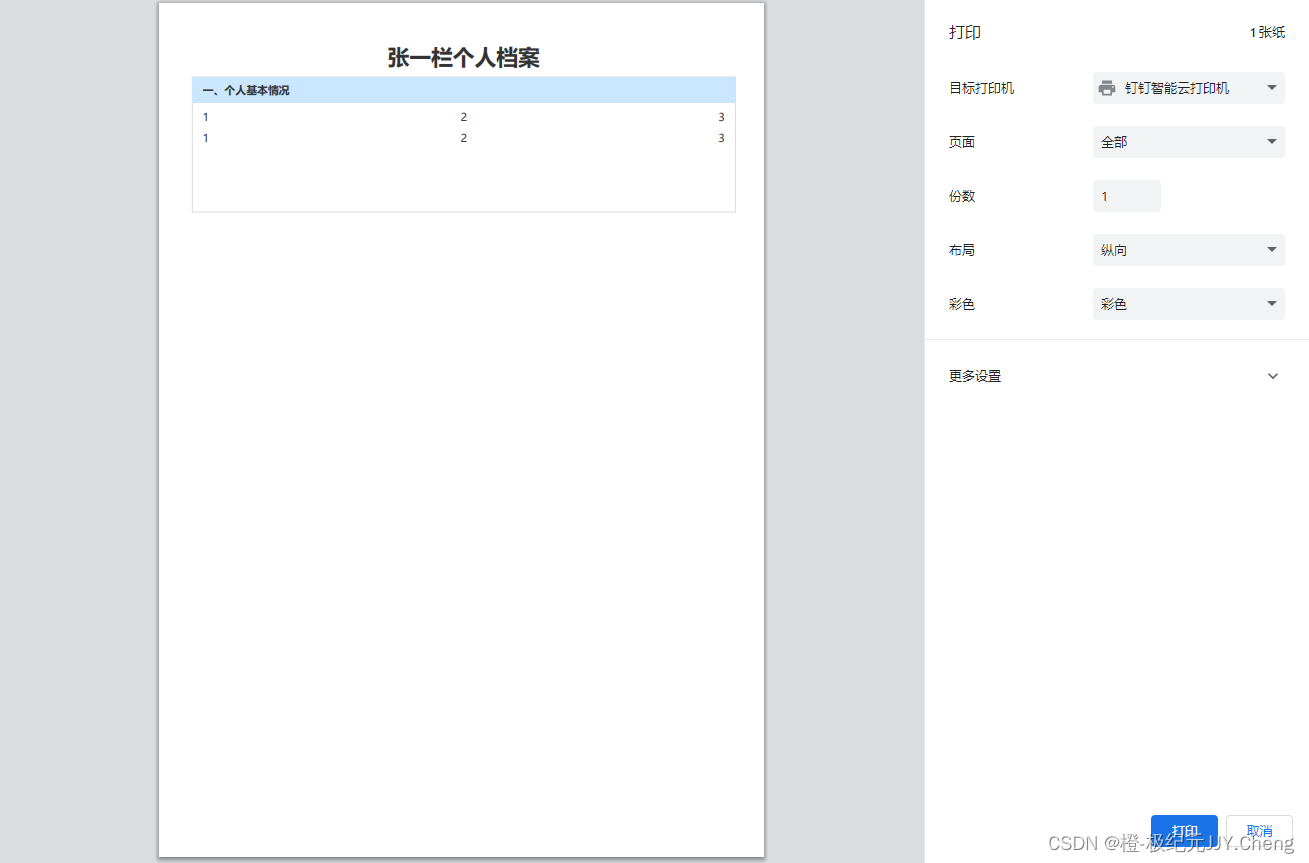

4 VIVADO的input delay约束

![[2021最新]大数据平台CDH存储组件kudu之启用HA高可用(添加多个master)](https://img-blog.csdnimg.cn/2021041515491117.png?x-oss-process=image/watermark,type_ZmFuZ3poZW5naGVpdGk,shadow_10,text_aHR0cHM6Ly9ibG9nLmNzZG4ubmV0L3FxXzQ0NDkxNzA5,size_16,color_FFFFFF,t_70)