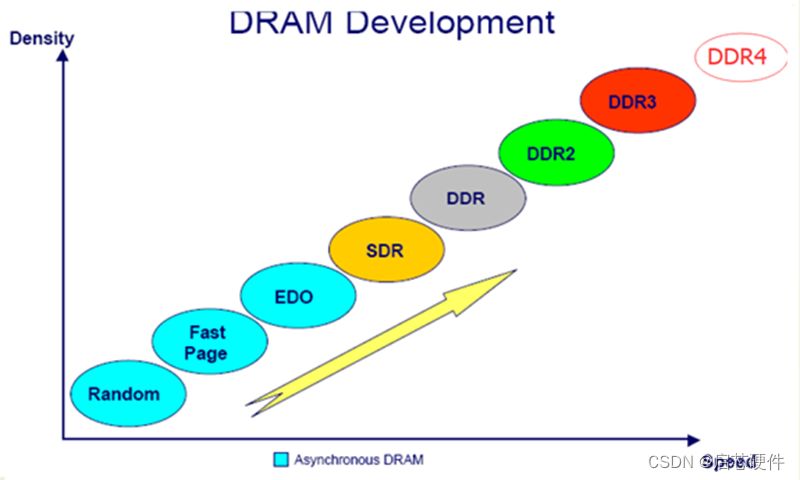

计算机以及手机系统性能的改善,不仅仅取决于cpu处理器主频的提升,还与cpu和内存之间的访问速度密切相关。

SDRAM: Synchronous Dynamic Random Access Memory,同步动态随机存取存储器,同步是指Memory工作需要同步时钟,内部命令的发送与数据的传输都以它为基准;动态是指存储阵列需要不断的刷新来保证数据不丢失;随机是指数据不是线性依次存储,而是由指定地址进行数据读写。通常用来作为电脑的内存使用。

目前主存常用的是基于SDRAM(Synchronous DRAM)芯片技术的内存条,包括DDR SDRAM、DDR2 SDRAM和DDR3 SDRAM,DDR4以及即将推出的DDR5等。

第一板斧–提高工作频率来提速

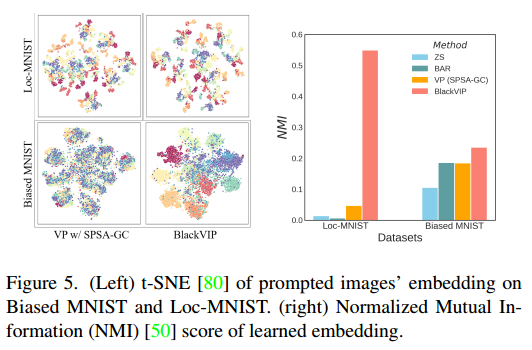

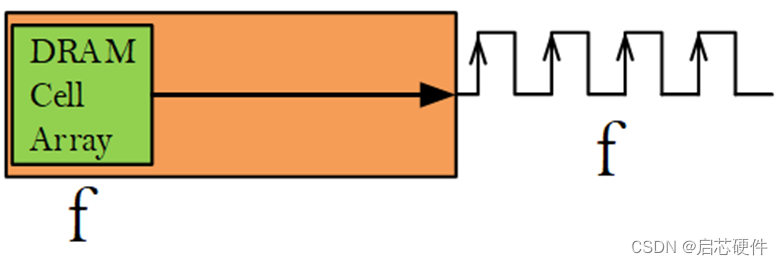

可以说,SDR SDRAM是理解后面所以DDR的基础,包括目前正在研究的DDR5。因此,我们可以从简单到复杂的来详细了解其中的核心技术。首先,看下图:

首先,来看上图。文章中大部分图片都是自己画的,一部分图片是借鉴了其他作者的思路。DRAM Cell Array是存放数据的单元,其作用是不断的与内存总线交换数据资料。每一颗内存芯片都有很多这样的单元。并且这个内存的工作频率是与连接它的总线的数据传输频率是一样的,一个时钟周期只传输一次数据。也就是说,如果其总线的传输速度是50Mb,那么这个内存单元的速度也是50Mb。

再看右边的部分,是说数据是在每个时钟的上升沿才进行传输,因此,内存的传输是同步的。然后,如果想提高SDR的速度,那么就得提高频率了,伴随频率的提高,传输速度同时也提高了。但是,一方面频率的提高必然伴随着能量的消耗,另一方面,每一个时钟周期只能传输1b的数据,效率未免低了一些,因此,第二把板斧应运而生了。

第二板斧—双沿采样技术

第一种方案的问题在于,太多的内存单元要提高频率,代价太大。因此,需要另找突破口,也就是DDR的方案了,DDR的传输数据是SDR的两倍,一个时钟周期传输两次数据,怎么实现的呢?

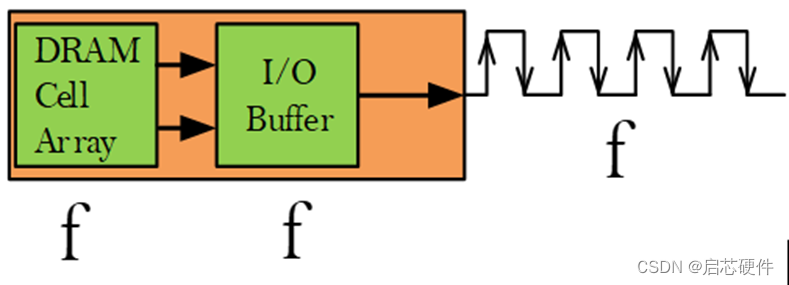

首先,看以下示意图:

对比上图SDR的方案,可以看出多了一个输入输出缓冲器,因为采用了双沿采样技术,也就是不仅在时钟的上升沿传输数据,而且在时钟的下降沿也会传输数据,因此变相的提升了系统的频率,使得整体传输数据也加倍了。

DDR SDRAM在不提高时钟频率的情况下,使得数据传输率提高了一倍,相比与SDR 采用了更多更先进的同步电路,采用了DLL技术提供数据选通信号对数据进行精确定位,由于采用了输入输出缓冲器,对两个内存单元使用相同的列地址线,这样可以同时访问,将数据从两个数据总线中传输,如此,整体系统的数据量就加倍了。虽然,相比于SDR速度得到了极大的提升,功耗也下降了,但是,并不是没有发展的空间,且看第三板斧。

第三板斧—buffer频率倍增技术

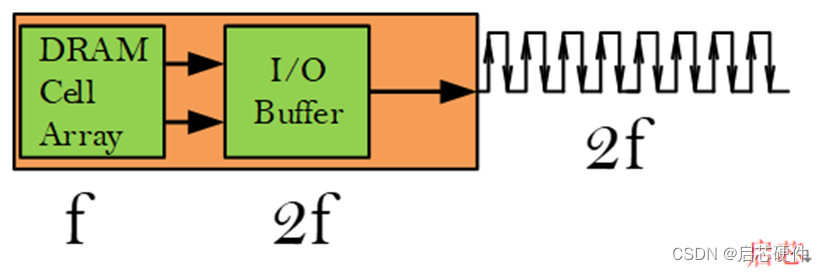

技术再次提升集中体现在DDR2上。一句话总结就是虽然同样采用了在时钟的上升沿和下降沿传输数据的基本方法,但是DDR2拥有两倍于DDR1的内存预读取能力,也就是4 bit的数据预读取。技术原理如下图所示。

主要就是把缓冲器和总线的工作频率提高了一倍。频率提高一倍,带宽也就对应增加了,同时内存基本单元的频率并没有改变。由于DDR2的预读取能力相对预DDR1加倍了,换句话说,DDR2内存每个时钟能够以4倍外部总线的速度读/写数据,并且能够以内部控制总线4倍的速度运行。举个例子,在同样100MHz的工作频率下,DDR的实际频率为200MHz,而DDR2则可以达到400MHz。

DDR3可以简单看作是DDR2的改进版,通过改进缓冲器,让其频率提升了四倍,也就是带宽增加倍四倍,同时内存单元的频率也就是核心频率还是没有变化的。通过双沿采样,相对于DDR2,其预读取能力加倍了,也就是DDR3内存每个时钟周期能够以8倍外部总线的速度读写数据,每个时钟周期能够预读取8 bit的数据。在同样100MHz的工作频率下,DDR的实际频率是200 MHz,而DDR3则达到了800 MHz。

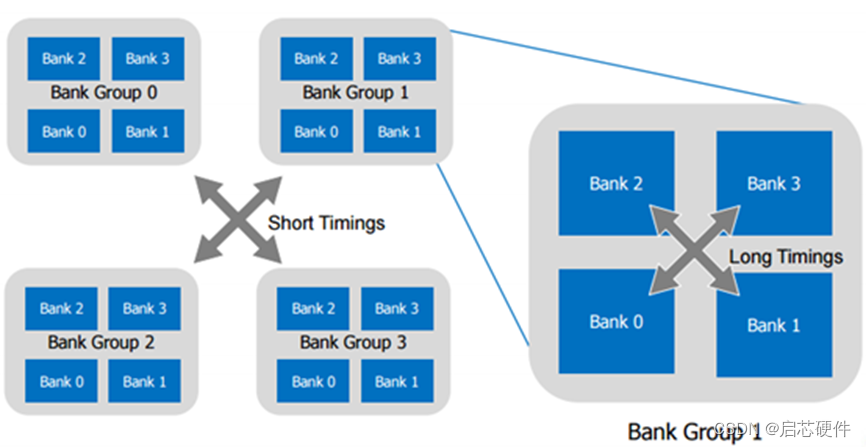

第四板斧—Bank Group点传技术

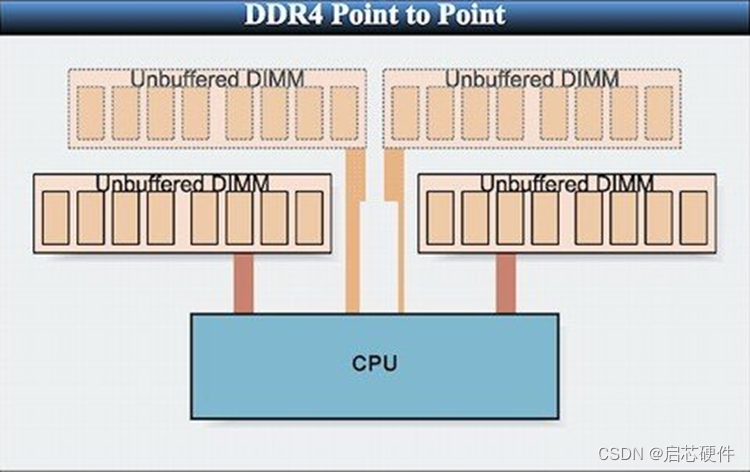

我并没有把DDR4归类到上面,因为在技术层面,DDR4并不简简单单是DDR3的改进版。诚然,DDR4最重要的使命依然是提高内存的频率和带宽,回头看DDR—DDR2—DDR3的整个发展历程,我们不难看出一直都是以提高数据的预存取为主要的性能提升手段。但是,到了DDR4,数据的预取已经变得非常困难,同时,带来的延时也非常大,因此,DDR的架构专家另辟蹊径,推出了Bank Group的设计。

相对于数据预取带来速度内存频率的提升, Bank Group的架构设计更为精巧。简要说一下,DDR4的中每个Bank Group可以独立读写数据,这样做的好处是让内部的数据吞吐量得到了大幅的提升,内存的等效频率得到了巨大的提升,可以同时读取大量的数据。虽然,DDR4在架构上依然采用了与DDR3相同的8 bit预取,但是由于使用了BANK GROUP分组,可能是两个或者四个BANK GROUP的分组,由于DDR4允许每个BANK GROUP分组都可以独立的激活、读写和刷新操作,因此改进了内存整体效率与带宽。举个例子,如果内存内部设计了两个独立的BANK GROUP,那么相当于每次可以操作16 bit的数据,也就是内存的预取值就是16 bit;同理,如果是有四个独立的BANK GROUP,那么相当于每次可以操作32 bit的数据。