I. 引言

A. 研究背景与意义

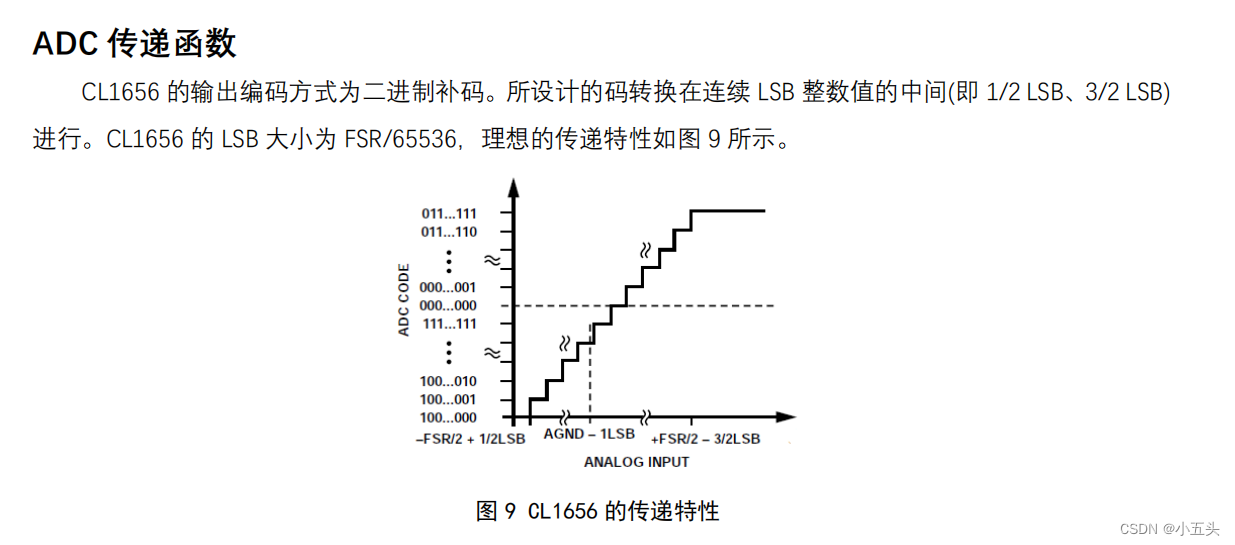

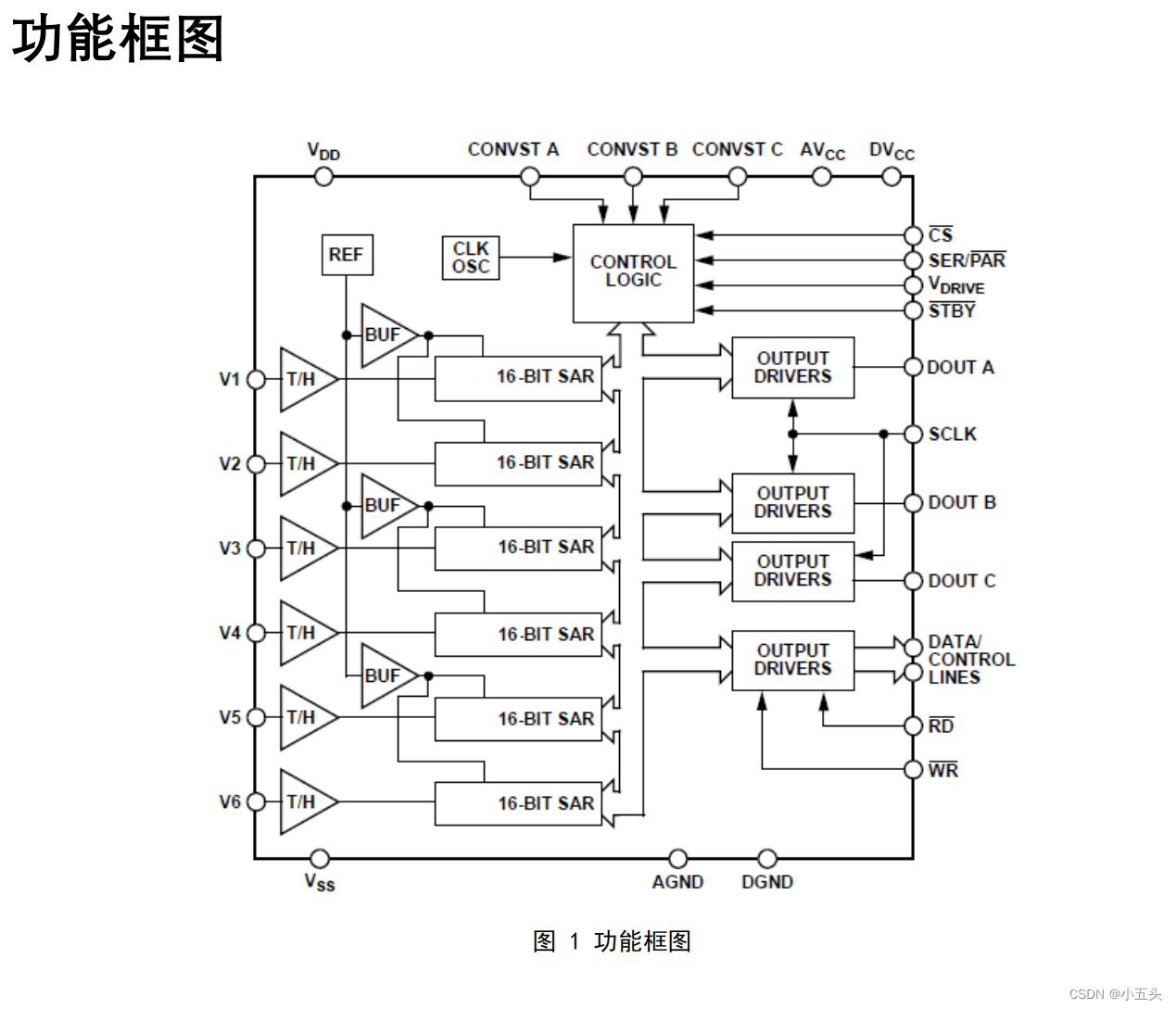

CL1656是一款精度高、功耗低、成本低的5V单片低功耗运放,由核心互联公司研发制造,CL1656 是一个 16-bit、快速、低功耗逐次逼近型 ADC,吞吐速率高达 250 kSPS,并且内置低噪声、宽 带宽采样保持放大器。转换过程与数据采集利用 CONVST 信号和内部振荡器进行控制,为设计人员提供了极大的灵活性和空间。 CL1656支持多种输入模式和输出模式,包括单端、差分、反馈、共地以及双极输出,并且能够利用多种工作模式来满足不同的应用要求。此外, CL1656还具有较低的温度系数,能够适应不同的电源电压。在低电源电压下, CL1656可以达到很高的精度;在高电源电压下, CL1656仍然能够保持相对较高的精度。

B. 应用领域

CL1656可以用于各种不同的应用场合,主要包括:

(1)信号采集,如摄像头、A/D转换器等。

(2)数据通讯,如数字音频、数据通信接口等。

(3)信号处理,如模数转换器、 FPGA等。

(4)数字测量,如数字信号处理器、传感器接口等。

(5)计算机接口,如 USB、以太网等。

(6)车载电子,如车载信息系统、自动驾驶系统等。

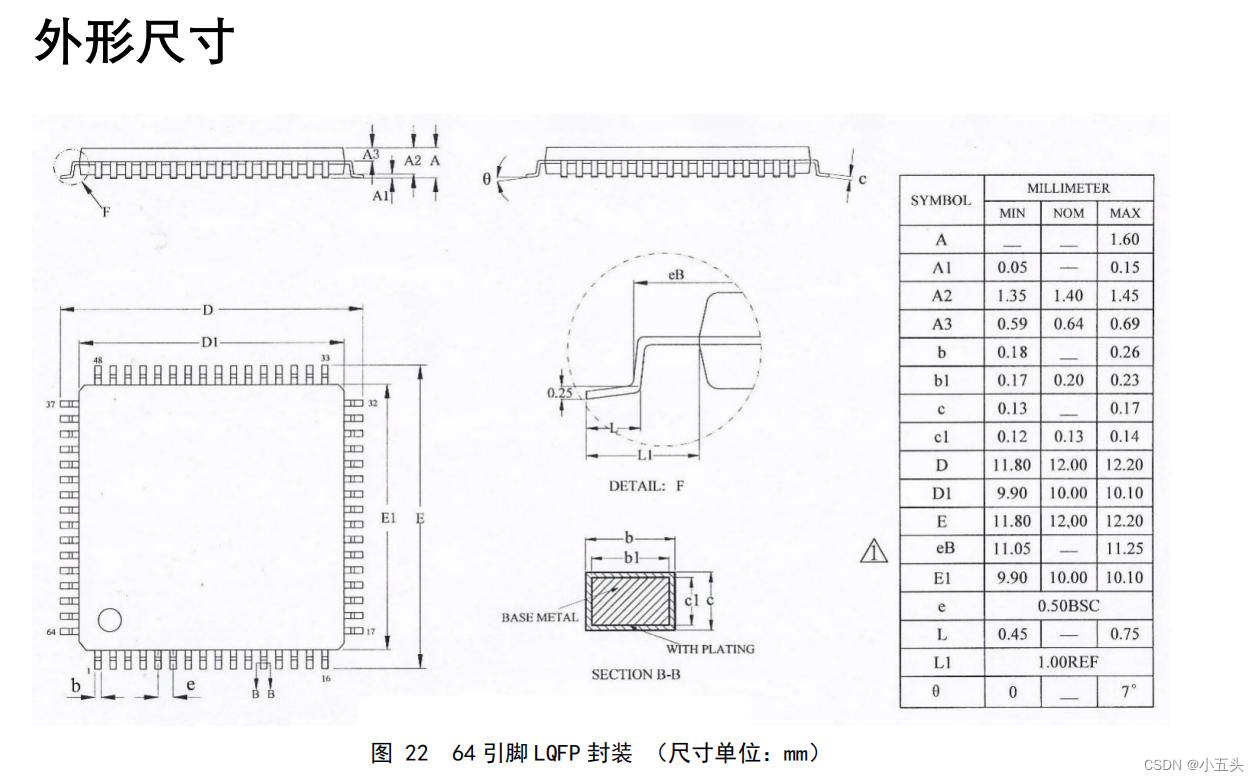

II. 芯片封装介绍

随着电子技术的飞速发展, IC封装也得到了长足的进步。目前 IC封装主要有: COB、 SOP、 QFN等。其中,引脚数在8个以上的有四种封装: COB封装、 SOP封装、 QFN封装和 LQFP封装。随着各种高密度元器件的发展, LQFP成为最受欢迎的一种小型无引脚 IC封装,其特点是芯片面积小,引脚少,且价格低廉,在国内广泛使用。LQFP (Low Proportional Flop Package)又称为低密度多芯片表面贴装,是一种新型的表面贴装技术。它将一个多芯片元件或一个芯片组直接安装在一个 PCB板上。

LQFP主要用在手机的电路板上,其特点是引脚少,面积小,成本低,但引脚的高度比 SOP低。其引脚数目少,一般为128~256个。在 LQFP中,引脚数目最多的是64引脚的封装。在使用时,其引脚数目也会有所不同。有的产品中只有2~4个引脚;有的产品则有8个以上的引脚数。如:飞利浦 LQFP封装中最多的是64引脚封装(2~4个引脚);而索尼 LQFP封装中最多的则是16个引脚(1~4个引脚);三星 LQFP封装中最多的则是32个引脚(2~4个引脚)。

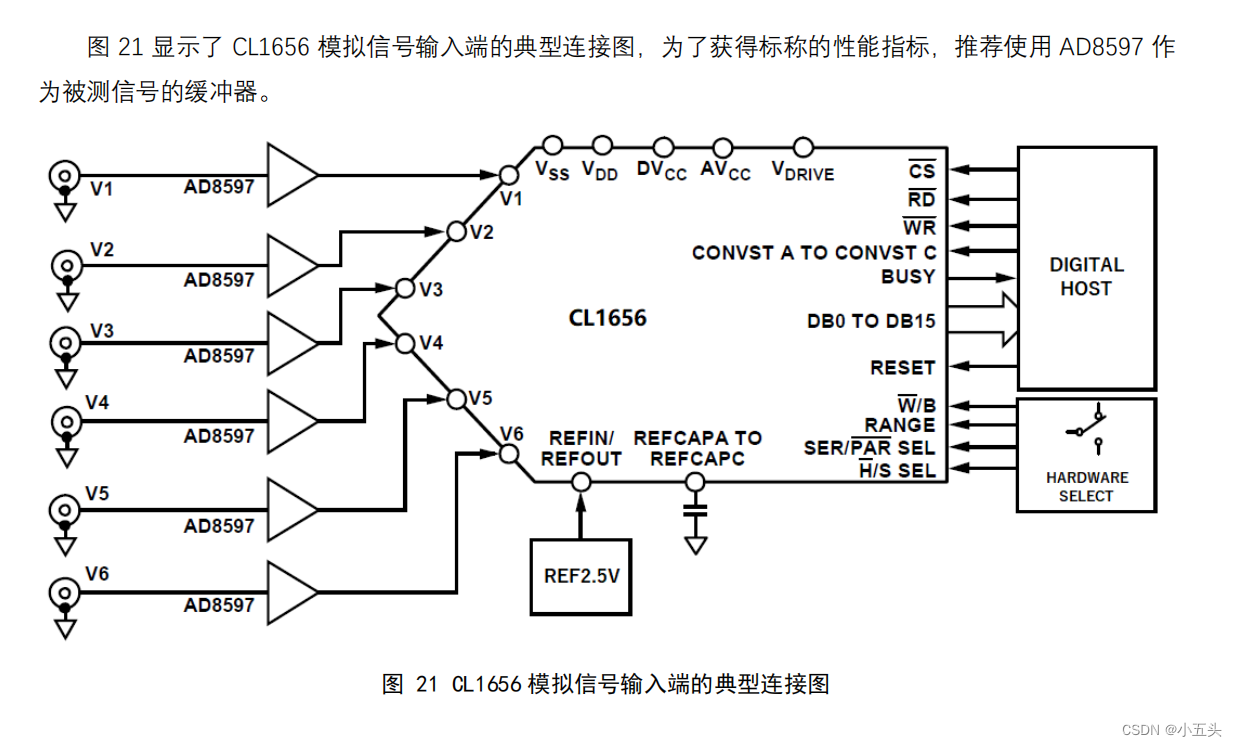

CL1656是一款模拟信号输入端的数字开关,在工业控制中被广泛的应用于各种场合,包括现场设备的控制、各种设备的状态监测、电力的控制、设备的安全保护等。

CL1656是一款基于三端集成模拟开关,并集成了高速 AD转换器和高速开关量输出功能的器件。

三端集成模拟开关CL1656,一般由一个输入端、两个输出端和一个电源端组成。CL1656有两种典型输出形式:标准、逻辑输出,常用在测量设备中,模拟量输出信号一般接在CL1656的输入端。

现场模拟量信号输入,一般是指现场的温度、压力、流量、液位等物理量信号的输入。这些物理量信号通常需要经过传感器将其转化为数字信号,然后再经过现场模拟开关将信号转换为数字,最后通过计算机进行处理。CL1656集成了一个模拟量输入端,通过它可以将这些信号转换为数字信号,并通过计算机进行处理。这种方式的优点是可以方便的将不同的模拟量进行隔离,不会对其他设备产生影响。缺点是转换的效率相对较低,通常需要通过比较大的电流进行传输,而在某些现场环境下这种电流会很大,这样就会导致信号的传输距离变短,甚至会产生干扰。

传感器信号采集是指对传感器输出的模拟信号进行采集,并通过与之相连的变送器输出给控制器进行处理。由于传感器的种类繁多,需要根据实际情况选择相应的传感器,并通过相应的变送器来将传感器的信号转化为易于处理的信号,进而将其传送给控制器。在工业生产中,传感器大多采用模拟量输入,所以需要将其接入CL1656的输入端,再将CL1656输出端接到变送器上。

CL1656可对电压、电流进行模拟量的采样,并将采样后的模拟量通过 AD转换器转化成数字量输出。需要注意的是,由于 AD转换器采用了同步采样技术,因此采样后的模拟量在转换过程中会存在误差,但是这个误差对于不同的应用场景来说都是可以忽略不计的。

III.芯片io介绍

| Interface | Pin Number | Pin Type | Pin Name | 描述 | Net Name | Active | 配置 |

| 模拟输入 | 33 | AI | V1 | 模拟输入 1 至 6。这些是单端模拟输入。在硬件模式下,这些通道上的模拟输入范围由 RANGE 引脚决定。在软件模式下,由控制寄存器的 Bit RNGC 至 Bit RNGA 决定。 | V1 | ||

| 36 | AI | V2 | V2 | ||||

| 39 | AI | V3 | V3 | ||||

| 42 | AI | V4 | V4 | ||||

| 45 | AI | V5 | V5 | ||||

| 48 | AI | V6 | V6 | ||||

| 基准电压 | 51 | REF | REFIN/REFOUT | 基准电压输入/输出。此引脚提供片上基准电压,供 ADC 外部使用。 或者,可禁用内部基准电压源,并将外部基准电压源施加到此输入端。参见“基准电压源”部分。使能内部基准电压源时,应利用至少一个 10uF 去耦电容对此引脚去耦。 | 2V5_REFIN | 使用内部基准。 硬件模式下使能内部基准电压源,则应设置H/S SEL 引脚 = 0 且 REFEN/DIS引脚 = 1。 软件模式下使能内部基准电压源,则应设置H/S SEL = 1 并需要写入控制寄存器,以将该寄存器的 DB9 置于 1。 | |

| 模拟输入通道 硬件选择 | 23 | DI | CONVST A | 转换开始输入 A、 B 和 C。这些逻辑输入用来启动 ADC 对转换。 CONVST A 用来启动 V1 和 V2 同步转换。 CONVST B 用来启动 V3 和 V4 同步转换。 CONVST C 用来启动 V5 和 V6 同步转换。 当 CONVSTx 引脚从低电平变为高电平时,所选 ADC 对的取样保持开关从采样切换到保持,然后便启动转换。利用这些输入端,还可让 ADC 对进入部分掉电省电模式。 | CONVST A | 4.7K VCC_5V。通道1、2启动 | |

| 22 | DI | CONVST B | CONVST B | 4.7K VCC_5V。通道3、4启动 | |||

| 21 | DI | CONVST C | CONVST C | 4.7K VCC_5V。通道5、6启动 | |||

| 去耦电容接地 | 54 | REF | REFCAPA | 去耦电容连接到这些引脚。这会对每对 ADC 的基准电压缓冲器进行去耦。每个 REFCAP 引脚应通过 10uF 和 100 nF 电容去耦至 AGND。 | REFCAPA | 去耦电容接地 | |

| 56 | REF | REFCAPB | REFCAPB | 去耦电容接地 | |||

| 58 | REF | REFCAPC | REFCAPC | 去耦电容接地 | |||

| FPGA | 29 | DI | /W/B | 字 //字节输入。当此引脚处于逻辑低电平时, 可利用并行数据线 DB[15:0]来传输 ADC 的输入输出数据。当此引脚处于逻辑高电平时,使能字节模式。在此模式下,利用数据线 DB[15:8]来传输数据, DB[7]用作 HBEN。要获得 16-bit 转换结果,需进行双字节读取。在串行模式下,此引脚应与 DGND 相连。 | WB | 字模式,并行数据线DB[15:0]传输数据。 DOWN | |

| 27 | DI | RANGE | 模拟输入范围选择。逻辑输入。此引脚的逻辑电平决定模拟输入通道的输入范围。 当此引脚在 BUSY 下降沿为逻辑 1 时,下一次转换的范围为±2 × VREF。当此引脚在 BUSY 下降沿为逻辑 0 时, 下一次转换的范围为±4 × VREF。 在硬件选择模式下,在 BUSY 下降沿检查 RANGE 引脚。在软件模式(H/S SEL = 1)下,可将 RANGE 引脚和 DGND 相连,然后由控制寄存器内的RNGA、 RNGB 和 RNGC bits 决定输入范围。 | RANGE | 模拟输入转换的范围为±2 × VREF。 UP | ||

| 61 | DI | SER//PAR/SEL | 串行/并行/选择输入。当此引脚处于低电平时,选择并行接口。当此引脚处于高电平时, 选择串行接口模式。在串行模式下,DB[10:8]用作 DOUT[C:A], DB[0:2]用作 DOUT 选择且 DB7 用作 DCEN。在串行模式下, DB15 和 DB[13:11]应与 DGND 相连。 | SEL | 并行模式。 DOWN | ||

| 62 | DI | /H/S SEL | 硬件 /软件选择输入。逻辑输入。当H/S SEL = 0 时, ADC 在硬件选择模式下工作,并通过 CONVST 引脚来选择需同步采样的 ADC 对。当H/S SEL = 1 时,通过写入控制寄存器操作来选择需同步采样的 ADC 对。在串行模式下, CONVST A 用来启动对所选 ADC 对的转换。 | HS_SEL | 硬件模式 选择输入。 DOWN | ||

| 24 | DI | /STBY | 待机模式输入。此引脚用来让 ADC 进入待机模式。/STBY引脚处于高电平时表示正常操作,处于低电平时表示待机操作。 | STBY | 正常工作。 UP | ||

| 19 | DI | /CS | 片选。 此低电平有效逻辑输入使能数据帧传输。在并行模式下,如果CS和RD均处于逻辑低电平,则会使能输出总线,使转换结果输出在并行数据总线上。在并行模式下,如果CS和WR均处于逻辑低电平,则利用 DB[15:8]将数据写入片上控制寄存器。在串行模式下,利用CS使能串行数据帧传输,并逐个输出串行输出数据的最高有效位(MSB)。 | CS | LOW | DOWN | |

| 20 | DI | /RD | 读取数据。在并行模式下,如果CS和RD均处于逻辑低电平,则会使能输出总线。在串行模式下, RD线路应保持低电平。 | RD | DOWN | ||

| 63 | DI | /WR/REF | 写入数据/使能和禁用基准电压源。当H/S SEL 引脚处于高电平,且CS和均𝑊WR处于逻辑低电平时,利用 DB[15:8]将数据写入内部控制寄存器。当H/S SEL 引脚处于低电平时,此引脚用来使能或禁用内部基准电压源。当H/S SEL = 0 且 REFEN/DIS= 0时,禁用内部基准电压源,应将外部基准电压源施加到REFIN/REFOUT 引脚。当H/S SEL = 0 且 REFEN/DIS= 1 时, 使能内部基准电压源,且应该对 REFIN/REFOUT 引脚进行去耦。参见“基准电压源”部分。 | WR | 使能 内部基准电压源。 UP | ||

| 18 | DO | BUSY | BUSY 输出。开始转换时,此引脚变为高电平,并保持高电平直到转换完成,并且转换数据被锁存到输出数据寄存器。当BUSY 信号为高电平时,不应在 ADC 上启动新的转换。 | BUSY | 开始转换时,由低变高; 完成转换后,由高变低。 | ||

| 17 | DO/DI | DB0/SEL A | 数据 Bit 0/选择 DOUT A。当 SER/PAR = 0 时,此引脚充当三态并行数字输出引脚。当 SER/PAR = 1 时,此引脚用作 SELA,并用来配置串行接口。如果此引脚为 1,则串行接口使用1/2/3 个 DOUT 输出引脚工作,并使能 DOUT A 作为串行输出端。在串行模式下,此引脚应始终等于 1。 | DB0 | |||

| 16 | DO/DI | DB1/SEL B | 数据 Bit 1/选择 DOUT B。当SER/PAR = 0 时,此引脚充当三态并行数字输出引脚。当SER/PAR = 1 时,此引脚用作 SELB,并用来配置串行接口。如果此引脚为 1,则串行接口使用2/3 个 DOUT 输出引脚工作,并使能 DOUT B 作为串行输出端。如果此引脚为 0,则不使能 DOUT B 作为串行数据输出端引脚,而仅使用一个 DOUT 输出引脚 DOUT A。不用的串行DOUT 引脚应保持不连接。 | DB1 | |||

| 15 | DO/DI | DB2/SEL C | 数据 Bit 2/选择 DOUT C。当 SER/PAR= 0 时,此引脚充当三态并行数字输出引脚。当SER/PAR = 1 时,此引脚用作 SELC,并用来配置串行接口。如果此引脚为 1,则串行接口使用3 个 DOUT 输出引脚工作,并使能 DOUT C 作为串行输出端。如果此引脚为 0,则不使能 DOUT C 作为串行数据输出引脚。不用的串行 DOUT 引脚应保持不连接。 | DB2 | |||

| 14 | DO/DI | DB3/DCIN C | 数据 Bit 3/菊花链输入 C。当 SER/PAR= 0 时,此引脚充当三态并行数字输出引脚。当 SER/PAR= 1 且 DCEN = 1 时,此引脚充当菊花链输入 C。处于串行模式而非 DGND 菊花链模式下时,应将此引脚连接至 DGND。 | DB3 | |||

| 13 | DO/DI | DB4/DCIN B | 数据 Bit 4/菊花链输入 B。当 SER/PAR= 0 时,此引脚充当三态并行数字输出引脚。当SER/PAR = 1 且 DCEN = 1 时,此引脚充当菊花链输入 B。处于串行模式而非 GND 菊花链模式下时,应将此引脚连接至 DGND。 | DB4 | |||

| 12 | DO/DI | DB5/DCIN A | 数据 Bit 5/菊花链输入 A。当 SER/PAR处于低电平时,此引脚充当三态并行数字输出引脚。当 SER/PAR= 1 且 DCEN = 1时,此引脚充当菊花链输入 A。处于串行模式而非 DGND 菊花链模式下时,应将此引脚连接至 DGND。 | DB5 | |||

| 11 | DO/DI | DB6/SCLK | 数据 Bit 6/串行时钟。当SER/PAR= 0 时,此引脚充当三态并行数字输出引脚。当SER/PAR = 1 时,此引脚用作 SCLK 输入,并成为串行传输的读取串行时钟。 | DB6 | |||

| 10 | DO/DI | DB7/HBEN/DCEN | 数据 Bit 7/高字节启用/菊花链启用。在并行字模式(SER/PAR= 0 且𝑊/B = 0),此引脚用作数据 Bit 7。在并行字节模式(SER/PAR = 0 且𝑊/B = 1),此引脚用作 HBEN。在此模式下且HBEN 引脚处于逻辑高电平时,则先在 DB[15:8]上输出 MSB 字节数据。当 HBEN 引脚处于逻辑低电平时,则先在 DB[15:8]上输出 LSB 字节数据。在串行模式(SER/PAR = 1)下,此引脚用作 DCEN。当 DCEN 引脚处于逻辑高电平时,则器件采用菊花链模式工作,同时 DB[5:3]用作 DCIN[A:C]。处于串行模式而非DGND 菊花链模式下时,应将此引脚连接至 DGND。 | DB7 | |||

| 7 | DO/DI | DB8/DOUT A | 数据 Bit 8/串行数据输出 A。当 SER/PAR= 0 时,此引脚充当三态并行数字输出引脚。当SER/PAR = 1 且 SEL A = 1 时,此引脚用作 DOUT A,并输出串行转换数据。 | DB8 | |||

| 6 | DO/DI | DB9/DOUT B | 数据 Bit 9/串行数据输出 B。当 SER/PAR = 0 时,此引脚充当三态并行数字输出引脚。当SER/PAR = 1 且 SEL B = 1 时,此引脚用作 DOUT B,并输出串行转换数据。在此配置下,串行接口具有两路 DOUT 输出线。 | DB9 | |||

| 5 | DO/DI | DB10/DOUT C | 数据 Bit 10/串行数据输出 C。当SER/PAR= 0 时,此引脚充当三态并行数字输出引脚。当 SER/PAR= 1 且 SEL C = 1 时,此引脚用作 DOUT C,并输出串行转换数据。在此配置下,串行接口具有三路 DOUT 输出线。 | DB10 | |||

| 4 | DO/DI | DB11 | 数据 Bit 11/数字地。当 SER/PAR= 0 时,此引脚充当三态并行数字输出引脚。当SER/PAR= 1 时, 此引脚应与 DGND 相连。 | DB11 | |||

| 3 | DO/DI | DB12 | 数据 Bit 12、数据 Bit 13、数据 Bit 15。当 SER/PAR= 0 时,这些引脚充当三态并行数字输入/输出引脚。当CS和WR处于低电平状态时,这些引脚用来输出转换结果。当CS和WR均处于低电平时, 这些引脚用来写入控制寄存器。当SER/PAR= 1 时,这些引脚应与 DGND 相连。 | DB12 | |||

| 2 | DO/DI | DB13 | DB13 | ||||

| 64 | DO/DI | DB15 | DB15 | ||||

| 1 | DO/DI | DB14/REFBUF | 数据 Bit 14/REFBUF使能/禁用。当 SER/PAR= 0 时,此引脚充当三态数字输入/输出引脚。当 SER/PAR= 1 时,此引脚可用来使能或禁用内部基准电压缓冲器。 | DB14 | |||

| 28 | DI | RESET | 复位输入。当设为逻辑高电平时,此引脚可复位 ADC。当前转换(如有)中止。内部寄存器设为全 0。在硬件模式下,根据硬件选择引脚上的逻辑电平来配置 ADC。在两种模式下,器件应该在上电后收到一个 RESET 高脉冲。复位高电平脉冲宽度典型值为 100 ns。在 RESET 脉冲之后, ADC 需由有效的 CONVST脉冲启动转换; CONVST 脉冲应包括一个高至低的 CONVST下降沿,随后是一个低至高的 CONVST 上升沿。 CONVST 信号应在 RESET 脉冲期间保持高电平。 | REST | HIGH | 复位时, UP | |

| POWER | 9 | P | VDRIVE | 逻辑电源输入。此引脚的电源电压决定逻辑接口的工作电压。此引脚的标称电源与主机接口电源相同。应将此引脚去耦至DGND,并且 10uF 和 100 nF 去耦电容应接在 VDRIVE 引脚上。 | VCC_3V3 | ||

| 26 | P | DVCC | 数字电源 4.75 V 至 5.25 V。 DVCC 和 AVCC 电压在理想情况下应保持等电位,并且电位差(甚至在瞬态电压存在情况时)不得超过 0.3 V。应将此电源去耦至 DGND,并且 10uF 和 100 nF去耦电容应接在 DVCC 引脚上。 | DVCC_5V | |||

| 31 | P | VDD | 正电源电压。这是模拟输入部分的正电源电压,并且 10uF 和100 nF 去耦电容应接在 VDD引脚上。 | VDD_5V | |||

| 30 | P | VSS | 负电源电压。这是模拟输入部分的负电源电压,并且 10uF 和100 nF 去耦电容应接在 VSS引脚上。 | VSS_N5V | |||

| 46 | P | AVCC | 模拟电源电压, 4.75 V 至 5.25 V。这是 ADC 内核的电源电压。AVCC 和 DVCC 电压在理想情况下应保持等电位,并且电位差(甚至在瞬态电压存在情况下)不得超过 0.3 V。应将这些电源引脚去耦至 AGND,并且 10uF 和 100 nF 去耦电容应接在 AVCC引脚上。 | AVCC_5V | |||

| 34 | P | AVCC | AVCC_5V | ||||

| 47 | P | AVCC | AVCC_5V | ||||

| 60 | P | AVCC | AVCC_5V | ||||

| 50 | P | AVCC | AVCC_5V | ||||

| 35 | P | AVCC | AVCC_5V | ||||

| 40 | P | AVCC | AVCC_5V | ||||

| 41 | P | AVCC | AVCC_5V | ||||

| 25 | P | DGND | 数字地 | GND | |||

| 8 | P | DGND | GND | ||||

| 59 | P | AGND | 模拟地 | AD_AGND | |||

| 38 | P | AGND | AD_AGND | ||||

| 43 | P | AGND | AD_AGND | ||||

| 37 | P | AGND | AD_AGND | ||||

| 49 | P | AGND | AD_AGND | ||||

| 57 | P | AGND | AD_AGND | ||||

| 53 | P | AGND | AD_AGND | ||||

| 52 | P | AGND | AD_AGND | ||||

| 32 | P | AGND | AD_AGND | ||||

| 55 | P | AGND | AD_AGND | ||||

| 44 | P | AGND | AD_AGND |

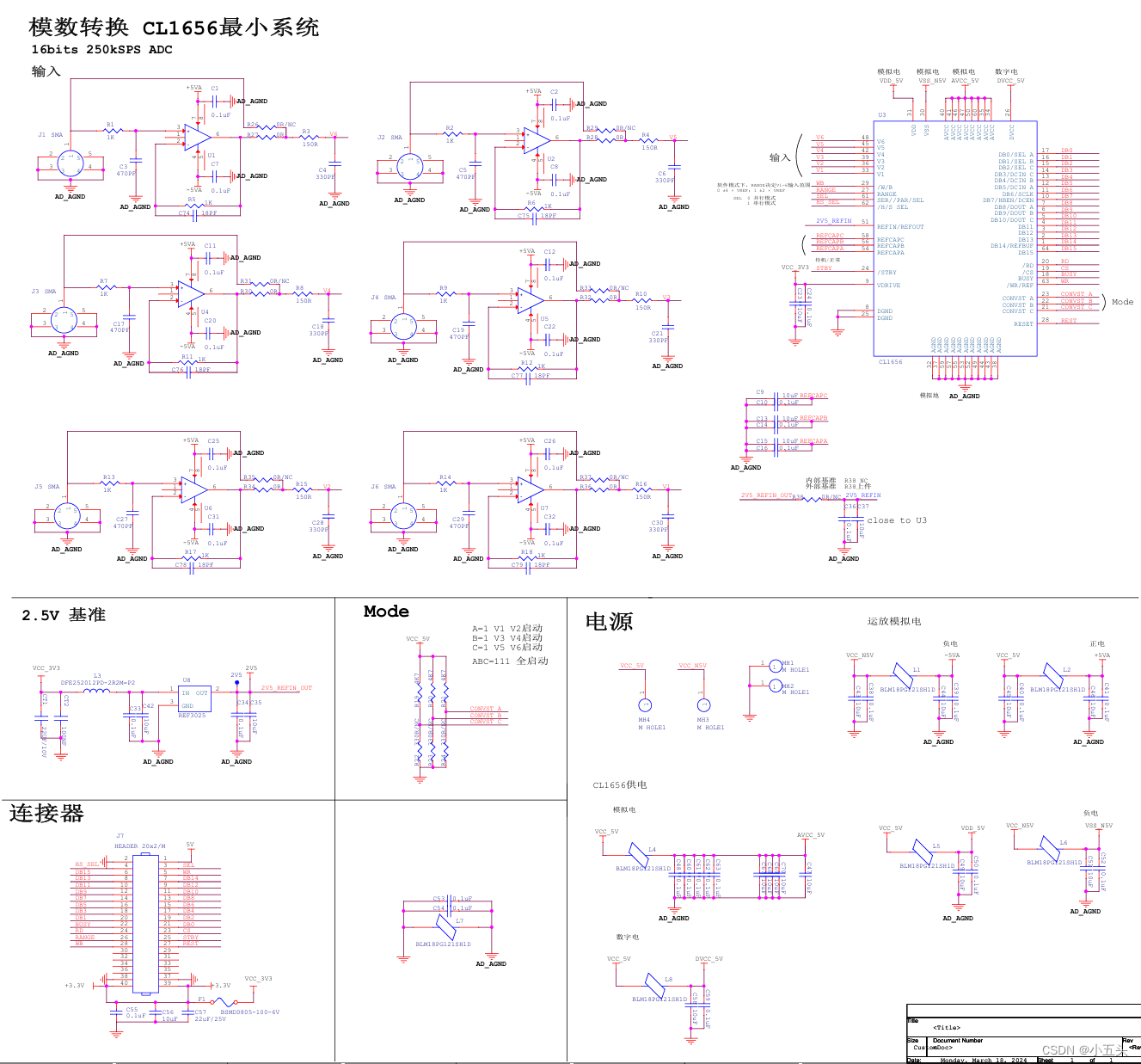

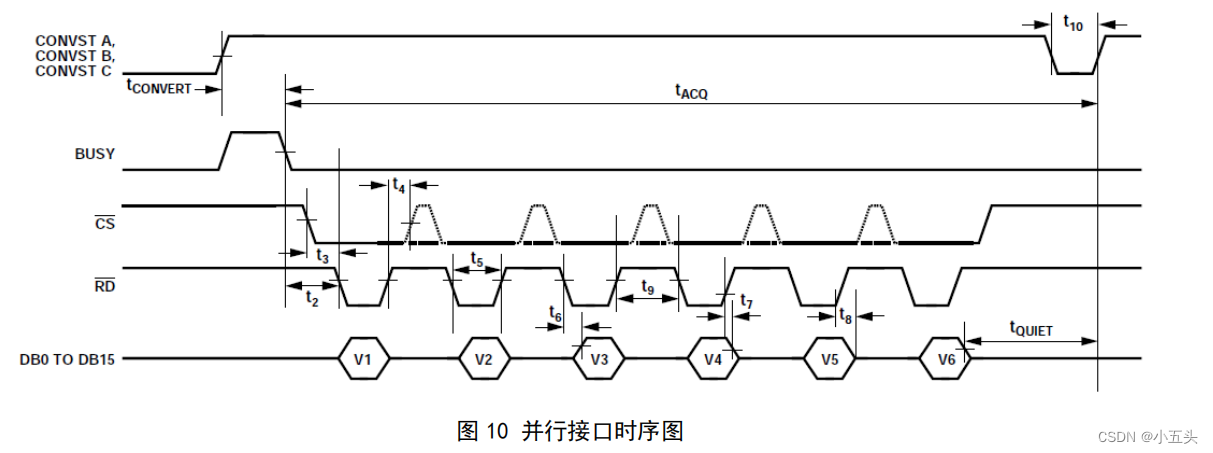

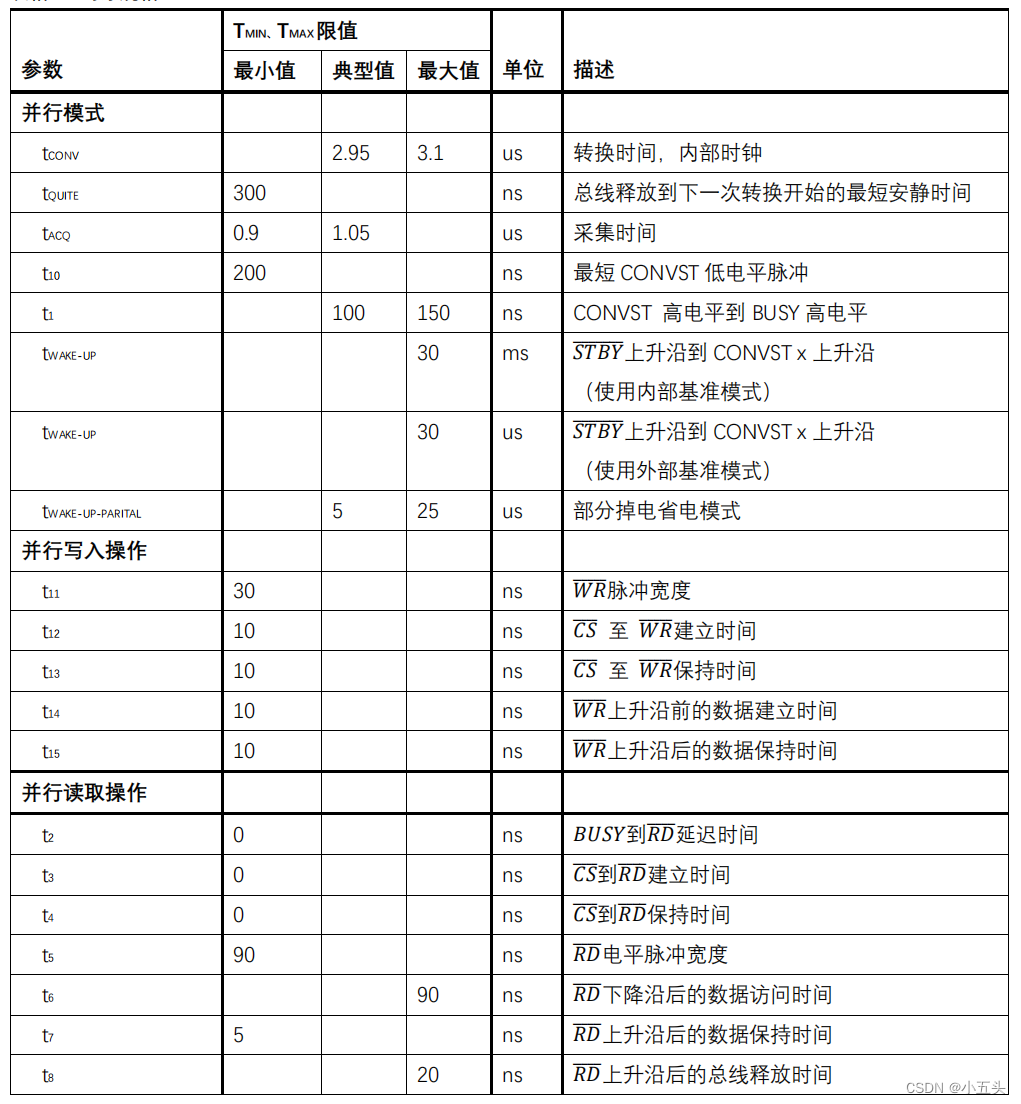

IV. 实验教程主要内容

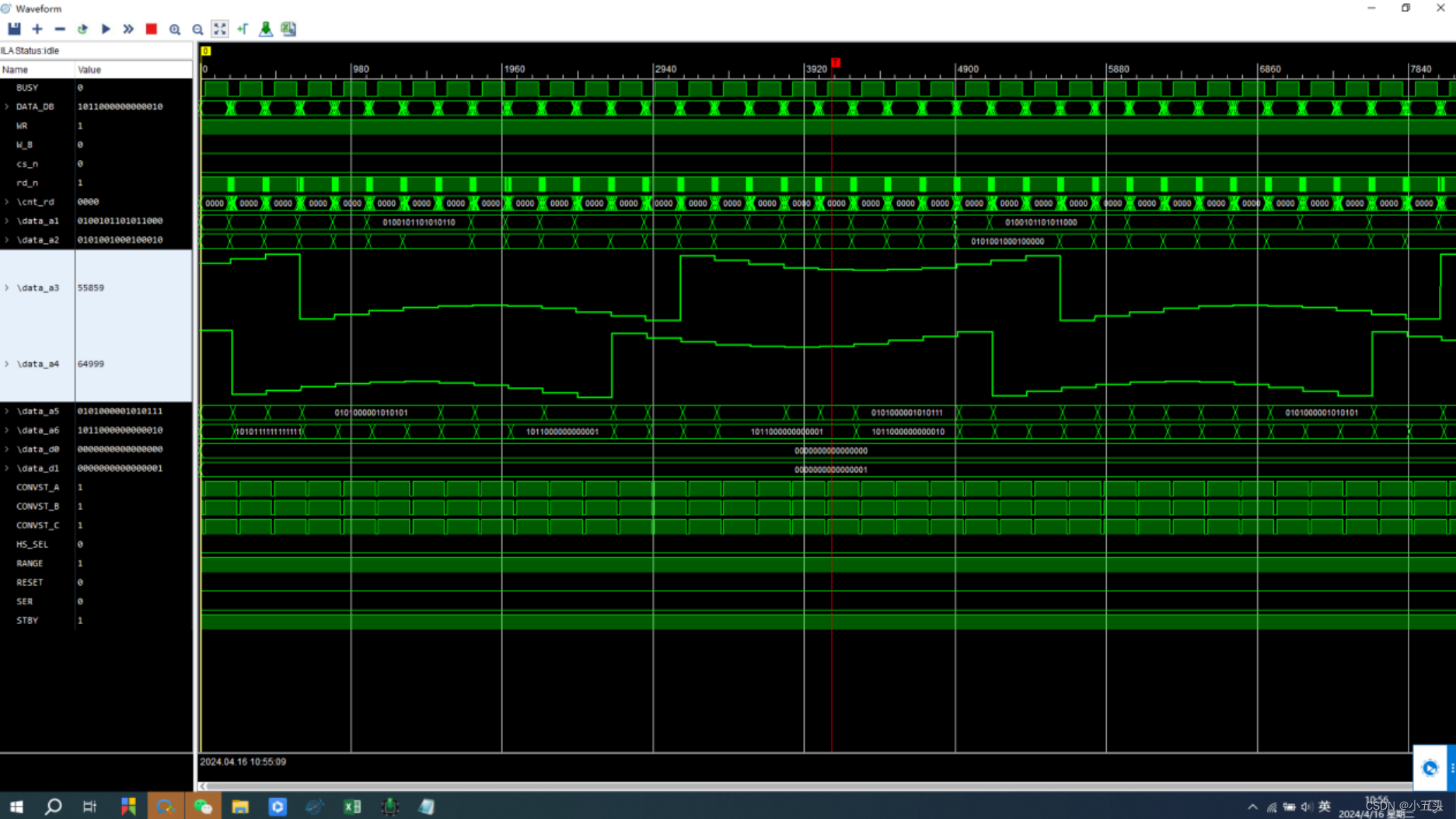

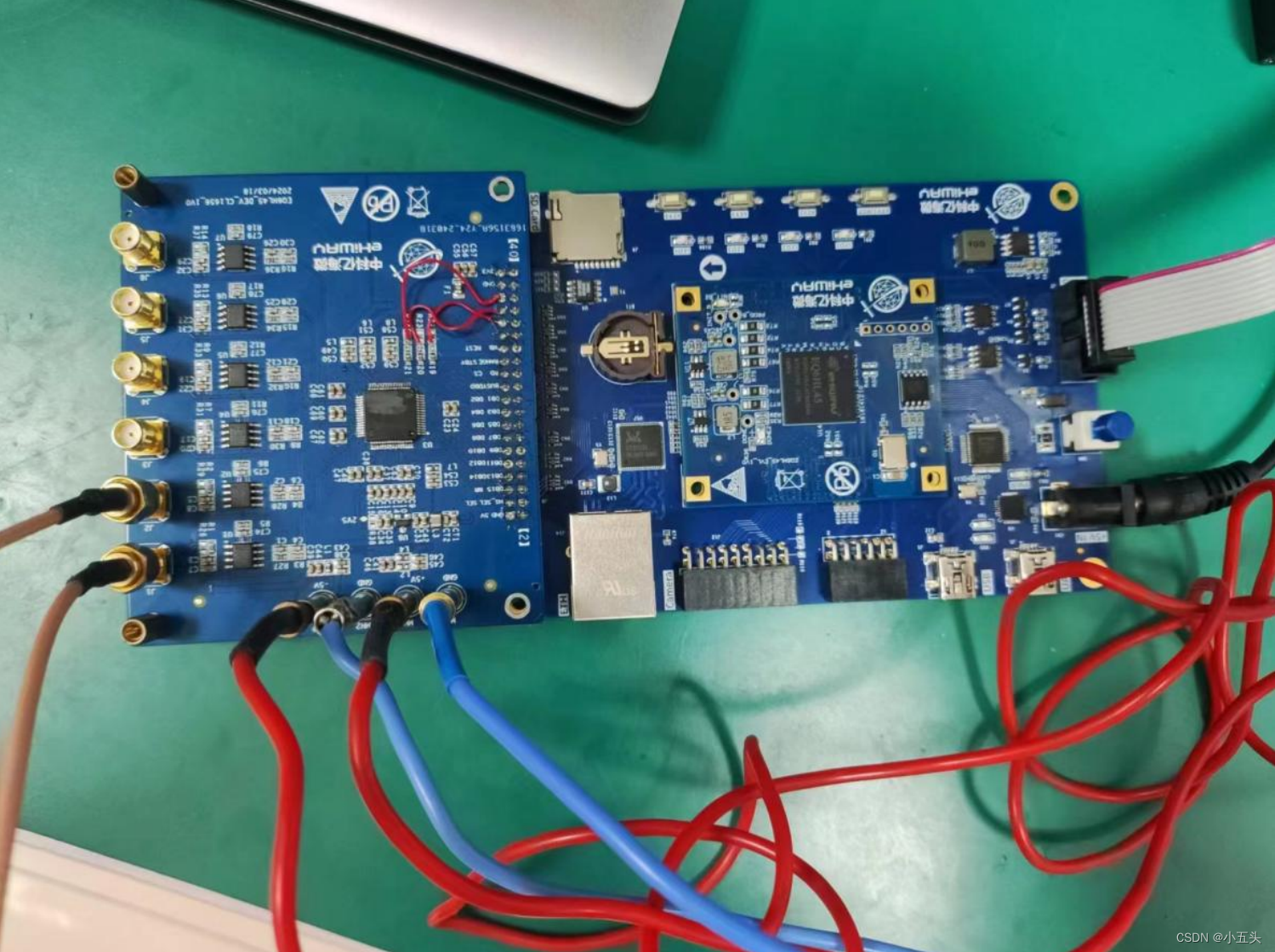

通过对CL1656芯片的学习,掌握了 FPGA的使用方法,并且编写了实验教程,使用中科亿海微公司的EQ6HL45开发板进行实验,使用上位机软件对实验过程进行了监控。结果表明,通过实验教程的编写,使学生对CL1656芯片的应用更加熟练,同时也使学生了解了 FPGA芯片开发流程。

实验教程的编写是在EQ6HL45开发板上,使用中科亿海微公司的eLinx3.0.5软件来完成的,编写之前首先对CL1656的芯片功能进行了解,然后对实验所用的EQ6HL45开发板进行配置,最后编写实验教程。由于硬件环境已经配置好了,接下来要对实验教程进行编写。编写过程中使用了 Modelsim 软件来进行编译和仿真,与eLinx3.0.5软件自带的debug工具。

A. 电路设计基础

B. Verilog程序设计

`timescale 1 ps/ 1 ps

//

// Company:

// Engineer:

//

// Create Date: 04-10-2024 10:59:08

// Design Name:

// Module Name: TOP

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Additional Comments:

//

//

module TOP(

input wire clk_50m,

input wire rst_n,

input wire BUSY,

input [15:0] DATA_DB,

//模式选择

output reg SER/*synthesis noprune*/,

// output reg PAR,

output reg HS_SEL/*synthesis noprune*/,

output reg STBY/*synthesis noprune*/,

output reg RANGE/*synthesis noprune*/,

output reg RESET/*synthesis noprune*/,

output reg WR/*synthesis noprune*/,

output reg W_B/*synthesis noprune*/,

output reg cs_n/*synthesis noprune*/,

output reg rd_n/*synthesis noprune*/,

output reg led,

output reg CONVST_A,

output reg CONVST_B,

output reg CONVST_C,

output reg test_1

);

reg [7:0] state/* synthesis preserve */;

reg BUSY_d0,BUSY_d1/* synthesis preserve */;

reg [3:0] cnt/* synthesis preserve */;

reg [15:0] REGL/* synthesis preserve */;

reg PAR/* synthesis preserve */;

reg SEL/* synthesis preserve */;

reg [25:0] count;

reg [3:0] sun;

reg [3:0] ool;

reg [3:0] ctate;

reg [3:0] cnt_rst;

reg [15:0] data_d0,data_d1/* synthesis preserve */;

reg [3:0] cnt_rd;

reg [15:0] data_a1,data_a2,data_a3,data_a4,data_a5,data_a6/* synthesis preserve */;

wire pos_BUSY/* synthesis preserve */;

assign pos_BUSY = BUSY_d0 & (!BUSY_d1);

always @ (posedge clk_50m or negedge rst_n) begin

if (!rst_n)

begin

data_d0 <= 16'd0;

data_d1 <= 16'd0;

end

else

begin

data_d0 <= !data_a1;

data_d1 <= data_d0 + 1;

end

end

always @ (posedge clk_50m or negedge rst_n) begin

if (!rst_n)

test_1 <= 1'b0;

else if (data_d0^data_d1^data_a1)

test_1 <= 1'b1;

else

test_1 <= 1'b0;

end

always @ (posedge clk_50m or negedge rst_n) begin

if (!rst_n)

begin

count <= 26'd0;

led <= 1'b0;

end

else if (count >= 25_000_000-1)

begin

count <= 26'd0;

led <= ~led;

end

else

begin

count <= count + 1'b1;

led <= led;

end

end

//上电复位100ns

always @ (posedge clk_50m or negedge rst_n) begin

if (!rst_n)

begin

RESET <= 1'b1;

sun <= 4'd0;

end

else if (sun == 5)

begin

RESET <= 1'b0;

sun <= sun;

end

else

begin

RESET <= 1'b1;

sun <= sun + 1'b1;

end

end

//并行模式

always @ (posedge clk_50m or negedge rst_n) begin

if (!rst_n)

begin

SER <= 1'b0;

PAR <= 1'b0;

SEL <= 1'b0;

W_B <= 1'b0;

HS_SEL<=1'b0;

WR <= 1'b0;

RANGE<= 1'b0;

STBY <= 1'b1;

end

else

begin

SER <= 1'b0;

PAR <= 1'b0;

SEL <= 1'b0;

W_B <= 1'b0;

HS_SEL<=1'b0;

WR <= 1'b1;

RANGE<= 1'b1;

STBY <= 1'b1;

end

end

always @ (posedge clk_50m or negedge rst_n) begin

if (!rst_n)

begin

ctate <= 4'd0;

cnt_rst <= 4'd0;

end

else

case (ctate)

0:begin

ctate <= ctate + 1'b1;

cnt_rst <= 4'd0;

end

1:begin

if (RESET == 0)

begin

ctate <= ctate + 1'b1;

cnt_rst <= 4'd0;

end

else

begin

ctate <= ctate;

cnt_rst <= 4'd0;

end

end

2:begin

if (cnt_rst == 10)

begin

ctate <= ctate + 1'b1;

cnt_rst <= 4'd0;

end

else

begin

ctate <= ctate;

cnt_rst <= cnt_rst + 1'b1;

end

end

3:begin

ctate <= ctate;

end

default : ;

endcase

end

always @ (posedge clk_50m or negedge rst_n) begin

if (!rst_n)

begin

BUSY_d0 <= 1'b0;

BUSY_d1 <= 1'b0;

end

else

begin

BUSY_d0 <= BUSY;

BUSY_d1 <= BUSY_d0;

end

end

always @ (posedge clk_50m or negedge rst_n) begin

if (!rst_n)

begin

data_a1 <= 16'd0;

data_a2 <= 16'd0;

data_a3 <= 16'd0;

data_a4 <= 16'd0;

data_a5 <= 16'd0;

data_a6 <= 16'd0;

end

else

case (cnt_rd)

1: if (rd_n) data_a1 <= DATA_DB; else data_a1 <= data_a1;

2: if (rd_n) data_a2 <= DATA_DB; else data_a2 <= data_a2;

3: if (rd_n) data_a3 <= DATA_DB; else data_a3 <= data_a3;

4: if (rd_n) data_a4 <= DATA_DB; else data_a4 <= data_a4;

5: if (rd_n) data_a5 <= DATA_DB; else data_a5 <= data_a5;

6: if (rd_n) data_a6 <= DATA_DB; else data_a6 <= data_a6;

default:;

endcase

end

always @ (posedge clk_50m or negedge rst_n) begin

if (!rst_n)

begin

cs_n <= 1'b0;

rd_n <= 1'b1;

CONVST_A<= 1'b0;

CONVST_B<= 1'b0;

CONVST_C<= 1'b0;

state <= 8'd0;

cnt <= 4'd0;

REGL <= 16'd0;

ool <= 4'd0;

cnt_rd <= 4'd0;

end

else

case (state)

0:begin

if (ctate == 3)

begin

cs_n <= 1'b0;

rd_n <= 1'b1;

CONVST_A<= 1'b0;

CONVST_B<= 1'b0;

CONVST_C<= 1'b0;

cnt <= 4'd0;

REGL <= REGL;

state <= state + 1'b1;

ool <= 4'd0;

cnt_rd <= 4'd0;

end

else

begin

state <= state;

end

end

1:begin

CONVST_A<= 1'b1;

CONVST_B<= 1'b1;

CONVST_C<= 1'b1;

if (BUSY_d1)

begin

state <= state + 1'b1;

cs_n <= 1'b0;

end

else

begin

state <= state;

cs_n <= 1'b0;

end

end

2:begin

if (BUSY_d1 == 0)

state <= state + 1'b1;

else

state <= state;

end

3:begin

if (ool >= 5)

begin

ool <= 4'd0;

rd_n <= 1'b1;

state <= state + 1'b1;

cnt_rd <= cnt_rd + 1'b1;

end

else

begin

rd_n <= 1'b0; //请求数据

ool <= ool + 1'b1;

end

end

4:begin

if (cnt_rd >= 6)

begin

state <= state + 1'b1;

cnt_rd <= 4'd0;

end

else

begin

cnt_rd <= cnt_rd;

state <= state - 1'b1;

end

end

5:begin

if (ool >= 15)

begin

ool <= 4'd0;

state <= state + 1'b1;

CONVST_A<= 1'b0;

CONVST_B<= 1'b0;

CONVST_C<= 1'b0;

end

else

begin

CONVST_A<= 1'b1;

CONVST_B<= 1'b1;

CONVST_C<= 1'b1;

state <= state;

ool <= ool + 1'b1;

end

end

6:begin

if (ool >= 15)

begin

ool <= 4'd0;

state <= 0;

end

else

begin

state <= state;

ool <= ool + 1'b1;

end

end

default : ;

endcase

end

endmoduleV. 实验设计与步骤

A. 实验环境搭建

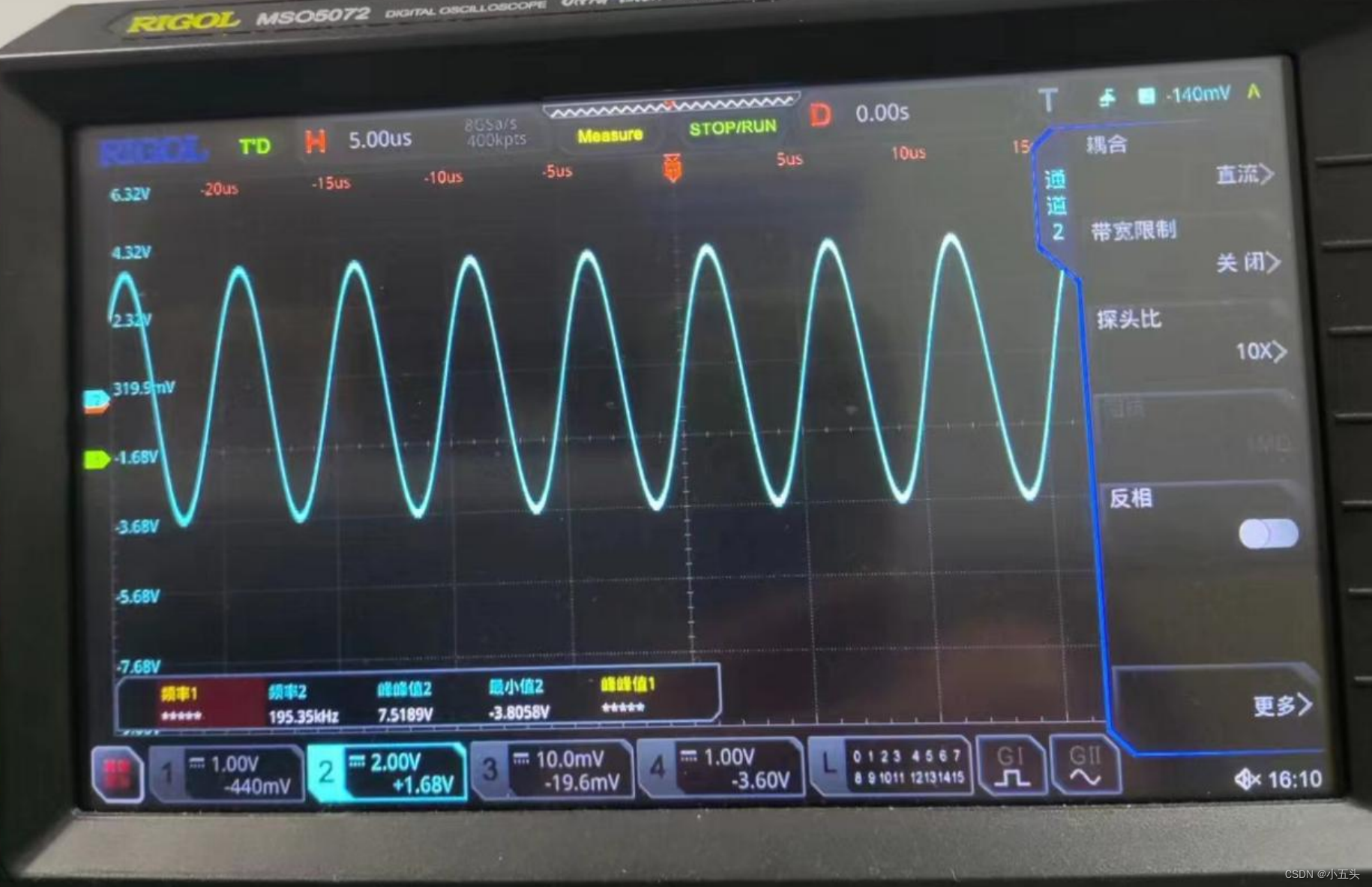

示波器输出采样波形10kHz 峰峰值5V

V3V4通道采样,测算波形频率10kHz

B.实验结果分析与讨论