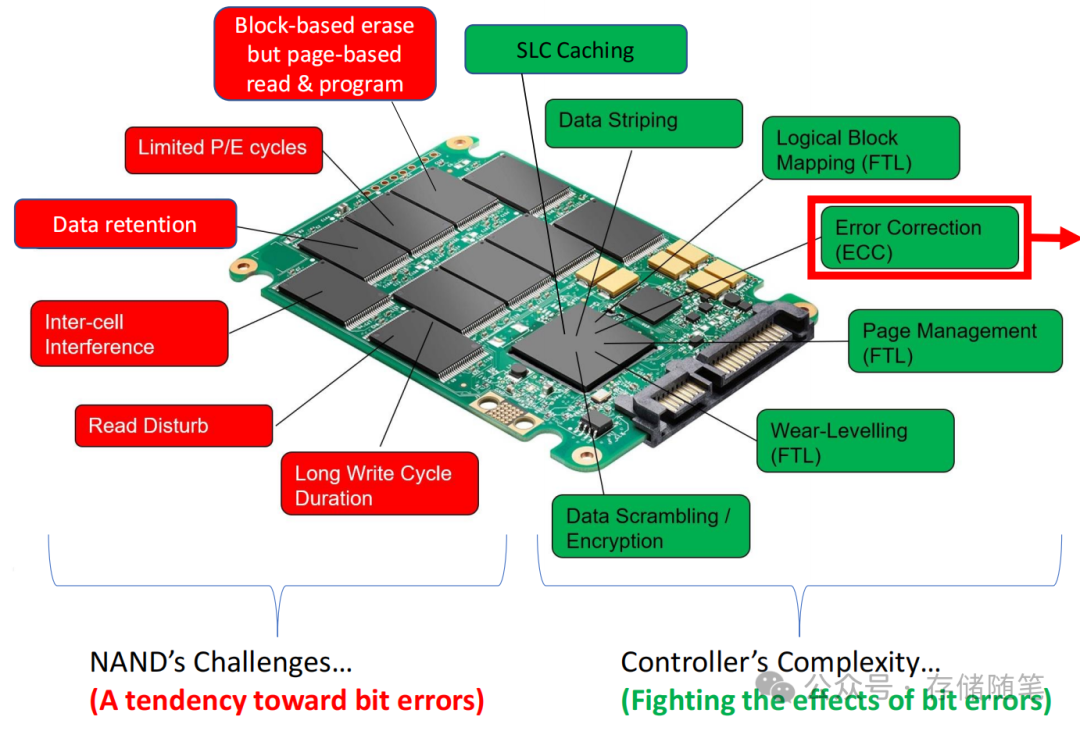

NAND Flash是固态硬盘(SSD)的核心数据存储。然而,NAND Flash因其物理特性和工作原理,存在一定的内在脆弱性,尤其是在数据存储的长期可靠性方面。

比特错误是指在读取NAND Flash时,原本存储的二进制位(比特)与读取结果不符的现象。以下为导致比特错误的几个主要原因:

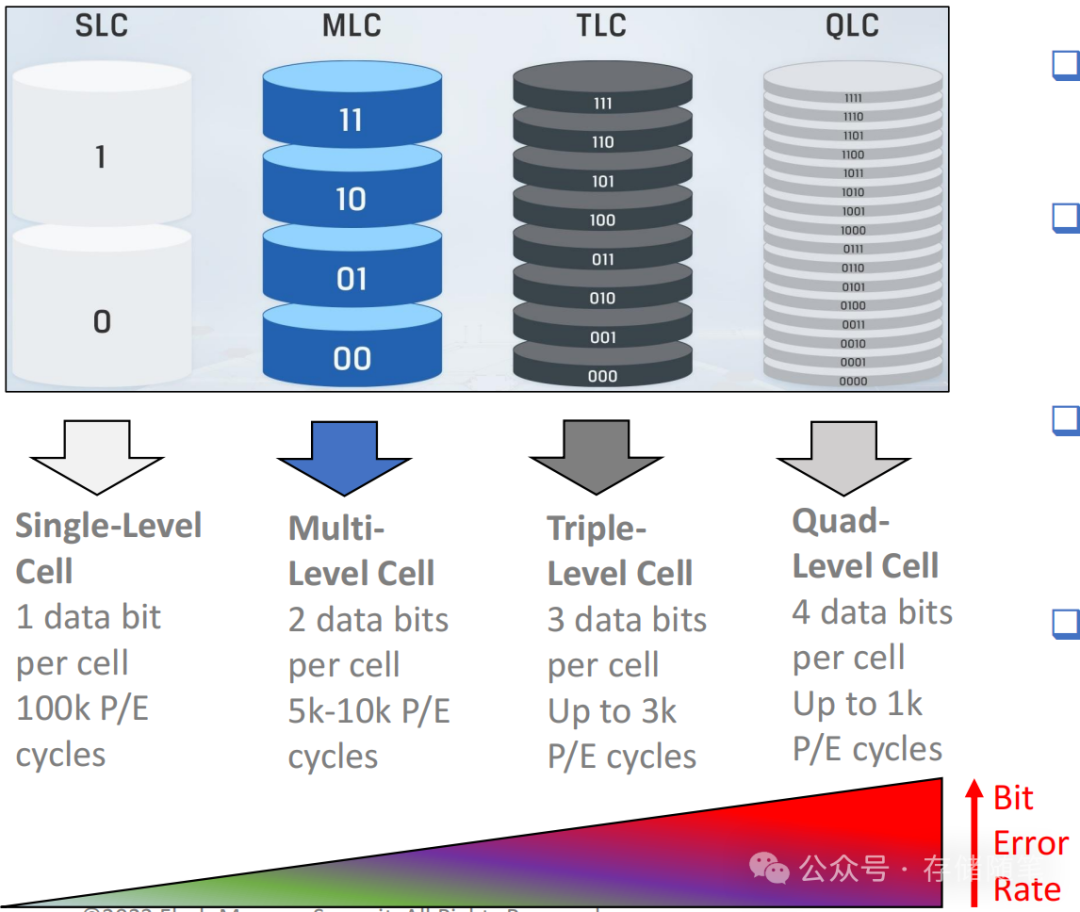

(1)耐久性限制(P/E周期)

NAND Flash通过改变电荷状态来存储数据,但每经过一次编程(写入)和擦除(清除)操作(称为P/E周期),存储单元的电荷捕获能力就会减弱,导致数据保持能力下降。随着P/E周期次数增加,比特错误率(BER)随之上升。

(2)电荷逃逸(电子脱阱)

长期存储后,存储单元内原本稳定的电荷可能会由于绝缘层缺陷、热激发等原因逐渐逃逸,使得存储的信息发生改变,产生比特错误。

(3)读取干扰(临近单元)

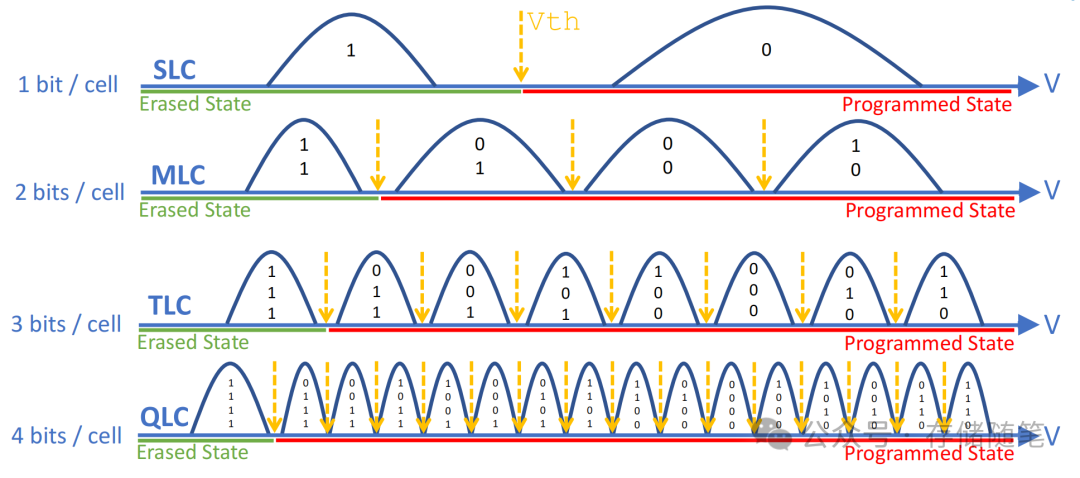

在读取某个存储单元时,施加的电压可能会对相邻单元产生影响,导致它们的电荷状态轻微变化,尤其是在高密度多级单元(如MLC、TLC、QLC)中更为显著。这种效应随时间累积,可引起比特错误。

(4)工作与存储温度

过高或过低的工作温度会影响NAND芯片内部电荷的稳定性,加速电荷逃逸或导致电荷捕获异常。此外,存储环境温度的变化也会影响数据的长期保留质量,间接增加比特错误的发生概率。

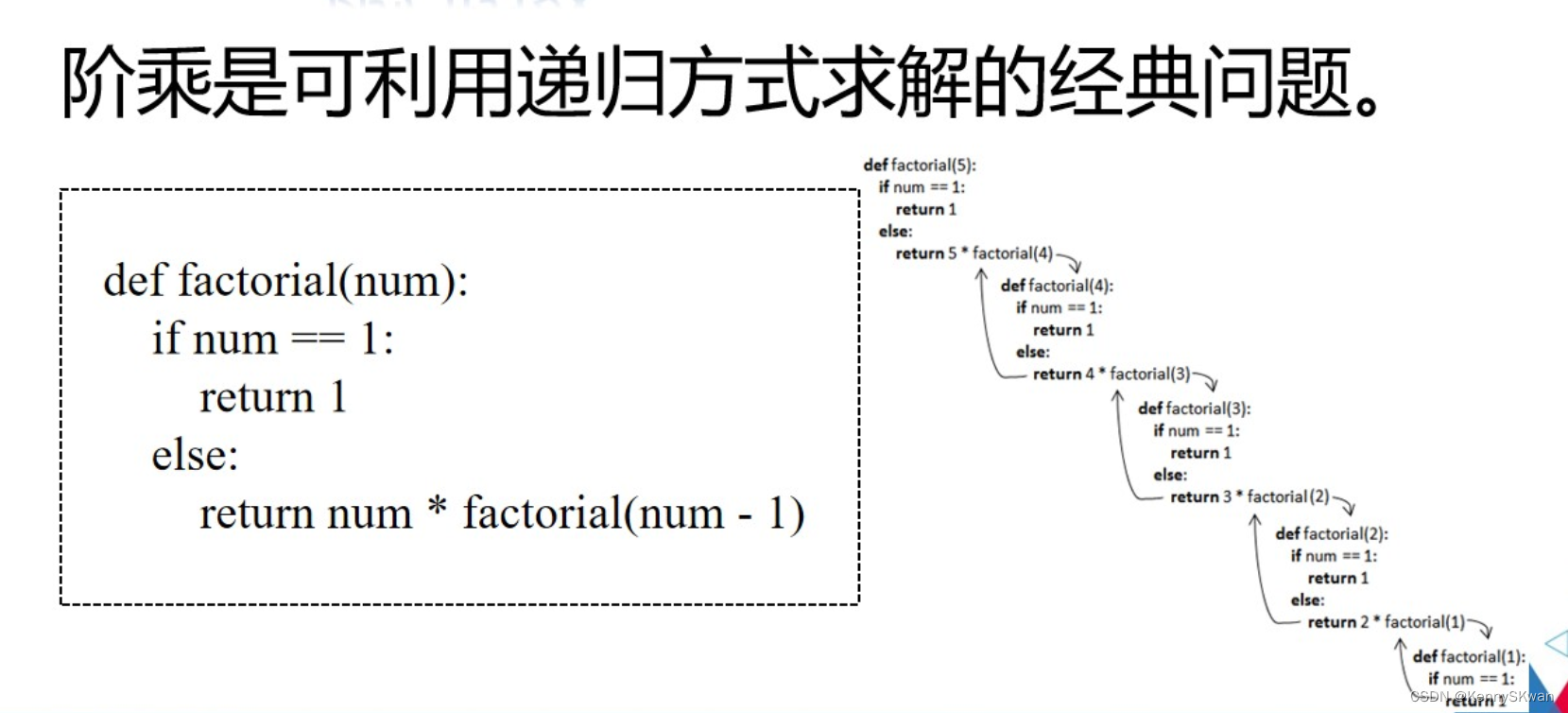

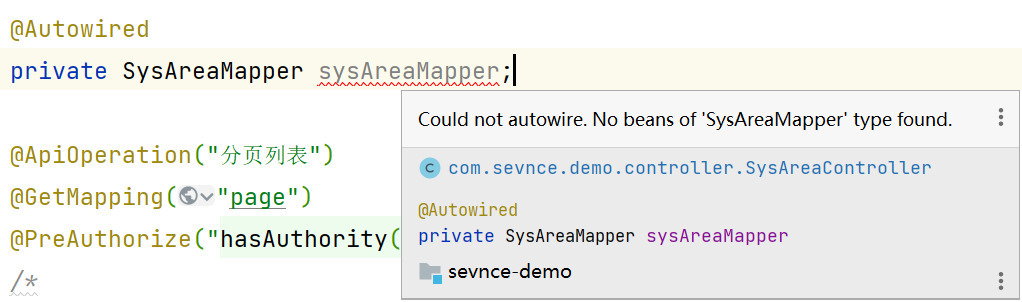

(5)控制器应对比特错误

由于NAND Flash固有的比特错误倾向,控制器设计必须包含复杂的错误校正机制,如BCH码、LDPC码等错误纠正码(ECC),以检测并纠正一定数量的比特错误。控制器还采用块擦除但按页读写的方式,以及SLC缓存策略(将MLC/TLC/QLC单元模拟为SLC单元进行高速写入),以提高整体性能和数据可靠性。

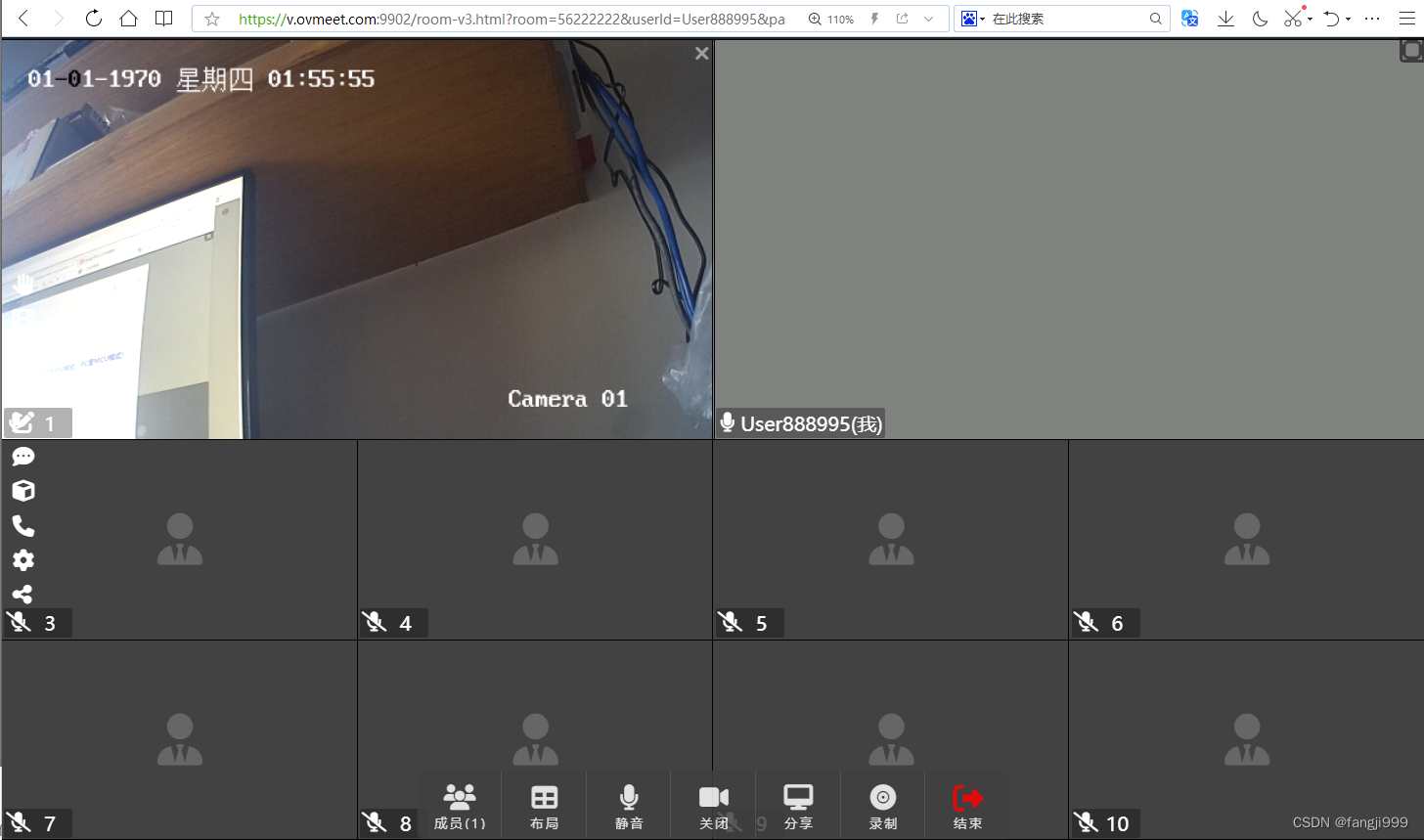

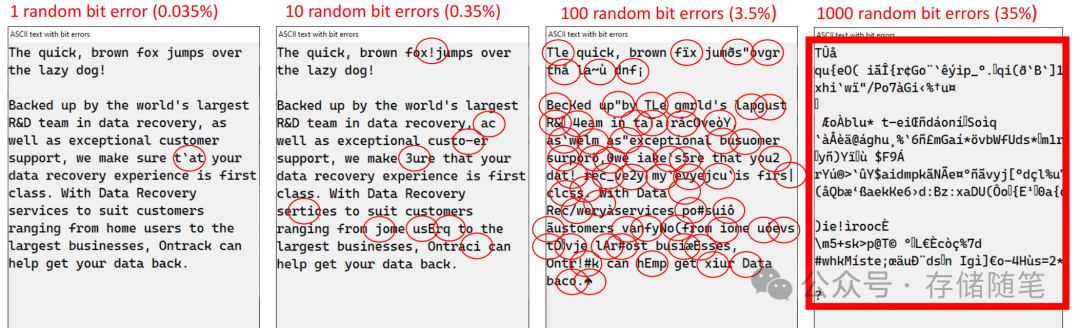

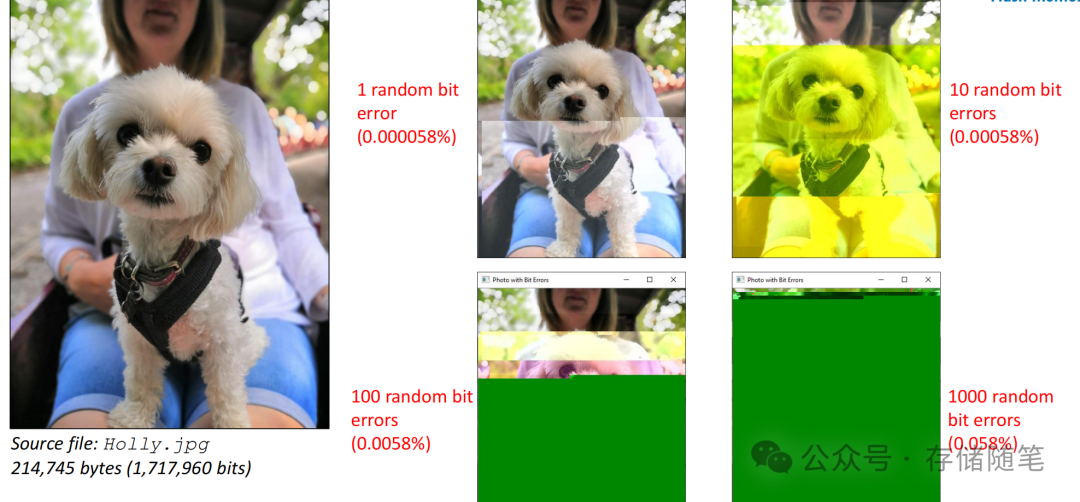

出现bit错误数量,对用户数据的影响也不影响,下面图片可以直观对比看下:

如果是装了系统的情况,还有可能导致系统蓝屏:

在数据丢失或SSD故障的情况下,数据恢复专家会采用多种技术来恢复数据:

-

芯片原位法:利用原始控制器进行诊断、维修和固件修复,有时需要定制硬件和深入理解控制器逻辑。这种方法相对直接但可能风险较高,且对某些复杂故障或加密数据处理效率低下。

-

芯片离线法:移除NAND芯片,直接读取物理数据,然后通过软件模拟或逆向工程解析数据。此方法虽能提供对物理数据的只读访问,降低进一步数据风险,但处理过程复杂,尤其当面对硬件加密或特定控制器特性时。

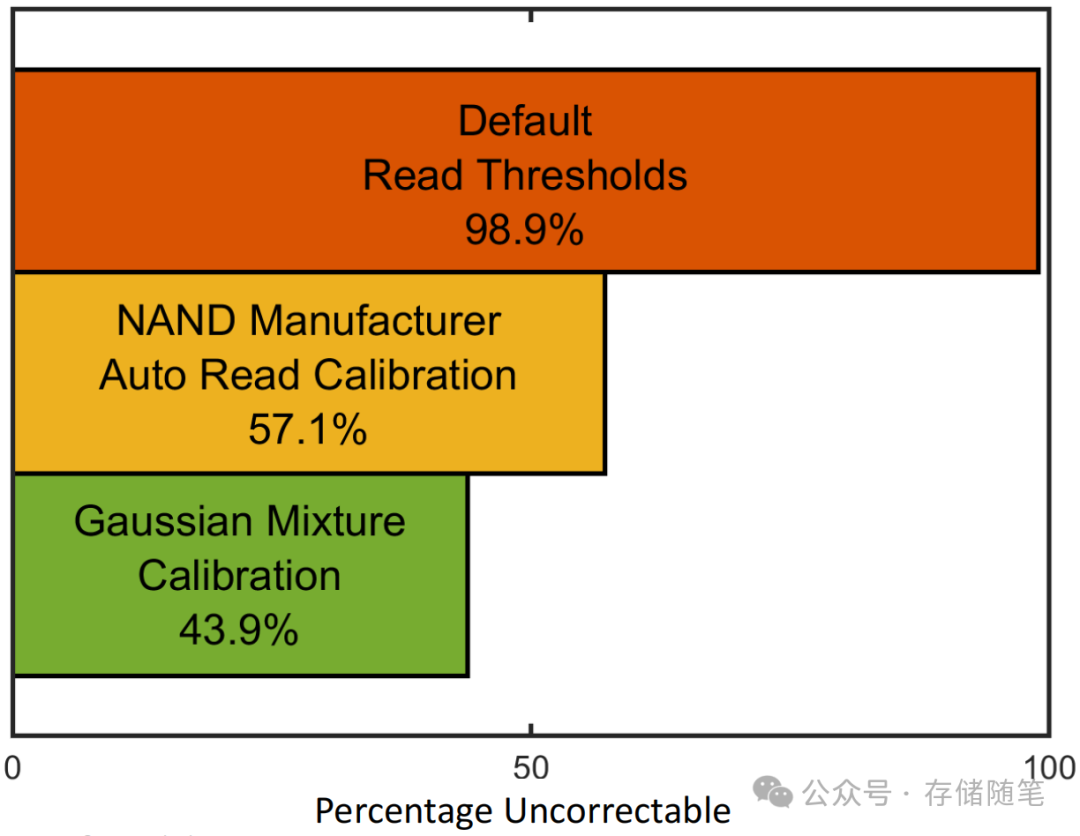

现有的数据恢复技术,如读重试、读偏移和自动读取校准,虽然能在一定程度上应对比特错误,但其效果受NAND密度、老化程度和使用情况影响显著,且缺乏统一标准,易受固件工程师解读差异影响。在实践中,为了追求性能,有时会牺牲校准精度,导致数据修复能力受限。特别是对于采用QLC NAND的SSD,一旦比特错误率开始上升,自动读取校准可能表现不佳。

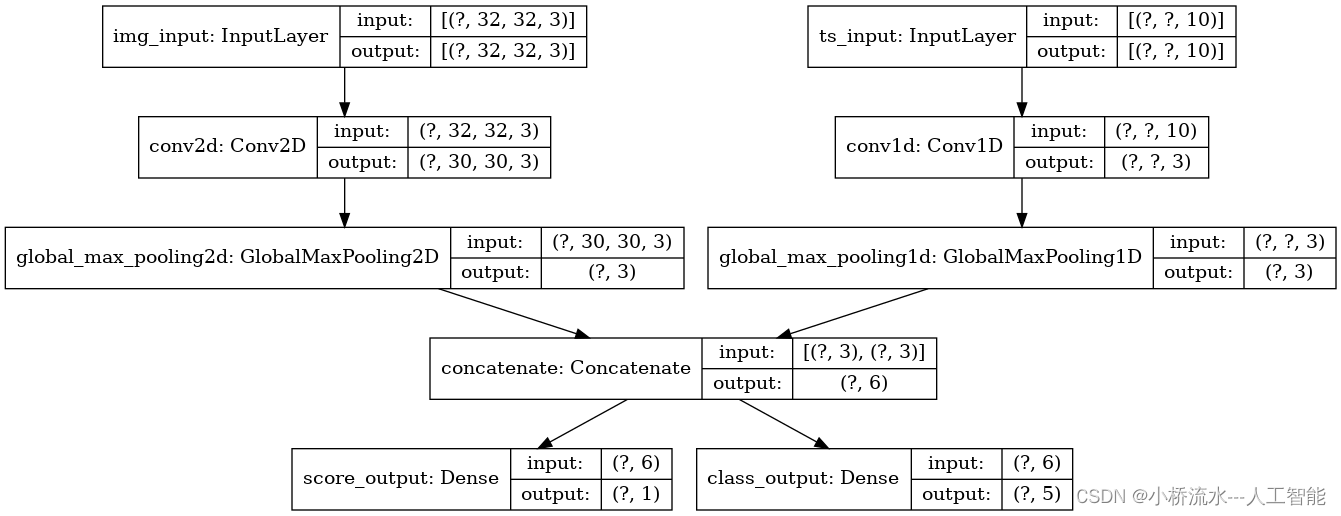

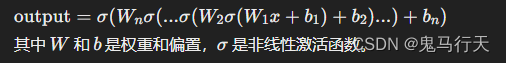

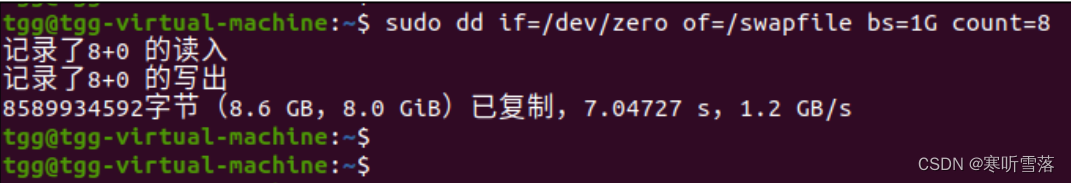

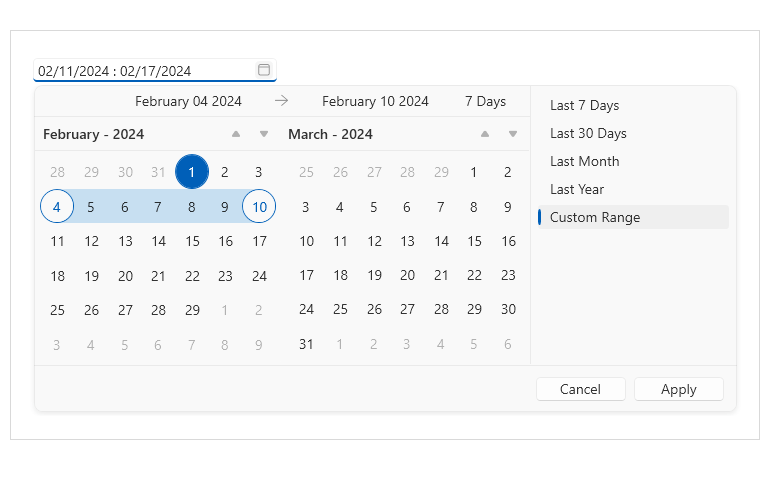

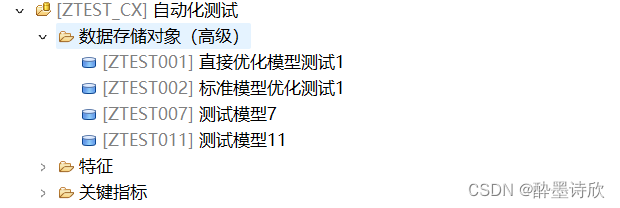

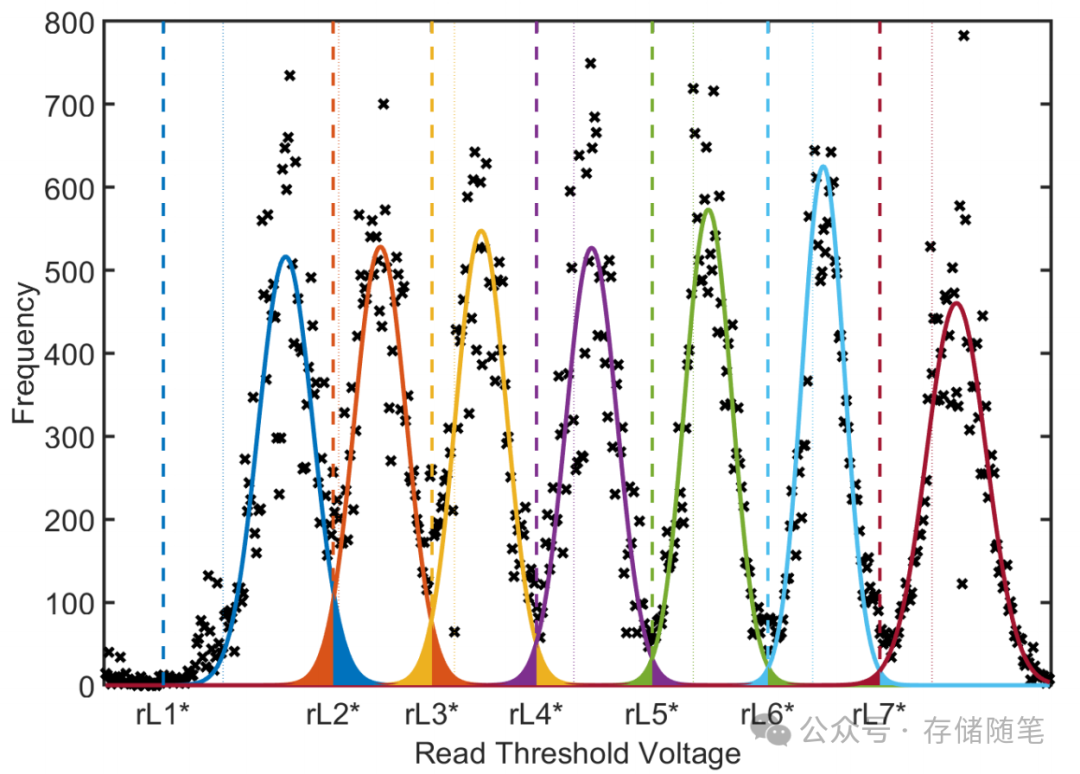

为实现更优的校准,研究人员提出了一种基于高斯混合模型的方法,通过制作NAND VT图像(多次读取并微调读阈值),获取电压分布,再进行数据拟合,找到最优读阈值,从而最大限度减少数据完整性错误。这种方法独立于ECC类型、NAND制造商特定命令,仅利用NAND的标准特性,无需封装或改动NAND封装,且不需要预先了解存储数据。通过高斯分布的平滑估计,能够应对瞬态误差影响,估算并最小化数据完整性错误。

通过高斯混合校准,不可纠正数据量减少至44%,但仍有一大部分未被纠正。该方法解决了不正确谷底确定的问题,但只能纠正低页数据。相较于读重试和自动读取校准,高斯混合校准能更大程度地减少不可纠正数据,确定更精确的最优读阈值,对不正确谷底判断的敏感性较低,且具有可验证性和适应性。能生成电压分布、数据拟合和最优阈值的视觉检查,当有不同数据拟合模型可用时,最优图像可调整,拟合模型可根据不同NAND厂商设备定制。

数据恢复专家则运用多种策略和技术来恢复因比特错误导致的数据丢失。其中,高斯混合校准作为一种创新方法,旨在优化读阈值设置,提高数据恢复过程中比特错误的纠正效率,为克服现有校准方法的局限性提供了新的思路。

参考文献:Eliminating controller-based reverse-engineering in NAND Flash chip-off data recovery

如果您看完有所受益,欢迎点击文章底部左下角“关注”并点击“分享”、“在看”,非常感谢!

精彩推荐:

-

CXL与PCIe世界的尽头|你相信光吗?

-

全景剖析SSD SLC Cache缓存设计原理

-

存储革新:下一代低功耗PCM相变存储器

-

3D DRAM虽困难重重,最快明年到来

-

字节跳动入局存储内存SCM

-

解读“CFMS中国闪存市场峰会”存储技术看点

-

首个业内DNA存储技术规范发布

-

如何突破SSD容量提升的瓶颈?

-

固态存储是未来|浅析SSD架构的演进与创新技术

-

论文解读:NAND闪存中读电压和LDPC纠错码的高效设计

-

华为新发布磁电存储“王炸”,到底是什么?

-

SSD LDPC软错误探测方案解读

-

关于SSD LDPC纠错能力的基础探究

-

存储系统如何规避数据静默错误?

-

PCIe P2P DMA全景解读

-

深度解读NVMe计算存储协议

-

对于超低延迟SSD,IO调度器已经过时了吗?

-

浅析CXL P2P DMA加速数据传输的原理

-

NVMe over CXL技术如何加速Host与SSD数据传输?

-

浅析LDPC软解码对SSD延迟的影响

-

为什么QLC NAND才是ZNS SSD最大的赢家?

-

SSD在AI发展中的关键作用:从高速缓存到数据湖

-

浅析不同NAND架构的差异与影响

-

SSD基础架构与NAND IO并发问题探讨

-

字节跳动ZNS SSD应用案例解析

-

CXL崛起:2024启航,2025年开启新时代

-

NVMe SSD:ZNS与FDP对决,你选谁?

-

浅析PCI配置空间

-

浅析PCIe系统性能

-

存储随笔《NVMe专题》大合集及PDF版正式发布!

如果您也想针对存储行业分享自己的想法和经验,诚挚欢迎您的大作。

投稿邮箱:Memory_logger@163.com (投稿就有惊喜哦~)

《存储随笔》自媒体矩阵

更多存储随笔科普视频讲解,请移步B站账号:

如您有任何的建议与指正,敬请在文章底部留言,感谢您不吝指教!如有相关合作意向,请后台私信,小编会尽快给您取得联系,谢谢!