视频链接

M.2 B Key-5G模块 &(U)SIM卡电路设计01_哔哩哔哩_bilibili

M.2 B Key-5G模块 &(U)SIM卡电路设计

1、5G模块 &(U)SIM卡相关概念

1.1、5G模块(RM500Q-GL)

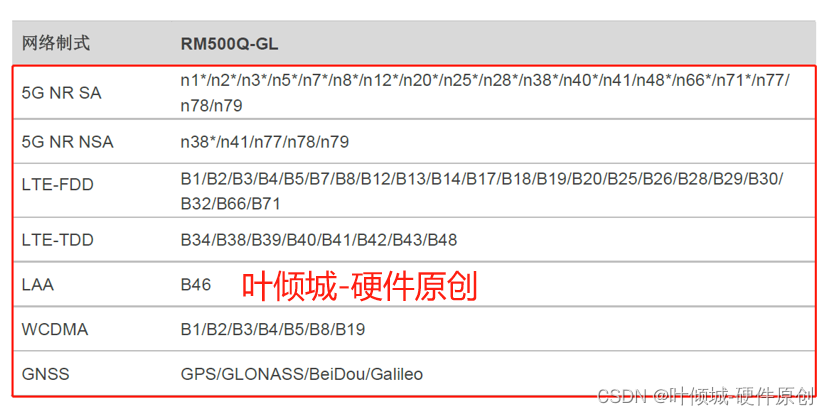

RM500Q-GL是一款支持分集接收功能的5G NR/LTE-A/UMTS/HSPA+无线通信模块。它符合标准的PCIe M.2 接口规范,支持5G NR SA/NSA、LTE-FDD、LTE-TDD、DC-HSDPA、HSPA+、HSDPA、HSUPA、WCDMA 等多种网络制式下的数据连接。

1.2、其他5G模块

1.3、(U)SIM卡

SIM卡是(Subscriber Identity Module 客户识别模块)

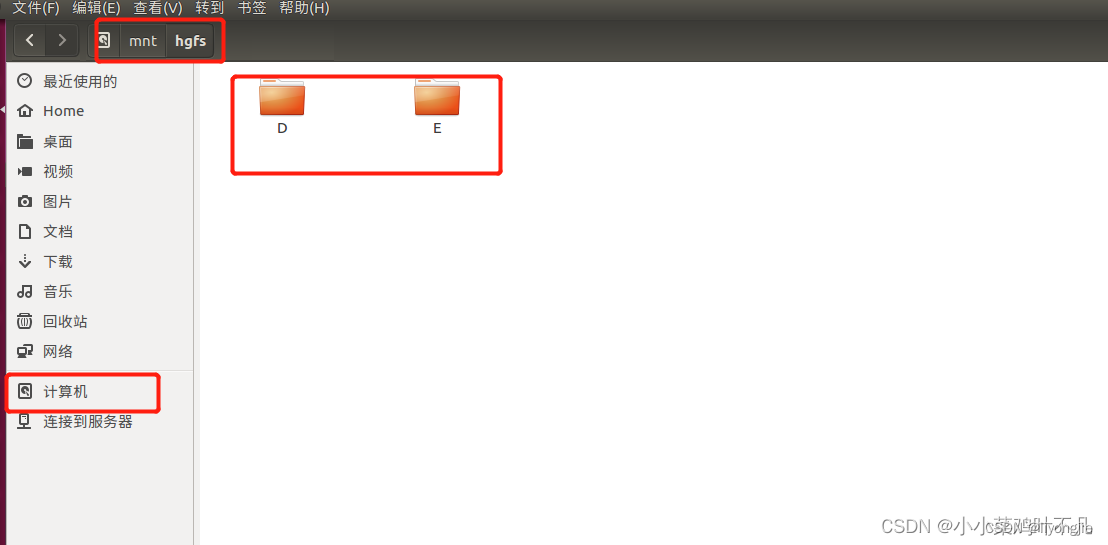

2、M.2 B Key接口类型和尺寸图

2.1、M.2基本介绍

M.2接口也叫NGFF,英文全称Next Generation Form Factor。对于5G模块来说,M.2采用B key。

2.2、M.2 socket接口类型和尺寸图

由于有多种尺寸和功能的M.2接口,因此需要规定一个标准的命名规则来划分这些接口。M.2接口的命名主要遵循以下原则:

1、适配器尺寸。(长和宽)

2、适配器最顶层到最底层的最大Z轴高度。

3、机械连接键(Mechanical Connector Key )的位置。

| KEY | 引脚 | 应用 |

| A | 8-15 | 2xPCIex1/USB2.0/I2C/DPx4 |

| B | 12-19 | PCIex2/SATA/USB2.0/USB3.1 Gen1/HSIC/SSIC/Audio/UIM/I2C/SMBus |

| C | 16-23 | PCIe/MPCIe/USB2.0/USB3.1 Gen1/SSIC/I2C-SlimBus/UIM/ANTCTL |

| D | 20-27 | 未使用 |

| E | 24-31 | 2xPCIex1/USB2.0/I2C/SDIO/UART/PCM |

| F | 28-35 | FMI |

| G | 39-46 | Generic |

| H | 43-50 | 未使用 |

| J | 47-54 | 未使用 |

| K | 51-58 | 未使用 |

| L | 55-62 | 未使用 |

| M | 59-66 | PCIex4/SATA/SMBus |

2.3、B key M.2 缺口处少12-19

B key的防呆键位于插槽的左方。

| 分类 | 图示 | 说明 |

| Socket 2 B key |  | 支持sata,pcie x2。 传输模式变为SATA或PCI-E X2,支持SSD, WWAN或者其他主要key界面。 |

2.4、B-key-socket2

B-Key的SSD已淘汰,但是可以用于5G模块等。

3、RM500Q-GL (5G模块)

3.1、RM500G-GL概述

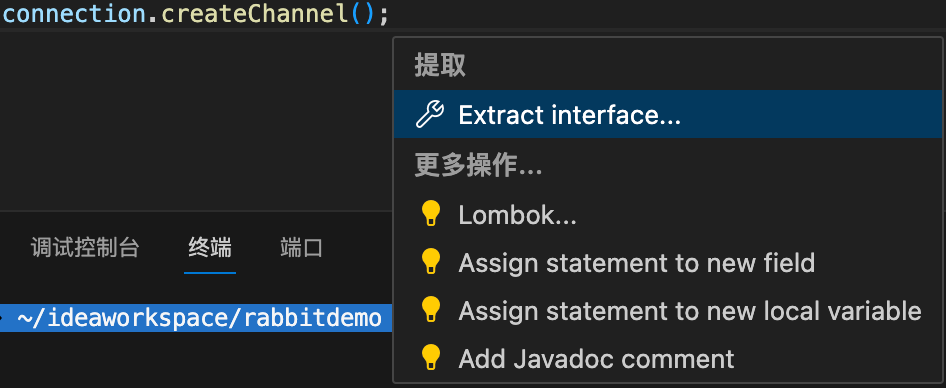

3.1.1、RM500Q-GL 模块支持的频段和GNSS类型

3.1.2、RM500Q-GL模块的主要特性

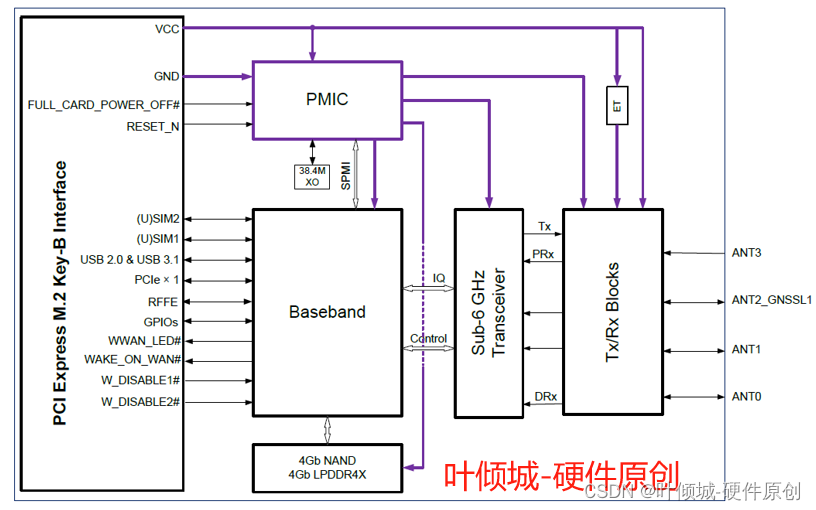

3.2、功能框图

3.3、管脚定义

3.3.1、电源

| Pin number | Pin name | Description |

| 3、5、11、27、33、39、45、51、57、71、73 (11个) | GND | GND |

| 2、4、70、72、74 (5个) | VCC | 3.135~4.4V直流源供电,典型值为3.7V |

| 65 | RFFE_VIO_1V8 | MIPI RFFE供电电源 1.8V电压源输出 |

3.3.2、 模块开关机&复位引脚(★对应4.1)

| Pin number | Pin name | Description |

| 6 | FULL_CARD_POWER_OFF# | 模块开/关机 |

| 67 | RESET_N | 模块复位 |

3.3.3、 (U)SIM接口引脚定义 (★对应4.2)

| Pin number | Pin name | I/O | Description |

| 36 | USIM1_VDD | PO | (U)SIM1卡供电电源 Class B (3.0V)或Class C(1.8V)卡 |

| 34 | USIM1_DATA | IO | (U)SIM1卡数据 1.8/3.0V电压域 |

| 32 | USIM1_CLK | DO | (U)SIM1卡时钟 1.8/3.0V电压域 |

| 30 | USIM1_RST | DO | (U)SIM1卡复位 1.8/3.0V电压域 |

| 66 | USIM1_DET | DI | (U)SIM1卡检测 模块内部上拉至1.8V |

| 48 | USIM2_VDD | PO | (U)SIM2 卡供电电源 Class B (3.0V)或Class C (1.8V)卡 |

| 42 | USIM2_DATA | IO | (U)SIM2卡数据 1.8/3.0V电压域 |

| 44 | USIM2_CLK | DO | (U)SIM2卡时钟 1.8/3.0V电压域 |

| 46 | USIM2_RST | DO | (U)SIM2卡复位 1.8/3.0V电压域 |

| 40 | USIM2_DET | DI | (U)SIM2卡检测 模块内部上拉至1.8V |

3.3.4、 USB接口引脚定义 (★对应4.3)

| Pin number | Pin name | I/O | Description |

| 7 | USB_DP USB_DM | AI/AO | USB 2.0差分数据(-&+) 90Ω差分阻抗 |

| 9 | |||

| 29 | USB_SS_TX_M USB_SS_TX_P | AO | USB 3.1发送(-&+) 90Ω差分阻抗 |

| 31 | |||

| 35 | USB_SS_RX_M USB_SS_RX_P | AI | USB 3.1接收(-&+) 90Ω差分阻抗 |

| 37 |

3.3.5、 PCIe接口引脚定义 (★对应4.4)

| Pin number | Pin name | I/O | Description |

| 55 53 | PCIE_REFCLK_P PCIE_REFCLK_M | AI/AO | PCIe 参考时钟 (+) 100 MHz,差分阻抗为85Ω |

| 49 47 | PCIE_RX_P PCIE_RX_M | AI | P C I e 接 收 (+) 差分阻抗为85Ω |

| 43 41 | PCIE_TX_P PCIE_TX_M | AO | PCIe 发送 (+) 差分阻抗为85Ω |

| 50 | PCIE_RST_N | OD | PCIe 复位 |

| 52 | PCIE_CLKREQ_N | OD | PCIe 时钟请求 |

| 54 | PCIE_WAKE_N | OD | PCIe 唤醒 |

3.3.6、 控制和状态指示接口 (正在开发中)

| Pin number | Pin name | I/O | Description |

| 8 | W_DISABLE1# | DI | 飞行模式控制 |

| 10 | WWAN_LED#* | OD | 射频状态指示灯 (漏极开路;低电平有效) //WWAN_LED#信号用于指示模块的RF工作状态,该引脚灌电流最大为10mA。// |

| 23 | WAKE_ON_WAN# | OD | 唤醒主机 (漏极开路;低电平有效) |

| 25 | DPR* | DI | 动态降功率控制 (1.8V电压域;默认高电平) |

| 26 | W_DISABLE2# | DI | GNSS功能开启/关闭 (1.8/3.3V电压域;低电平有效) //RM500Q-GL可通过W_DISABLE2#引脚来打开或关闭GNSS功能。该引脚在模块内部默认上拉,兼容1.8V和3.3V两种电压域。拉低该引脚可关闭模块GNSS功能。// |

| 38 | SDX2AP_STATUS* | DO | 模块状态指示 (1.8V电压域) |

| 68 | AP2SDX_STATUS* | DI | AP状态指示 (1.8V电压域) |

3.3.7、 配置引脚

| CONFIG_0 (Pin 21) | CONFIG_1 (Pin 69) | CONFIG_2 (Pin 75) | CONFIG_3 (Pin 1) | 模块类型和主机接口 | 端口配置 |

| NC | GND | NC | NC | Quectel defined | N/A |

3.3.8、 PCM接口 (正在开发中)

| Pin number | Pin name | I/O | Description |

| 20 | PCM_CLK | IO | 1.8 V 电压域 主模式时,输出信号。 从模式时,输入信号。 如果未使用,请保持悬空状态。 |

| 22 | PCM_DIN | DI | 1.8 V 电压域 |

| 24 | PCM_DOUT | DO | 1.8 V 电压域 |

| 28 | PCM_SYNC | IO | 1.8 V 电压域 |

3.3.9、 COEX UART串口(正在开发中)

3.3.10、 天线调谐控制接口(正在开发中)

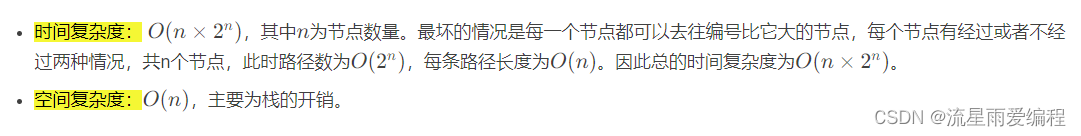

4、M.2 硬件设计要点(★)

4.1、复位按键注意项

拉低RESET_N引脚200~700ms可复位模块。如下图,可使用开集、开漏驱动电路或按键控制RESET_N 引脚。

1、NPN 驱动RESET_N复位电路

2、NMOS驱动RESET_N复位电路

3、按键复位电路

4.2、(U)SIM接口注意项(★)

1、常闭型 (U)SIM 卡槽

2、常开型 (U)SIM 卡槽

3、6-Pin (U)SIM 卡槽参考电路

4.3、USB接口注意事项(★)

RM500Q-GL提供了一个集成的通用串行总线(USB)接口。

4.4、PCIe接口注意事项

RM500Q-GL 支持Endpoint(EP)和Root Complex(RC)模式。

4.5、USB和PCIe通信协议

USB 模式

a、支持所有USB 2.0/3.1 功能

b、支持 MBIM/QMI/QRTR/AT

c、支持通过AT 命令从USB 模式切换至PCIe 模式

基于USB-AT 的PCIe 模式

a、支持MBIM/QMI/QRTR/AT

b、支持通过AT 命令从PCIe 模式切换回USB 模式

基于eFuse 的PCIe 模式

a、支持MBIM/QMI/QRTR/AT

b、支持非X86 系统和X86 系统(可满足BIOS PCIe 早期初始化功能)

4.6、其他

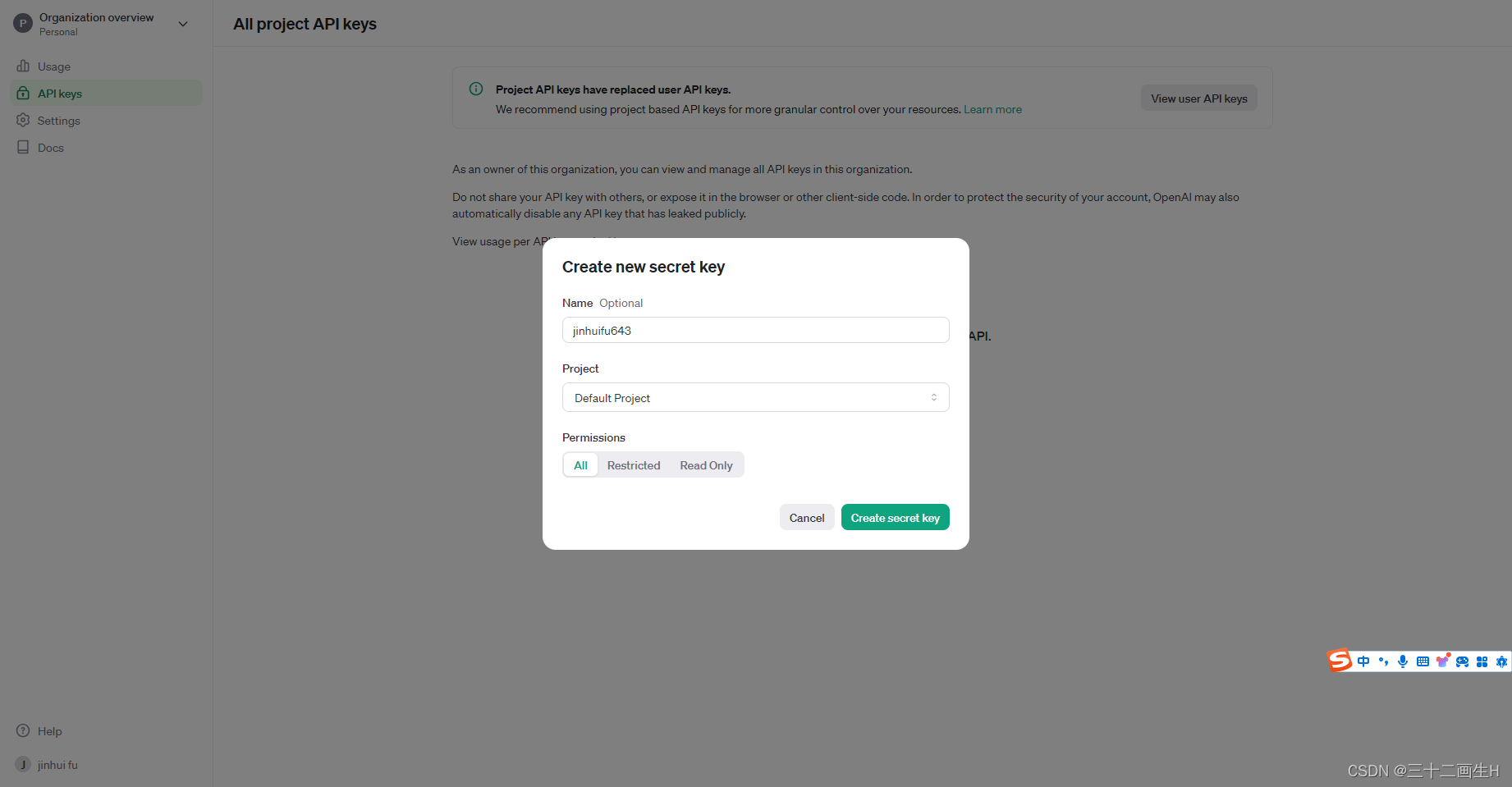

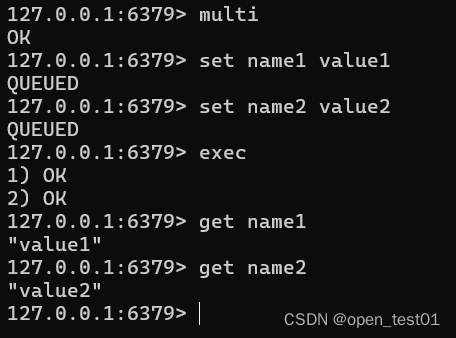

5、M.2-5G硬件实战 (USB协议)

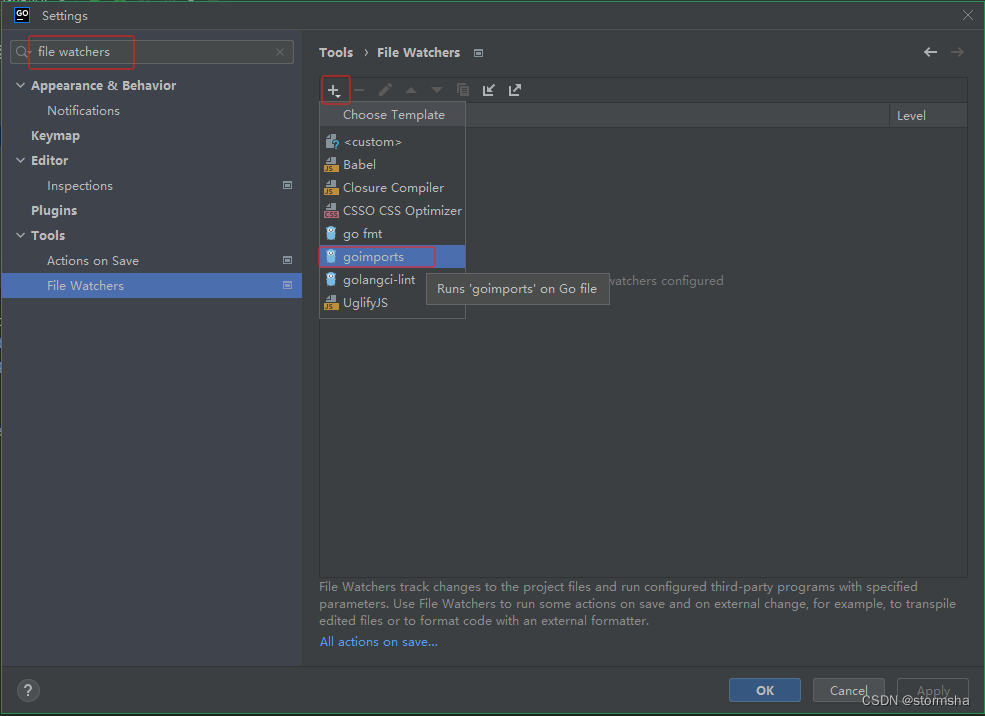

6、M.2 layout设计要点

6.1、M.2布局规范

1、M.2接口没有具体的定位要求,一般优先放置于板边,以便于插拔。

2、AC耦合电容靠近连接器摆放。(考虑直连后盘的stub长度)

3、差分信号上的耦合电容需放置到 M.2 conector 端且对称放置。

4、M.2与板平行,注意朝向板内。

6.2、M.2布线规范(★)

1、PCIe阻抗:100Ω±10%,USB阻抗:90Ω±10%

2、按差分形式布线,对内AC电容两端分段等长2mil,收发无等长要求。

3、M.2信号速率大于5Gbps时,按高速规范设计,伴地孔、圆弧、Stub最短等原则布线。

4、为减少串扰,同一层其它信号与差分信号线对之间的间距至少为走线相对于参考平面高度的6-10倍,一般控制在5W以上。

5、保持有完整的参考平面,确保阻抗的连续性。

6、差分远离晶振与clock信号以及电源信号。

7、差分与 GND anti-etch 的距离要 >20mils。

8、M.2焊盘及过孔需做挖空扯理,换层处加地过孔