文章目录

- 考纲

-

- 3.1 存储系统概述

- 3.2 主存储器

- 3.3 主存储器与CPU的连接

- 3.4 外部存储器

- 3.5 高速缓冲存储器

- 3.6 虚拟存储器

- 【※】存储系统总体流程图

- 【※】各个部件的存储位置

-

- 计算机存储相关硬件与数据结构说明

-

- 进程控制块(PCB)

- 页表

- 页表始址

- 页表始址寄存器(PTR)

- MMU(内存管理单元)

- TLB(Translation Lookaside Buffer,快表)

- Cache

- PS:

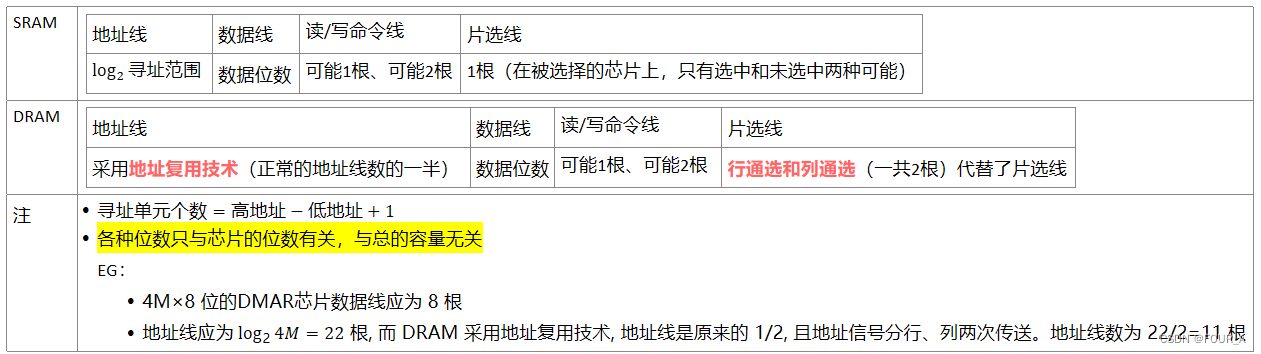

- 【※】DRAM芯片计算引脚的数目

-

- 计算芯片引脚的数目

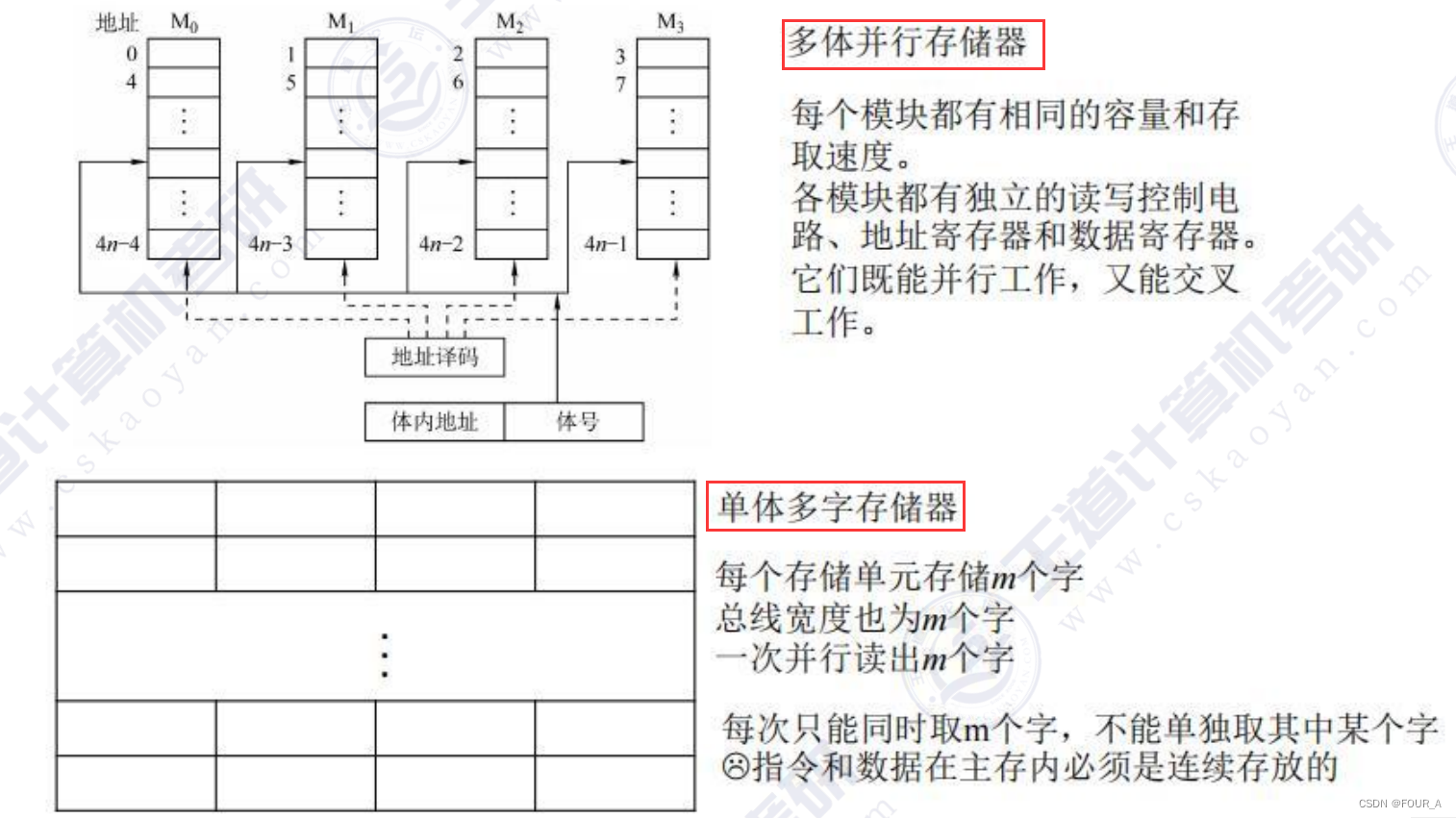

- 【※】多模块存储器

-

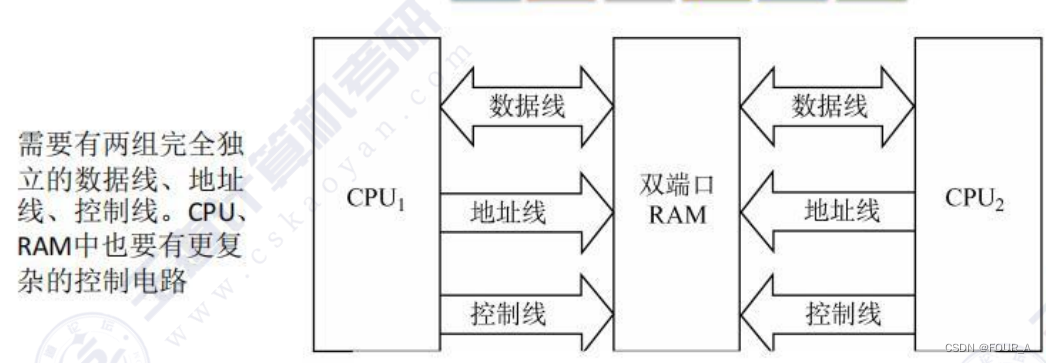

- 双端口RAM

- 多模块存储器

-

- 高位交叉编址

- 低位交叉编址

- 计算主存的带宽

-

- 微观角度:

- 宏观角度:

- 【※】磁盘存储器

-

- 磁盘的设备组成

- 磁盘的性能指标

- 磁盘地址

- 磁盘阵列RAID

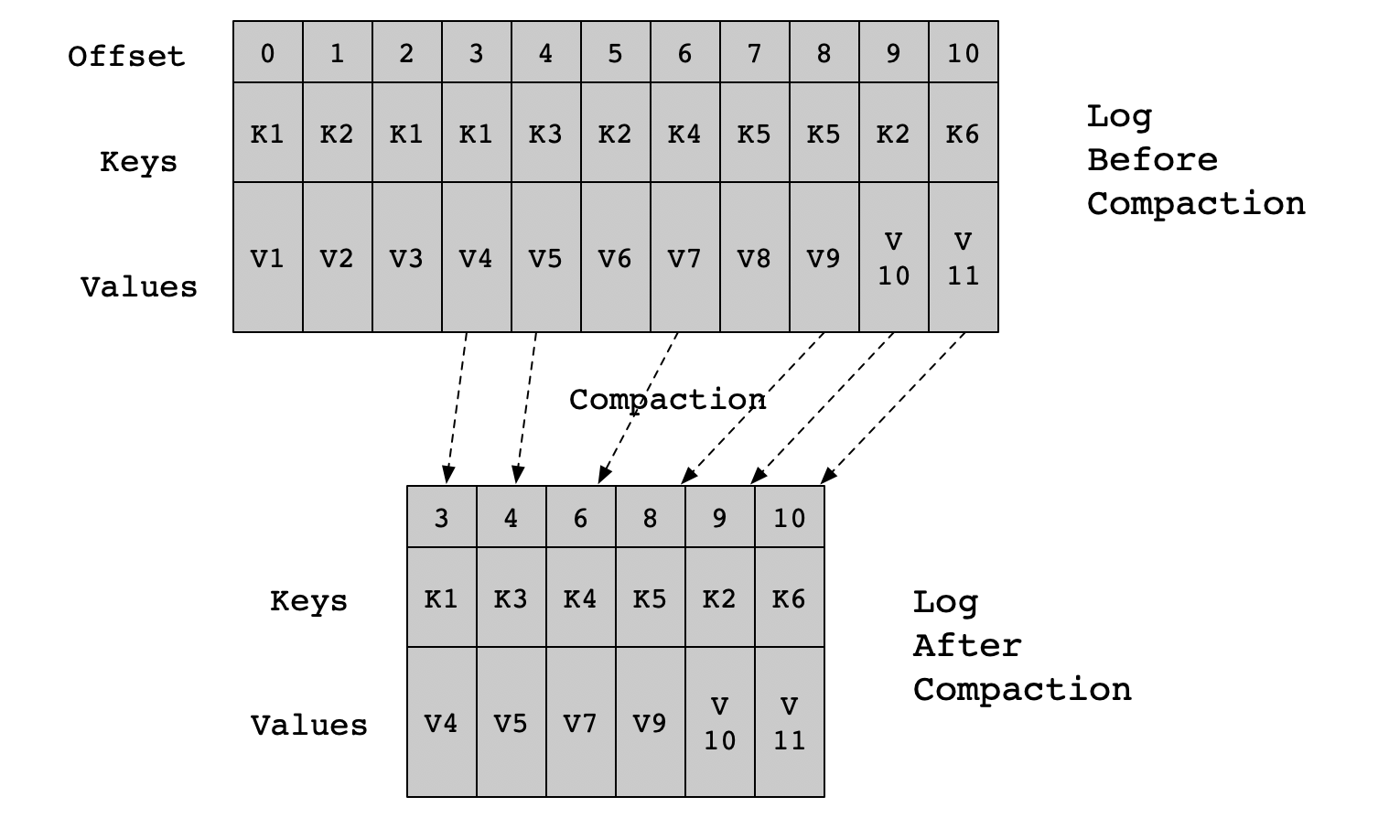

- 【※】固态硬盘SSD

-

- 原理

- 组成

- 读写性能特性

- 与机械硬盘相比的特点

- 磨损均衡技术

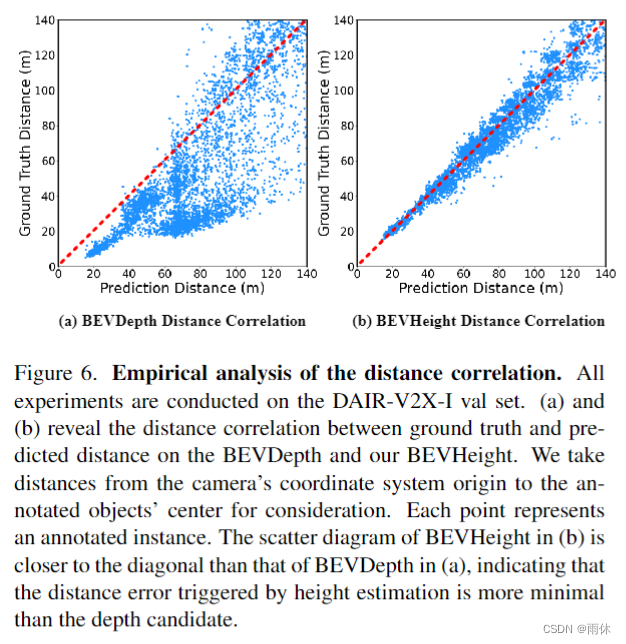

- 【※】Cache性能分析

-

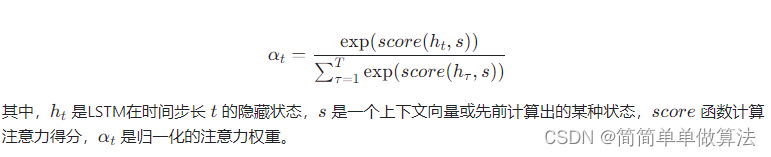

- Cahce性能分析

- 技巧【计算Cache的命中率】:

- Cache的命中率与:

- 如何区分Cache与主存的数据块对应关系?

- Cache很小,主存很大。如果 Cache 满了怎么办?

- CPU 修改了 Cache 中的数据副本,如何确保主存中数据母本的一致性?

- 【※】主存地址与Cache的映射关系、地址结构

- 【※】Cache总位数/总容量

- 存储器概述

-

- 存储器性能指标

- SRAM和DRAM的比较

- 存储器与CPU的连接

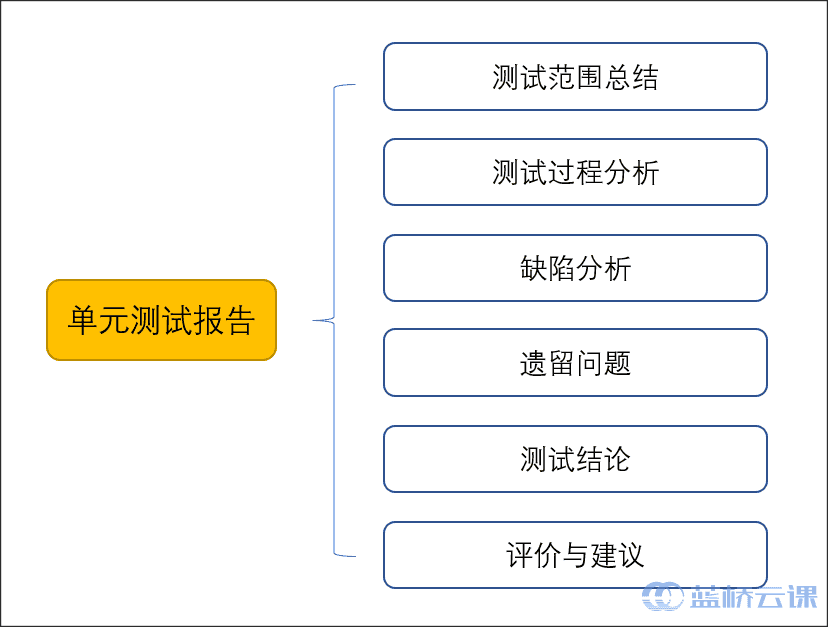

考纲

本章是重点里的重点,大题小题的考频都很高。本章常结合操作系统一起考察,是408里跨学科考察最多的一章。王道书3.1~3.4主要考小题;3.5、3.6经常考大题,要深入理解和学习。

3.1 存储系统概述

- 比较简单的一个小节,概念较多,重点记忆“存储器的性能指标”如何计算。

- 本节两个大题建议做一做,是很有代表性的考法。

3.2 主存储器

- SRAM、DRAM芯片的底层硬件原理不用过度深究,只需要了解它们之间有什么特性区别即可。王道书“3.2.1_3.DRAM芯片的读写周期” 部分过于底层,讲了电气特性,简单了解即可,计组课程里不用深究。

- 只读存储器ROM事实上已经从大纲里删除,今年大家只需要简要了解即可,不用花时间记忆。王道书里依然坚持讲ROM是因为固态硬盘SSD、Flash存储器本质上也是一种ROM,因此也决定了固态硬盘和Flash存储器“读快写慢”的重要特性。

- 要理解主存储器的基本组成,需要知道每个寄存器作用,主存内部各个基本部件之间是如何相互协调工作的,以及CPU是如何与主存交互的。

- 视频3.2.4 中介绍了双端口RAM、多模块存储器。前者(双端口RAM)已从408大纲删除,自命题考生仍需学习,408考生简单了解即可。

3.3 主存储器与CPU的连接

- 本节内容通常考察小题,目前408未出现过大题。

- 截至目前,408历年真题中还没有考过让你把主存和CPU“画图连线”的大题。通常只会在选择题中考察“字扩展、位扩展、字位扩展”相关的小题,做题难度不大。

3.4 外部存储器

- “磁盘存储器”是操作系统和计组都会讲的考点,相对来说操作系统讲的会更详细深入。因此,如果在计组这边第一次学习磁盘存储器,感觉理解不透也没关系,学完操作系统再回来看会容易很多。

- “固态硬盘”是2022年大纲新增的考点,个人认为近几年极有可能考选择题,重点注意固态硬盘的读写特性(读快写慢、随机读写、写前需擦除、擦除寿命有限)以及负载均衡技术。大家只要能理解课件内那张思维导图,做选择题一定没问题。

3.5 高速缓冲存储器

- 大题高频考点,常与操作系统第三章结合考察,综合性较高,但大题题型套路相对固定。

- 强化阶段会用一个例子帮助大家串联操作系统第三章与Cache的相关知识。

- 适合在第一轮做的大题已在学习进度打卡表中说明,未写进打卡表的题目中含有后序章节内容,不建议在第一轮做。

3.6 虚拟存储器

- 本节内容和操作系统第三章高度重合。计组这边建议先快速看看书,有个大概的了解即可,等学完操作系统第三章,第二轮复习时再回来仔细研究。

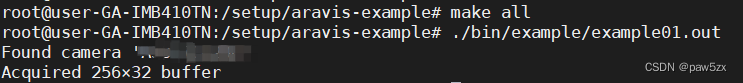

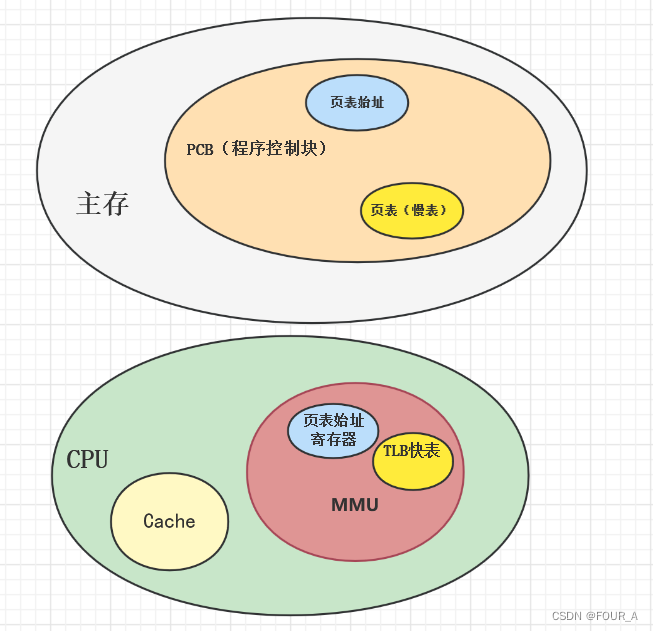

【※】存储系统总体流程图

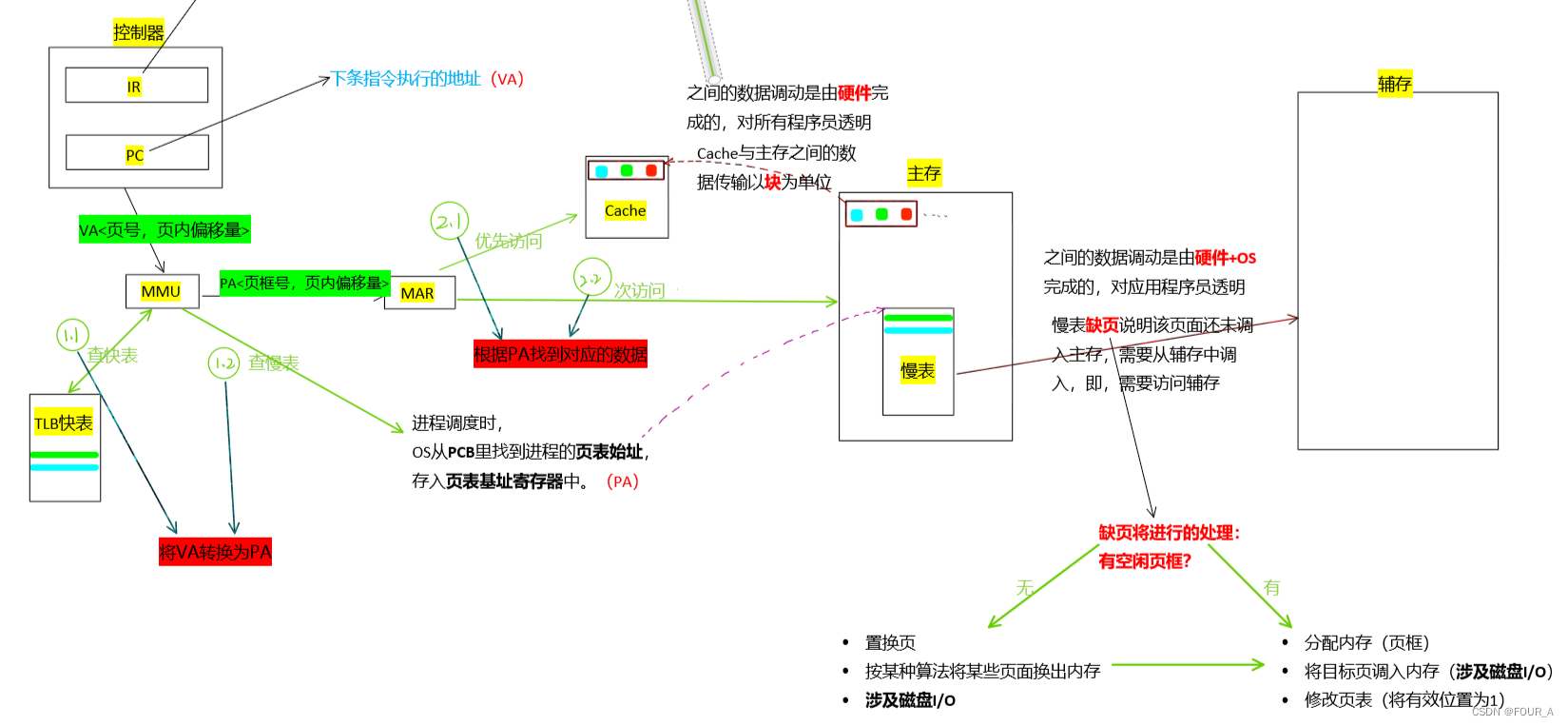

【※】各个部件的存储位置

计算机存储相关硬件与数据结构说明

进程控制块(PCB)

- 存放在主存的系统区(内核区)中,是一个数据结构,用于存储进程的各种信息。

页表

- 存放在 PCB 中,用于描述每个进程的虚拟空间与物理内存的映射关系。每个进程的低地址部分或高地址部分可能映射到同一片内核空间。

页表始址

- 存放在 PCB 中的 unsigned int 变量,指示页表的起始地址。

页表始址寄存器(PTR)

- 存放在 MMU 中,系统运行进程前(切换进程)CPU 将会把页表始址复制到页表始址寄存器中,每个进程的页表始址不同。

MMU(内存管理单元)

- 集成在 CPU 中,负责虚拟地址到物理地址的转换。

TLB(Translation Lookaside Buffer,快表)

- 高速存储器,通常由相联存储器或 SRAM 组成,包含于 MMU 中,属于 CPU。存放当前进程的页表项的副本数据,用于加速地址转换。

- 缺失处理由硬件自动实现。

Cache

- 高速存储器,由 SRAM 组成,包含于 CPU,但不属于 MMU 的一部分。

- 切换进程时,Cache 进程不作废,不同进程可能共享同一页框。

- 缺失处理由硬件自动实现。

PS:

- TLB 和 Cache 在底层硬件原理上相同(SRAM),但作用不同。

- TLB(快表)存放着当前进程的页表项的副本数据,用于加速地址转换。

- Cache 存放着内存块的副本数据,用于加速数据访问。

• 在进程被调度,开始运行之前,CPU 会将其页表始址存放到页表始址寄存器中,每切换一个进程,页表始址寄存器内容改变,也就是切换了一张页表。

• 若新进程上处理机运行时,TLB 的副本数据则全部作废,有效位全部变成 0。而 Cache 中的内容不需要全部作废。当刚开始运行新进程时,会经常发生 Cache 未命中的情况。

即:当 A 进程切换到 B 进程时:

① 页表始址寄存器更新

② TLB 副本数据全部作废,Cache 不需要全部作废

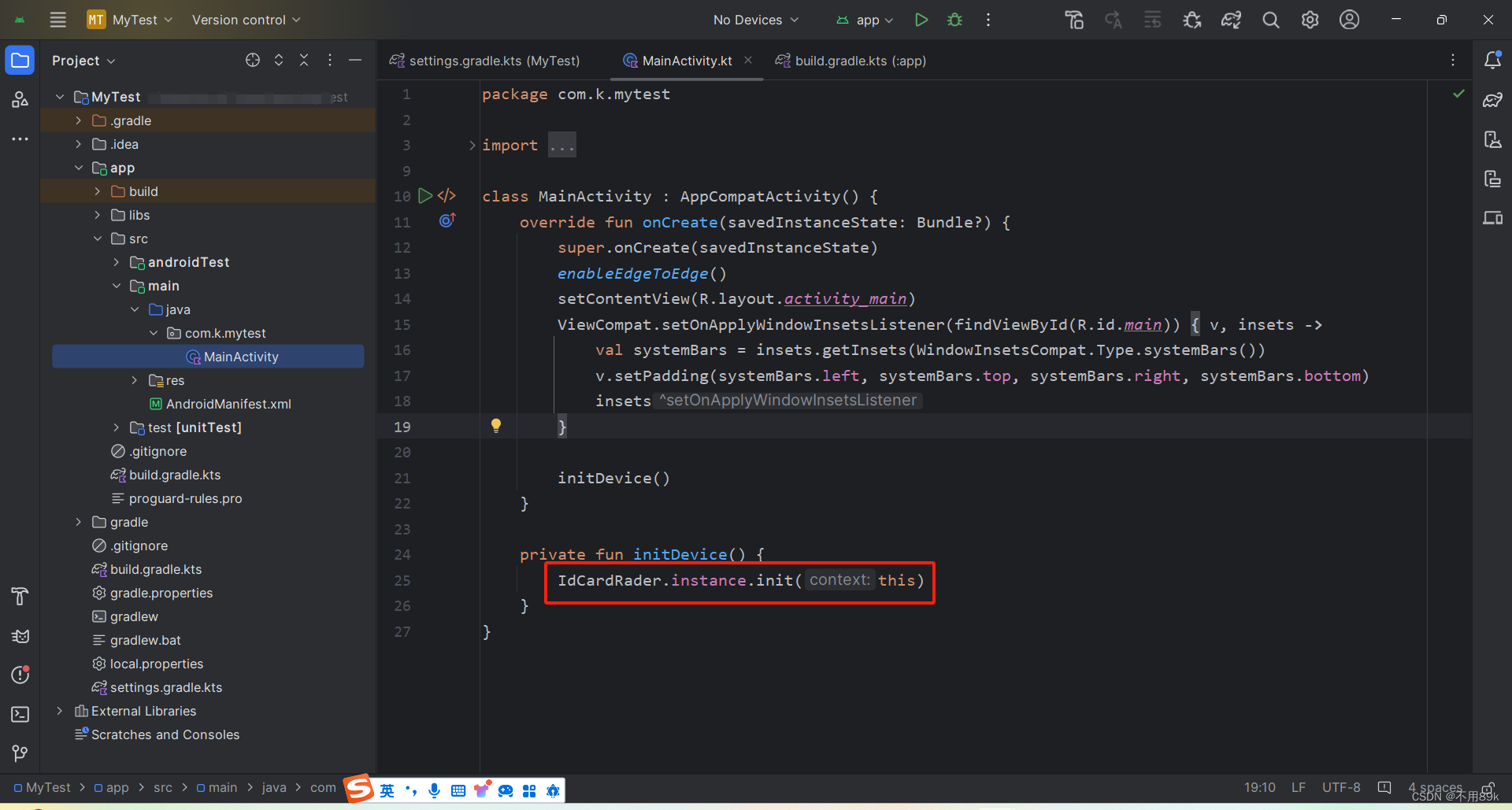

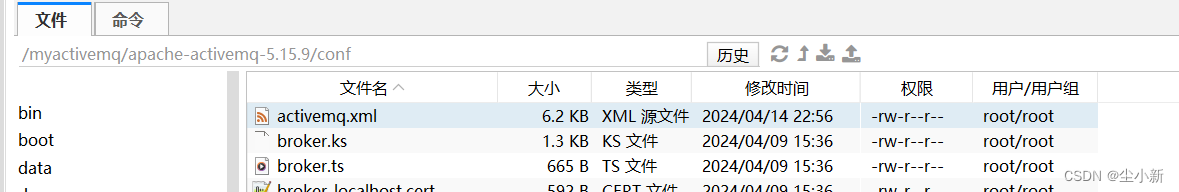

【※】DRAM芯片计算引脚的数目

• ABC 位:行数=A,列数=B,一个超元=C 位。

• 访问内存时,DRAM 芯片的读取过程:

- 从地址线获取内存地址,进行行、列译码。

- 先行:将对应行的整行数据放入行缓冲中。行缓冲是一整行的超元。

- 后列:将行缓冲中对应的超元读到数据线。

计算芯片引脚的数目

【※】多模块存储器

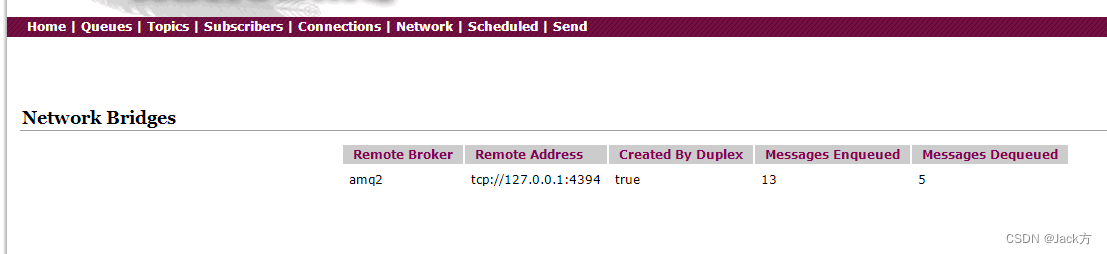

双端口RAM

- 支持两个 CPU 同时访问 RAM。

- 可同时读/写不同的存储单元。

- 可同时读同一个存储单元。

- 不能同时写(或者一读一写)同一个单元。

- 若发生“冲突”,则发出“BUSY”信号,其中一个 CPU 的访问端口暂时关闭。

多模块存储器

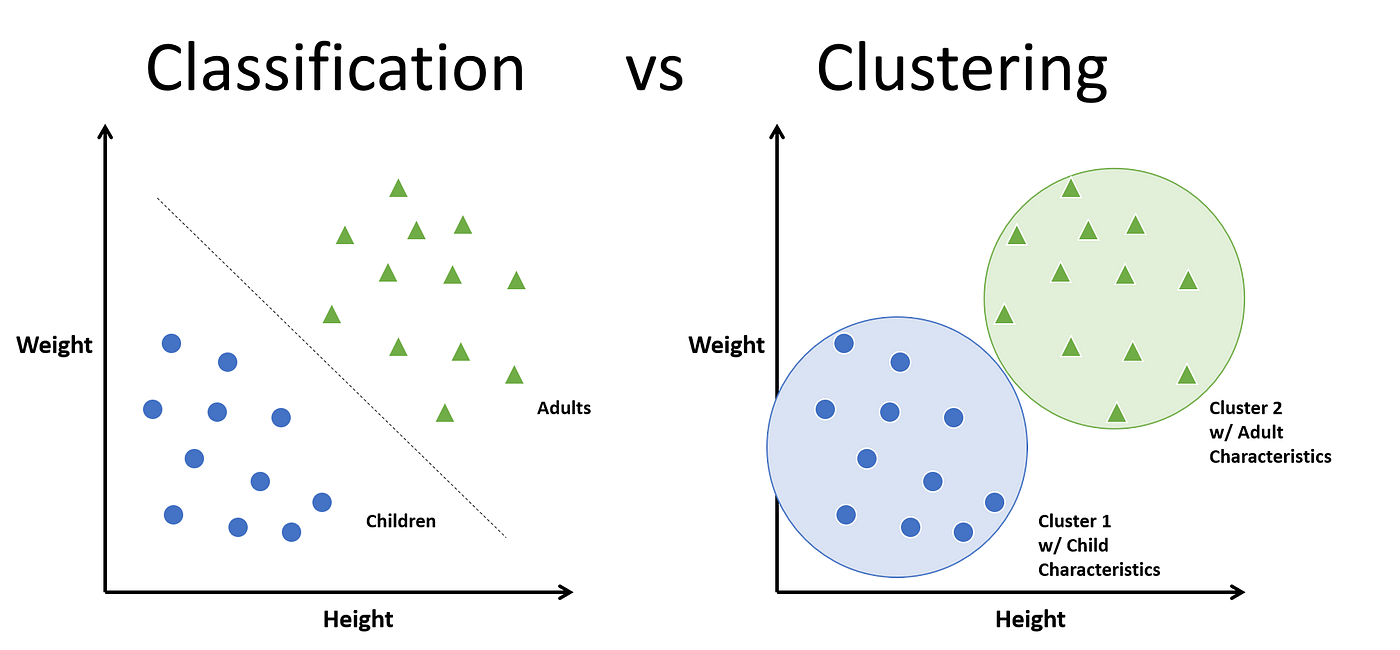

高位交叉编址

- 理论上多个存储体可以被并行访问,但是由于通常会连续访问,因此实际效果相当于单纯的扩容。

低位交叉编址

- 每个存储周期内可读写地址连续的 m 个存储字。

- 每个体的存储字 = 总线的宽度。

- 微观上,m 个模块被串行访问;

- 宏观上,每个存取周期内所有模块被并行访问。

- 连续取 n 个存储字耗时: T + ( n − 1 ) r 。 T + (n−1)r。 T+(n−1)<