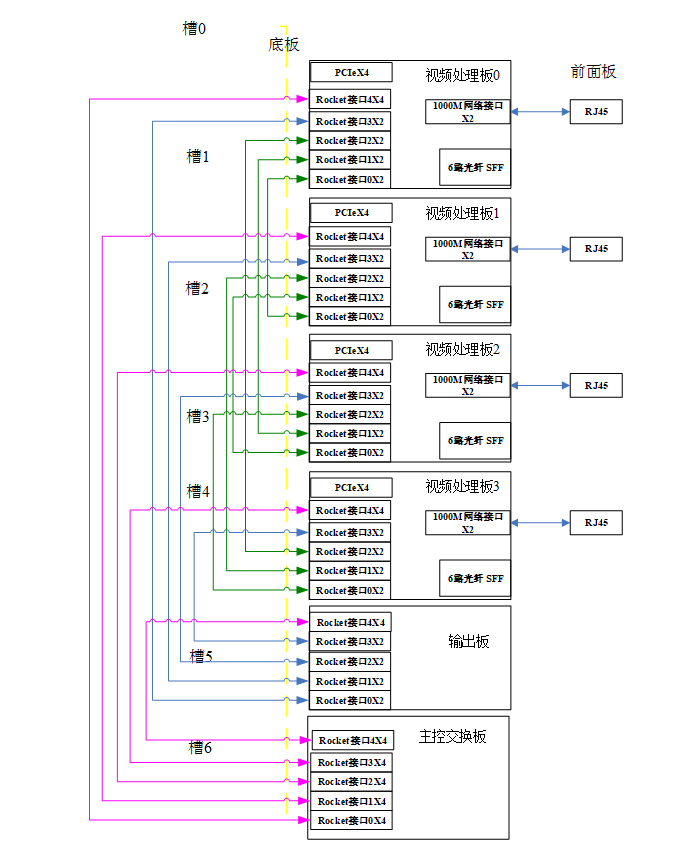

基于6U CPCIe的双路光纤图像DSP实时计算平台 | |

|

DSP实时计算平台设计方案:912-基于6U CPCIe的双路光纤图像DSP实时计算平台

news2026/2/14 20:27:52

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如若转载,请注明出处:http://www.coloradmin.cn/o/1572113.html

如若内容造成侵权/违法违规/事实不符,请联系多彩编程网进行投诉反馈,一经查实,立即删除!相关文章

11 - 三八译码器和存储器组织

---- 整理自B站UP主 踌躇月光 的视频 1. 38译码器

1.1 真值表

A2A1A0O7O6O5O4O3O2O1O00000000000100100000010010000001000110000100010000010000101001000001100100000011110000000 O 0 A 2 ‾ A 1 ‾ A 0 ‾ O 1 A 2 ‾ A 1 ‾ A 0 O 2 A 2 ‾ A 1 A 0 ‾ O 3 A 2 ‾ A…

c语言--枚举类型(声明、使用、优点)

目录 一、枚举类型的声明二、 枚举类型的优点三、 枚举类型的使用 一、枚举类型的声明

枚举顾名思义就是一一列举。 把可能的取值⼀⼀列举。 比如我们现实生活中: ⼀周的星期⼀到星期日是有限的7天,可以⼀⼀列举 性别有:男、女、保密&#x…

vscode 连接远程服务器 服务器无法上网 离线配置 .vscode-server

离线配置 vscode 连接远程服务器 .vscode-server

1. .vscode-server下载

使用vscode连接远程服务器时会自动下载配置.vscode-server文件夹,如果远程服务器无法联网,则需要手动下载 1)网址:https://update.code.visualstudio.com…

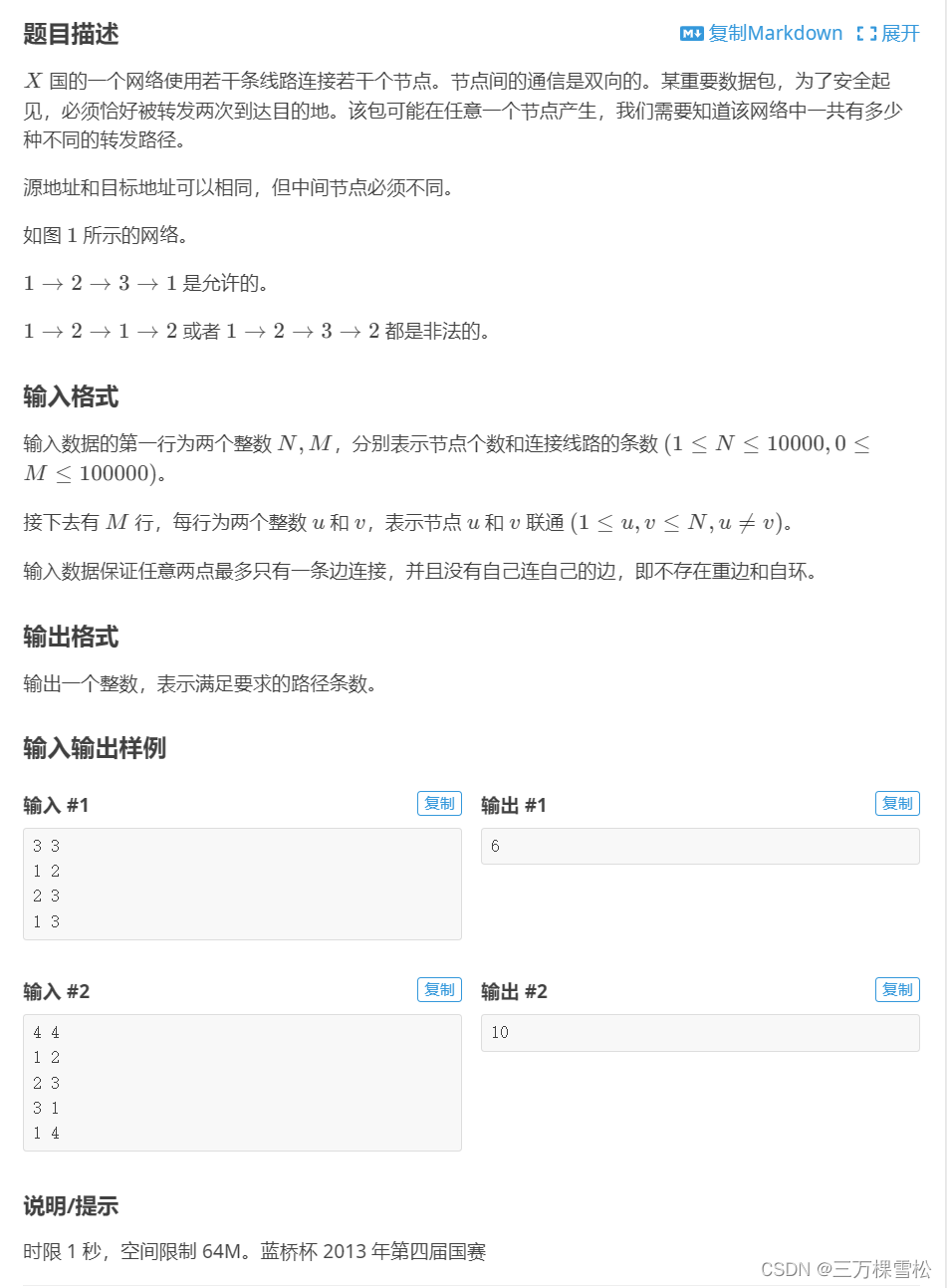

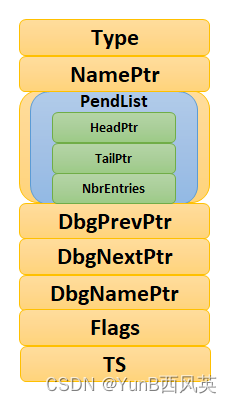

【蓝桥杯-单链表-网络寻路】

蓝桥杯-单链表-网络寻路 单链表基本操作操作一:向链表头插入一个数操作二:在第 k个插入的数后插入一个数操作三:删除第 k个插入的数后面的一个数; P8605 [蓝桥杯 2013 国 AC] 网络寻路 单链表基本操作

初始化有关操作

// head 表示头结点的…

Spring Boot 接入 Redis

Spring Boot 接入 Redis 简介

Redis 是一种访问速度非常快的内存数据结构存储,用作数据库、缓存、消息代理和流引擎。提供 strings、hashes、lists、sets 等数据结构。可以解决会话缓存、消息队列、分布式锁、定期将数据集存储到硬盘等功能。

通过 Redis 设计实现…

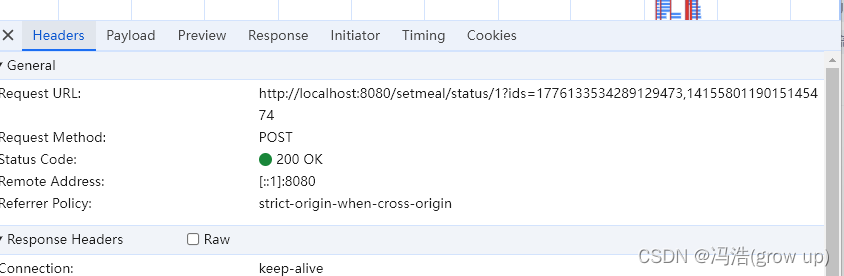

瑞吉外卖实战学习--15、批量启售和批量禁售

批量启售和批量禁售 前言代码实现 前言 代码实现

通过url我们可以获取到传过来的ids和状态值,现根据状态值查询出来相关数据然后直接附加状态值最后通过updateBatchById来进行修改 PostMapping("/status/{status}")public R<String> updateStatus(…

电子台账:用控件颜色提高工作效率和数据质量

目录

1 前言

2 用页签颜色表示月度数据锁定状态

3 模板制作中定位数据源表格及其行列

3.1 鼠标移过水平过滤模板

3.2 鼠标移过垂直过滤模板

4 数据抓取过程对账页和源单元格同时染色

5 数据溯源过程,对企业数据源单元格染色

6 用键盘进行数据编辑后 1 前言 …

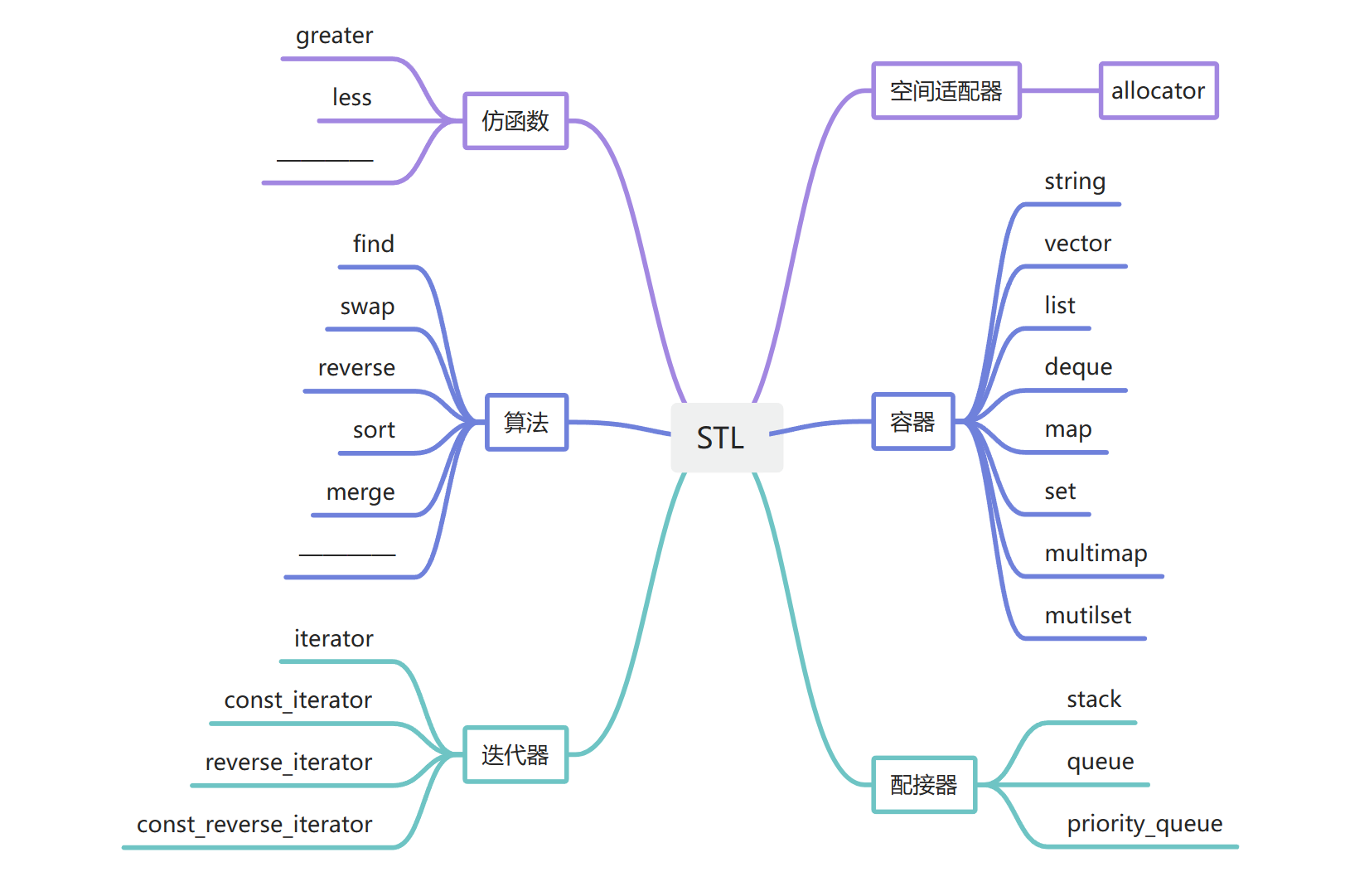

【c++】初阶模版与STL简单介绍

🔥个人主页:Quitecoder

🔥专栏:c笔记仓 朋友们大家好,本篇文章介绍一下模版和对STL进行简单的介绍,后续我们进入对STL的学习! 目录 模版1.泛型编程2.函数模板2.1函数模板的原理2.2模版的实例化…

(学习日记)2024.04.08:UCOSIII第三十六节:事件

写在前面: 由于时间的不足与学习的碎片化,写博客变得有些奢侈。 但是对于记录学习(忘了以后能快速复习)的渴望一天天变得强烈。 既然如此 不如以天为单位,以时间为顺序,仅仅将博客当做一个知识学习的目录&a…

【JavaSE】接口 详解(上)

前言 本篇会讲到Java中接口内容,概念和注意点可能比较多,需要耐心多看几遍,我尽可能的使用经典的例子帮助大家理解~ 欢迎关注个人主页:逸狼 创造不易,可以点点赞吗~ 如有错误,欢迎指出~ 目录 前言 接口 语法…

YoloV8改进策略:BiFPN+小目标分支实现小目标检测精度的大幅度上升

摘要

这几天有粉丝提到了BiFPN解决小目标问题,我结合我的经验,将BiFPN和小目标分支结合实现小目标任务检测精度的上升。

BiFPN

论文:https://arxiv.org/pdf/1911.09070v2.pdf

BiFPN,全称Bi-directional Feature Pyramid Netwo…

leetcode.24. 两两交换链表中的节点

题目

给定一个链表,两两交换其中相邻的节点,并返回交换后的链表。

你不能只是单纯的改变节点内部的值,而是需要实际的进行节点交换。

思路

创建虚拟头节点,画图,确认步骤。

实现

/*** Definition for singly-li…

阿德勒、荣格、埃里克森、霍妮、弗洛姆、沙利文的新精神分析理论

新精神分析理论,强调自我的自主性及其整合与调节功能,强调文化和社会因素对人格的重大影响。

一、阿德勒的个体心理学

阿德勒,是一个男人努力克服自卑感的优秀样板。阿德勒写了《超越与自卑》。

阿德勒,向意识层面扩展精神分析…

SpringBoot快速入门笔记(4)

文章目录 一、Vue框架1、前端环境准备2、简介3、快速开始4、事件绑定 二、Vue组件化开发1、NPM2、Vue Cli3、组件化开发4、SayHello自定义组件5、Movie自定义组件 一、Vue框架

1、前端环境准备 编码工具:VSCode 依赖管理:NPM 项目构建:VueCl…

【Mathematical Model】基于Python实现随机森林回归算法特征重要性评估线性拟合

前段时间在做遥感的定量反演,所以研究了一下回归算法,由于之前发的几篇博文都是定义好基础方程进行拟合的,不太满足我的需求。所以研究了一下随机森林回归的算法,之前使用随机森林都是做分类,这次做了回归算法也算是补…

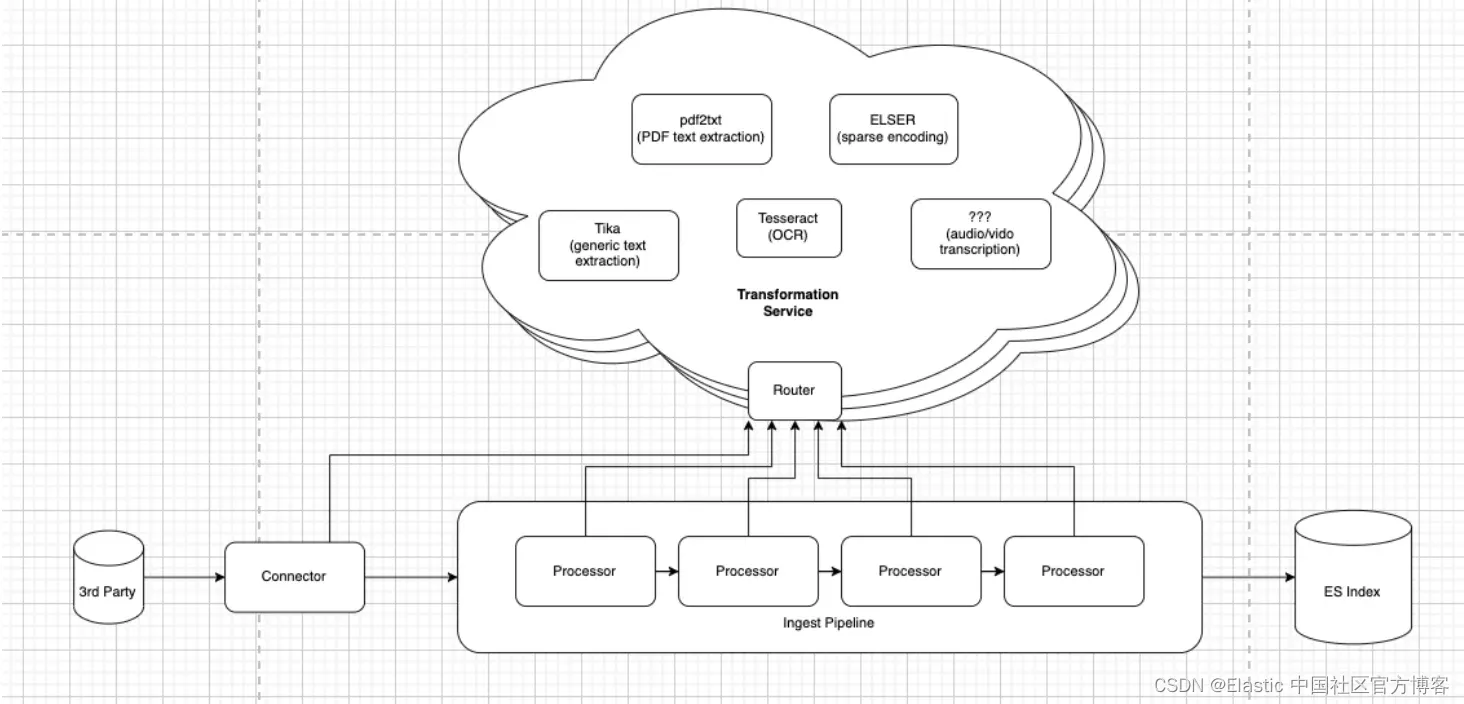

Elasticsearch:我们如何演化处理二进制文档格式

作者:来自 Elastic Sean Story

从二进制文件中提取内容是一个常见的用例。一些 PDF 文件可能非常庞大 — 考虑到几 GB 甚至更多。Elastic 在处理此类文档方面已经取得了长足的进步,今天,我们很高兴地介绍我们的新工具 —— 数据提取服务&…

java-权限修饰符、代码块

一、权限修饰符概念

权限修饰符是用来控制一个成员被访问的范围,可以用来修饰成员变量、方法、构造方法、内部类 二、权限修饰符的分类 举例:

1、private 2、空着不写 3、protected 4、public 三、权限修饰符的使用规则

实际开发中,一般使…

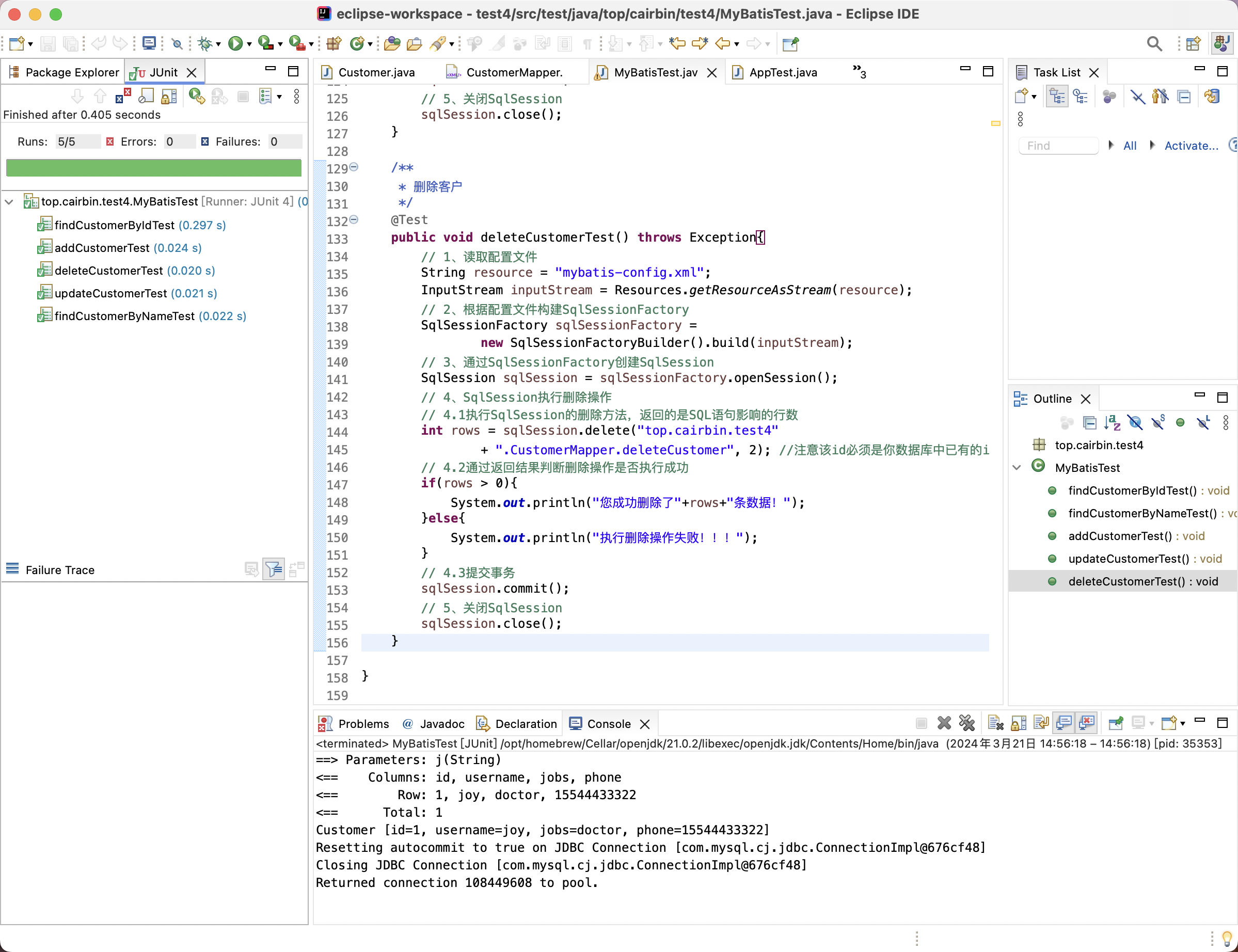

SSM框架学习——了解MyBatis

了解MyBatis

什么是MyBatis

MyBatis 是一款优秀的持久层框架,它支持自定义 SQL、存储过程以及高级映射。MyBatis 免除了几乎所有的 JDBC 代码以及设置参数和获取结果集的工作。MyBatis 可以通过简单的 XML 或注解来配置和映射原始类型、接口和 Java POJOÿ…

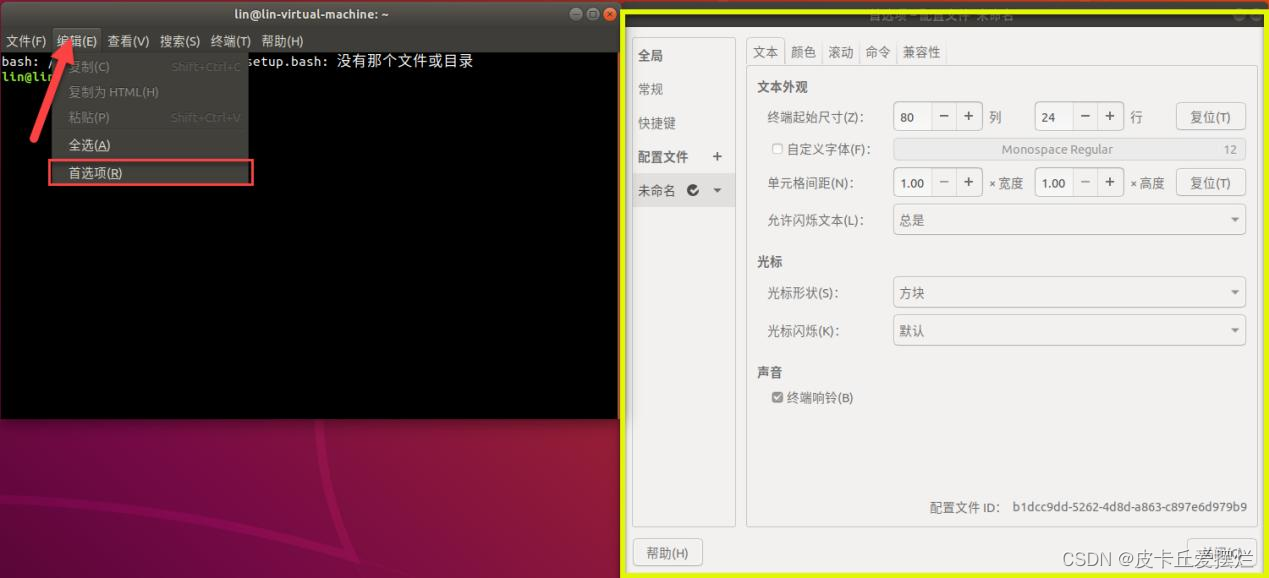

Linux第4课 Linux的基本操作

文章目录 Linux第4课 Linux的基本操作一、图形界面介绍二、终端界面介绍 Linux第4课 Linux的基本操作

一、图形界面介绍

本节以Ubuntu系统的GUI为例进行说明,Linux其他版本可自行网搜。 图形系统进入后,左侧黄框内为菜单栏,右侧为桌面&…

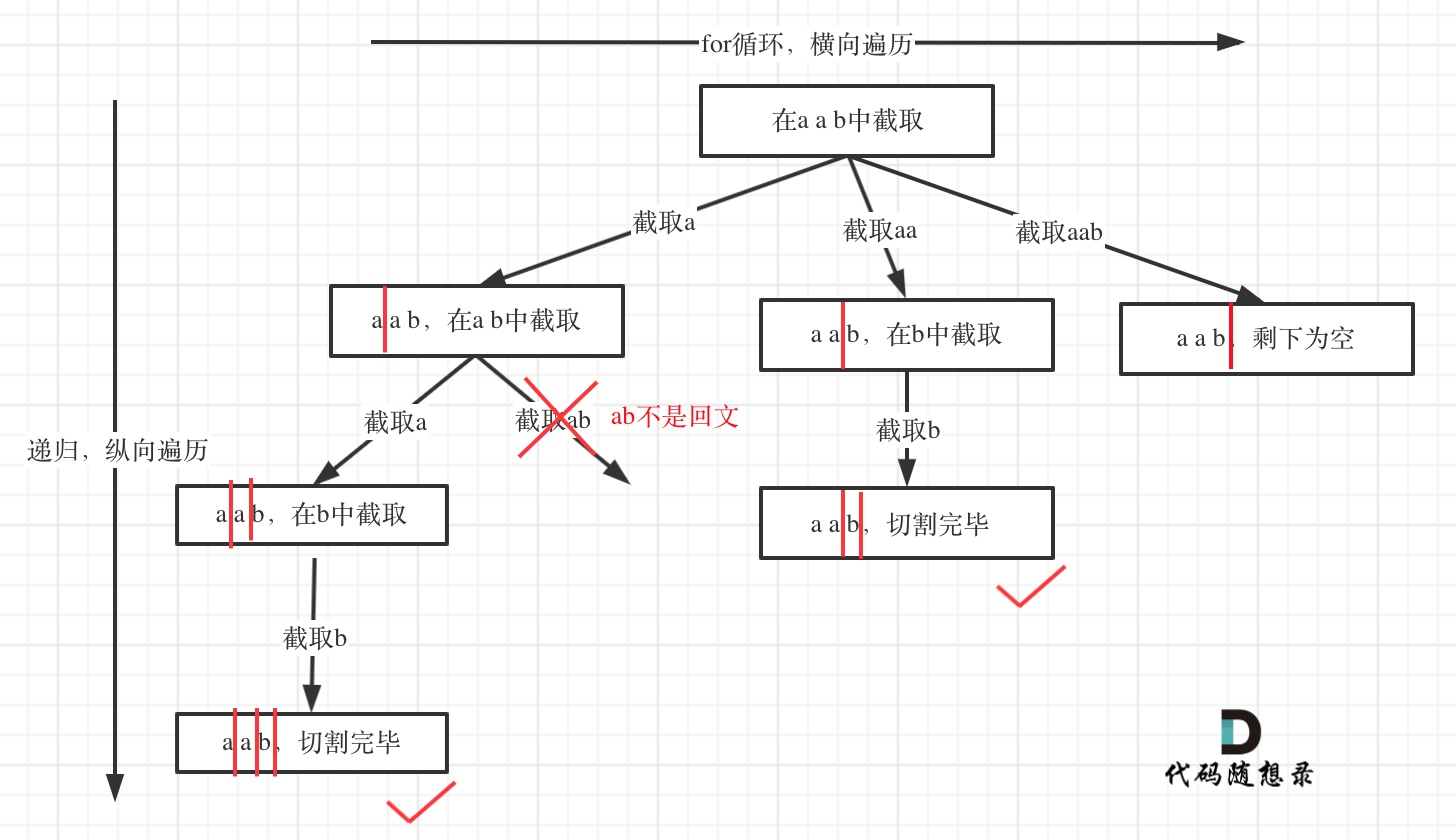

LeetCode-131. 分割回文串【字符串 动态规划 回溯】

LeetCode-131. 分割回文串【字符串 动态规划 回溯】 题目描述:解题思路一:回溯, 回溯三部曲解题思路二:0解题思路三:0 题目描述:

给你一个字符串 s,请你将 s 分割成一些子串,使每个…