无人问津也好,技不如人也罢,都应静下心来,去做该做的事。

最近在学STM32,所以也开贴记录一下主要内容,省的过目即忘。视频教程为江科大(改名江协科技),网站jiangxiekeji.com

在STM32中,集成了很多用于通信的外设模块,USART、I2C、SPI、CAN和USB,C8T6芯片是全部都支持的。

本期学习USART串口外设。

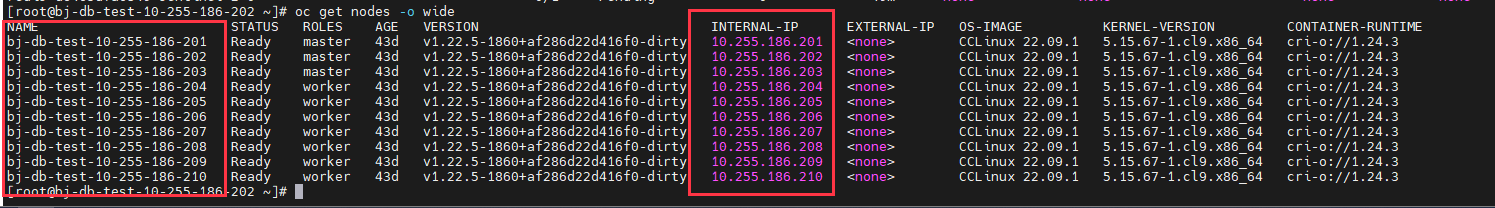

USART简介

一般我们串口很少使用这个同步功能,所以USART和UART使用起来,也没有什么区别。USRT它只支持时钟输出,不支持时钟输入,所以这个同步模式更多是为了兼容别的协议或者特殊用途而设计的,并不支持两个USRT之间进行同步通信,所以我们学习串口,主要还是异步通信。

USART大体可分为发送和接收两部分,发送部分就是将数据寄存器的一个字节数据,自动转换为协议规定的波形,从TX引脚发送出去;接收部分就是,自动接收RX引脚的波形,按照协议规定,解码为一个字节数据,存放在数据寄存器里。这就是USART电路的功能。

当我们配置好了USART电路,直接读写数据寄存器,就能自动发送和接收数据了。

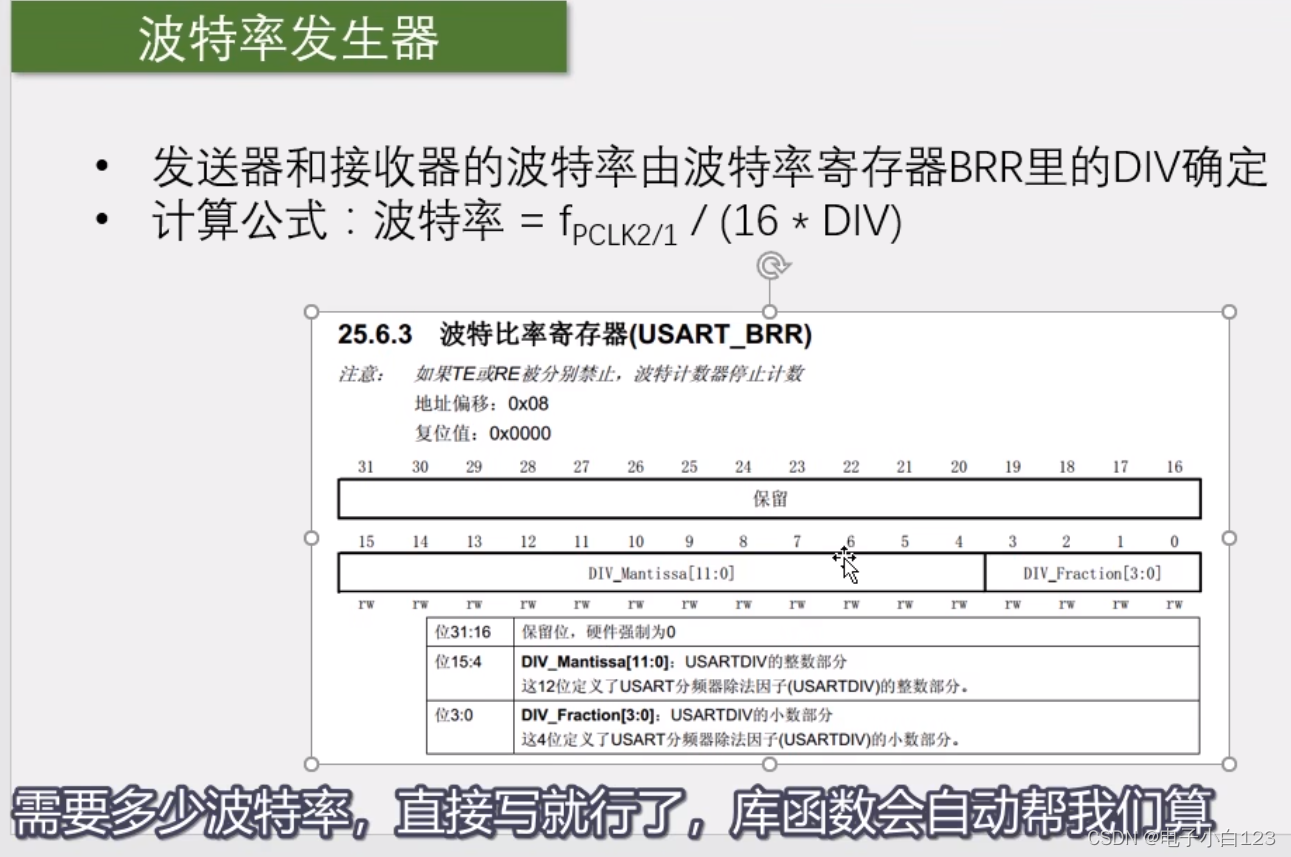

波特率发生器,就是用来配置波特率的,它其实就是一个分频器,比如我们APB2总线给个72MHz的频率,然后波特率发生器进行一个分频,得到我们想要的波特率时钟。最后在这个时钟下,进行收发,就是我们指定的通信波特率。

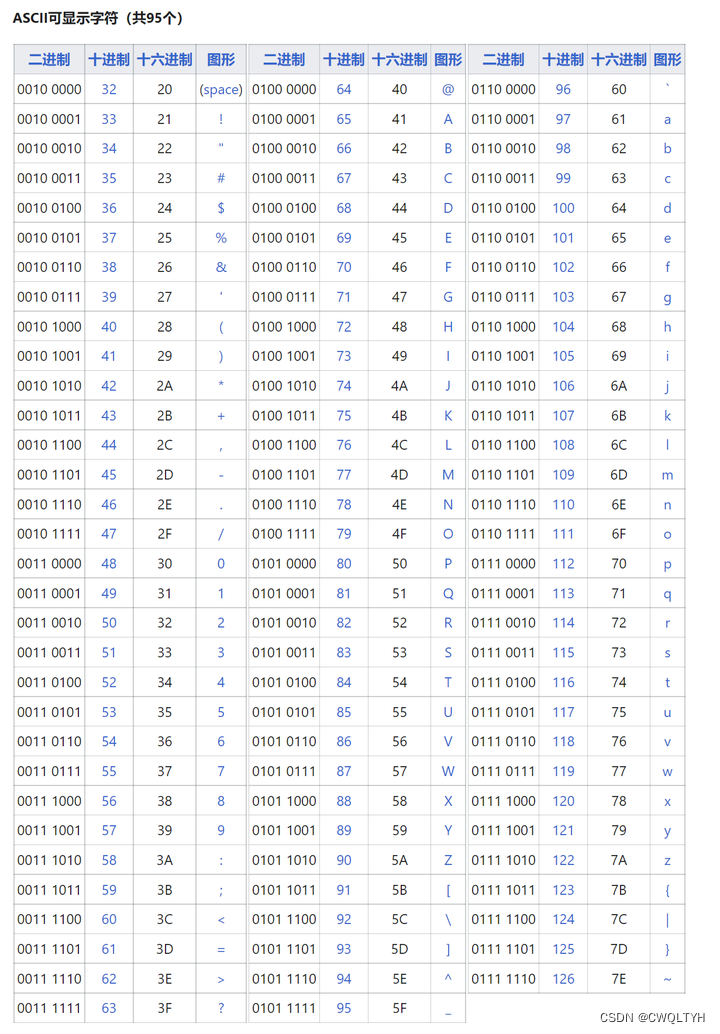

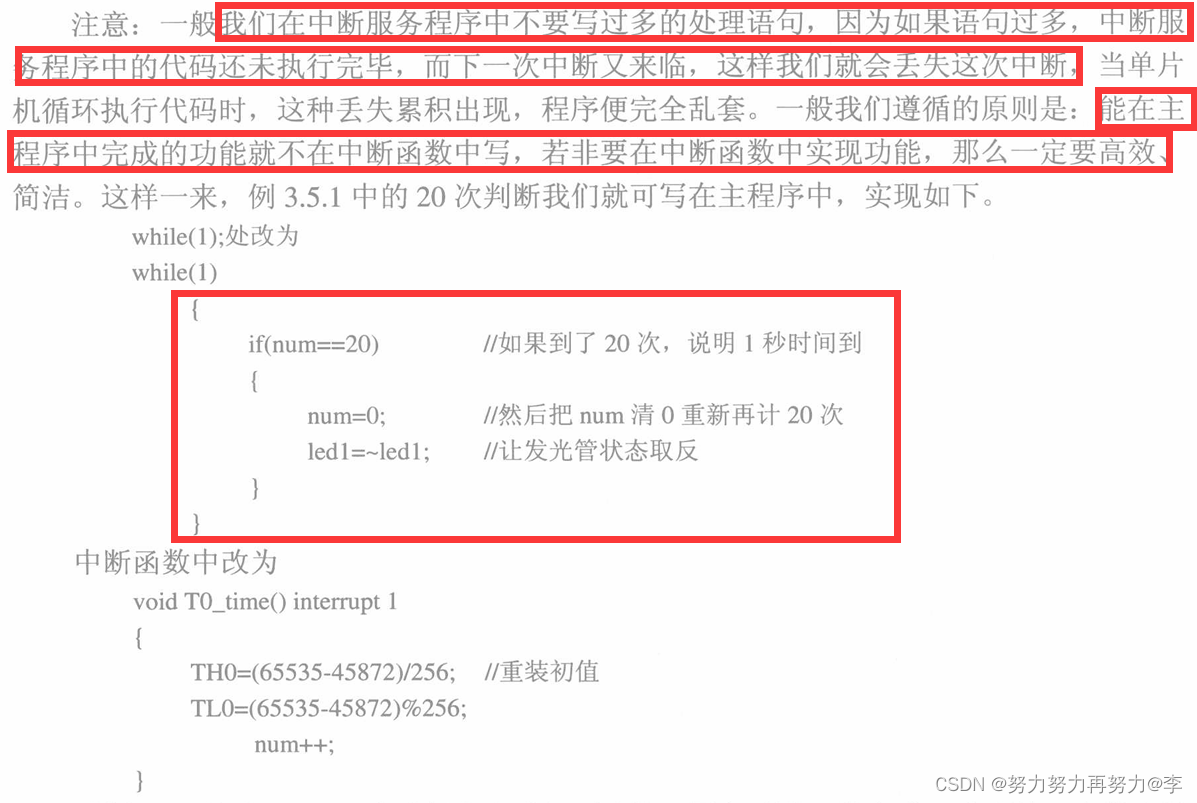

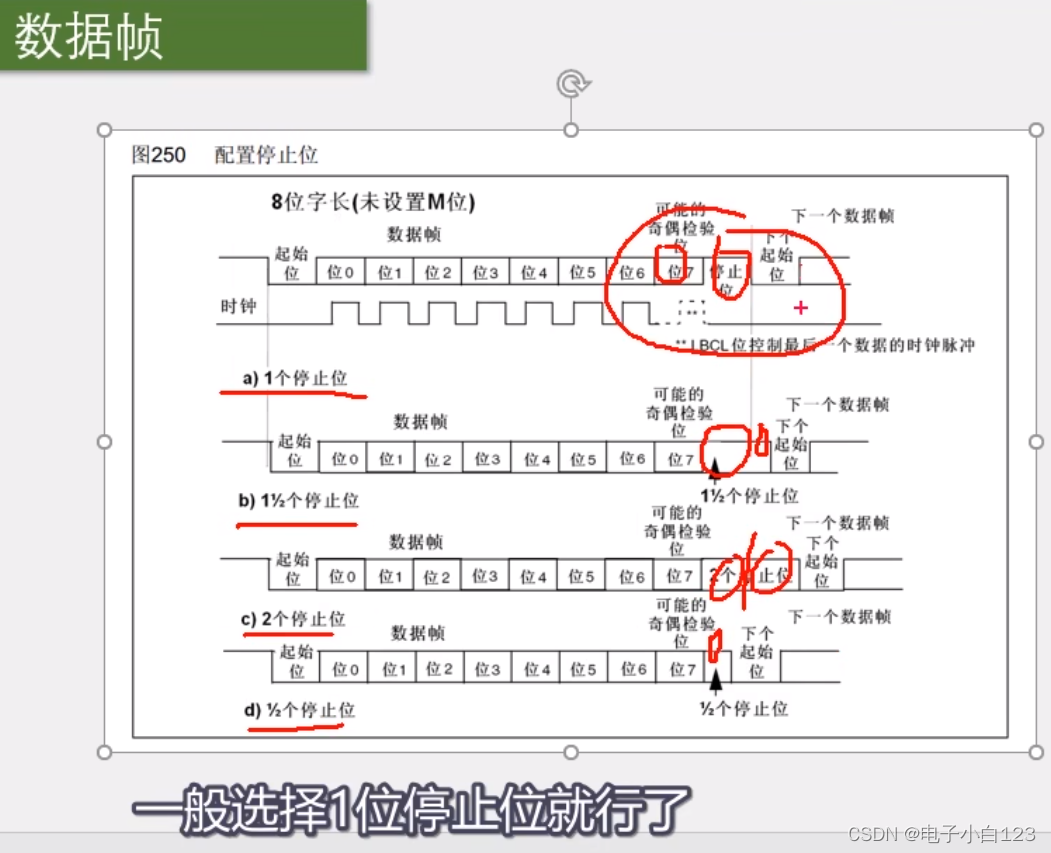

数据位一般不需要校验就选8位,需要校验就选9位;我们最常用的就是1位停止位,其他的很少用;常用无校验位。

硬件流控制是,比如A设备有个TX向B设备的RX发送数据,A设备一直在发,发的太快了,B处理不过来,如果没有硬件流控制,那B就只能抛弃新数据或者覆盖原数据了。如果有硬件流控制,

在硬件电路上,会多出一根线。如果B没准备好接收,就置高电平,如果准备好了,就置低电平。A接收到了B反馈的准备信号,就只会在B准备好的时候,才发数据,如果B没准备好,那数据就不会发送出去。这就是硬件流控制,可以防止因为B处理慢而导致数据丢失的问题。硬件流控制,STM32也是有的,不过我们一般不用。

串口支持DMA,如果由大量数据收发,可以使用DMA转运数据,减轻CPU的负担。

STM32F103C8T6有三个串口。其中这里USART1是APB2总线上的设备,USART2、3是APB1的设备。

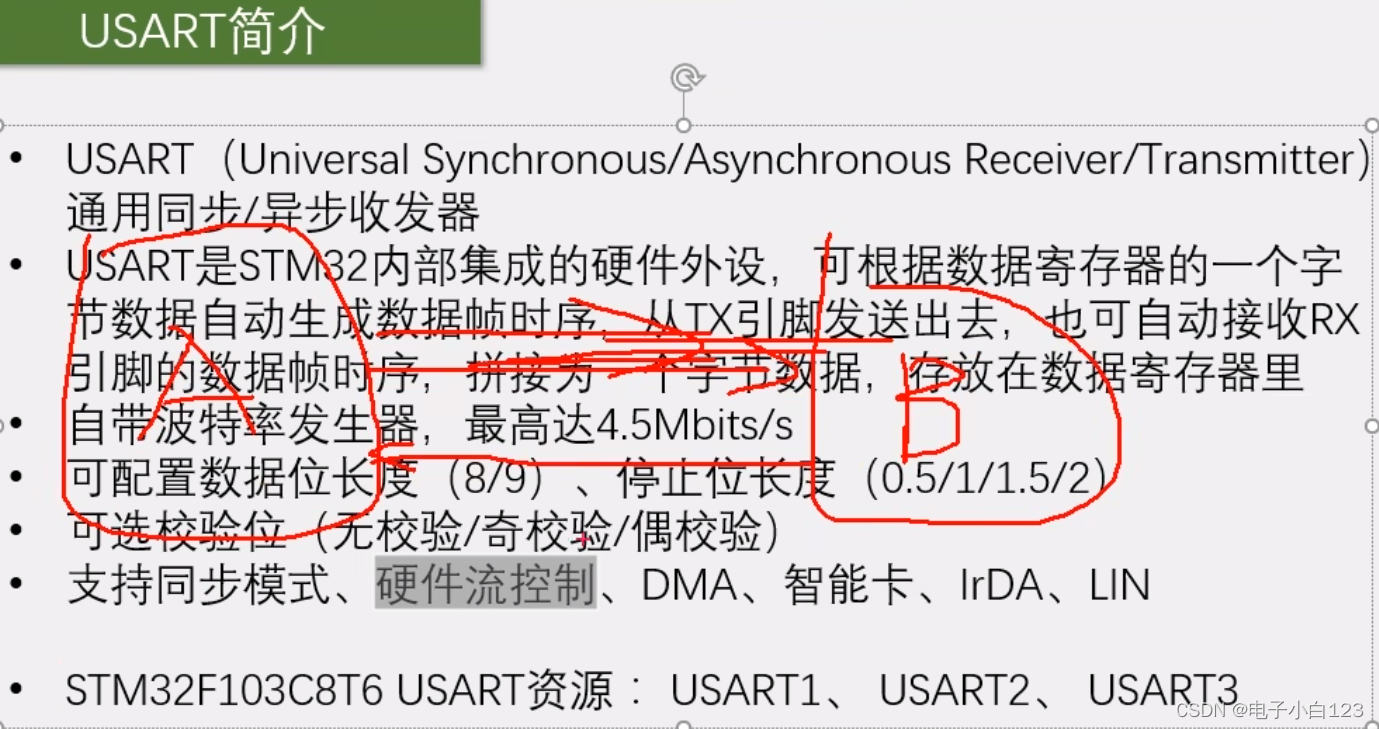

USART框图

左上这里的SW_RX、RDA_OUT/IN这些是智能卡和IrDA通信的引脚,不用管这三个。

引脚这块,TX发送脚就是从发送移位寄存器这里接出去;RX接收脚,就是通向接收移位寄存器这里,这样就行了。

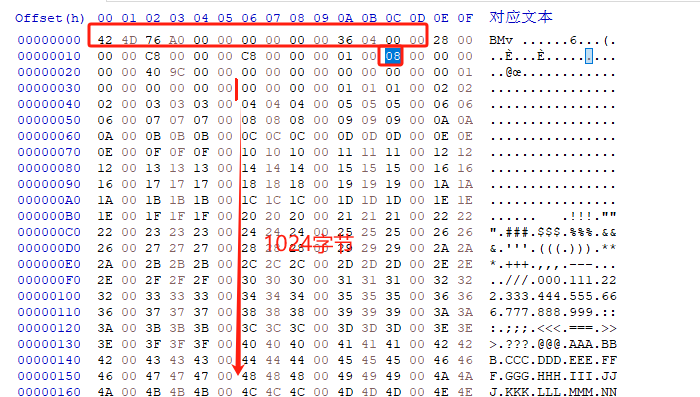

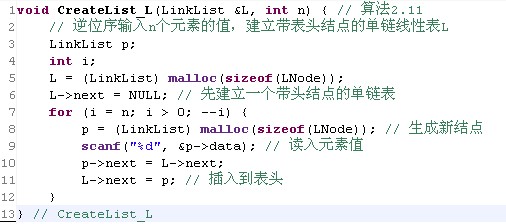

右上这部分就是串口的数据寄存器了 ,发送或接收的字节数据就存在这里。有两个数据寄存器,一个是发送数据寄存器TDR(Transmit DR)、一个是接收数据寄存器RDR(Receive DR),这两个寄存器占用同一个地址。在程序上,只表现为一个寄存器,就是数据寄存器DR(Data Register)。但实际硬件中,是分成了两个寄存器。TDR是只写的,RDR是只读的。当你进行写操作时,数据就写入到TDR,当你进行读操作时,数据就是从RDR读出来的。

然后往下看,下面是两个移位寄存器,一个用于发送,一个用于接收。发送移位寄存器的作用就是,把一个字节的数据一位一位地移出去,正好对应串口协议的波形的数据位。比如你在某时刻给TDR写入了0x55这个数据,在寄存器里就是二进制存储,0101 0101,那么此时,硬件检测到你写入数据了。它就会检查,当前移位寄存器是不是有数据正在移位,如果没有,这个01010101就会立刻全部移动到发送移位寄存器,准备发送。当数据从TDR移动到移位寄存器时,会置一个标志位,叫TXE(TX Empty),发送寄存器空,我们检查这个标志位,如果置1了,我们就可以在TDR写入下一个数据了。注意下,当TXE标志位置1时,数据还没发出去,只是数据从TDR转移到发送移位寄存器了,这时我们就可以往TDR写入新数据了。这里发送移位寄存器是向右移位的,所以正好和串口协议规定的低位先行,是一致的。如果当前移位寄存器移位还没有完成,TDR的数据就会进行等待,一但移位完成,就会立刻转移过来。接收端这边,也是类似的,当我们检测到RXNE置1之后,就可以把数据读走了。

当然发送还需要加上帧头帧尾,接收还需要剔除帧头帧尾,这些操作,它内部有电路会自动执行,我们知道会有硬件电路帮我们做就好了。

硬件流控制,简称流控。这里流控有两个脚,一是nRTS、二是nCTS。nRTS(Request To Send)是请求发送,是输出脚,也就是告诉别人,我当前能不能接收;nCTS(Clear To Send)是清除发送,是输入脚,也就是用于接收别人nRTS的信号的。这里前面加个n的意思是低电平有效。

接着看下面的中断输出控制 ,中断申请位,就是状态寄存器这里的各种标志位,有两个标志位比较重要。一个是TXE发送寄存器空,另一个是RXNE接收寄存器非空,这两个是判断发送状态和接收状态的必要标志位。中断控制这里就是配置中断是不是能通向NVIC,这个应该好理解。

USART1挂载在APB2,所以就是PCLK2的时钟,一般是72M;其他的USART都挂载在APB1,所以是PCLK1的时钟,一般是36M。

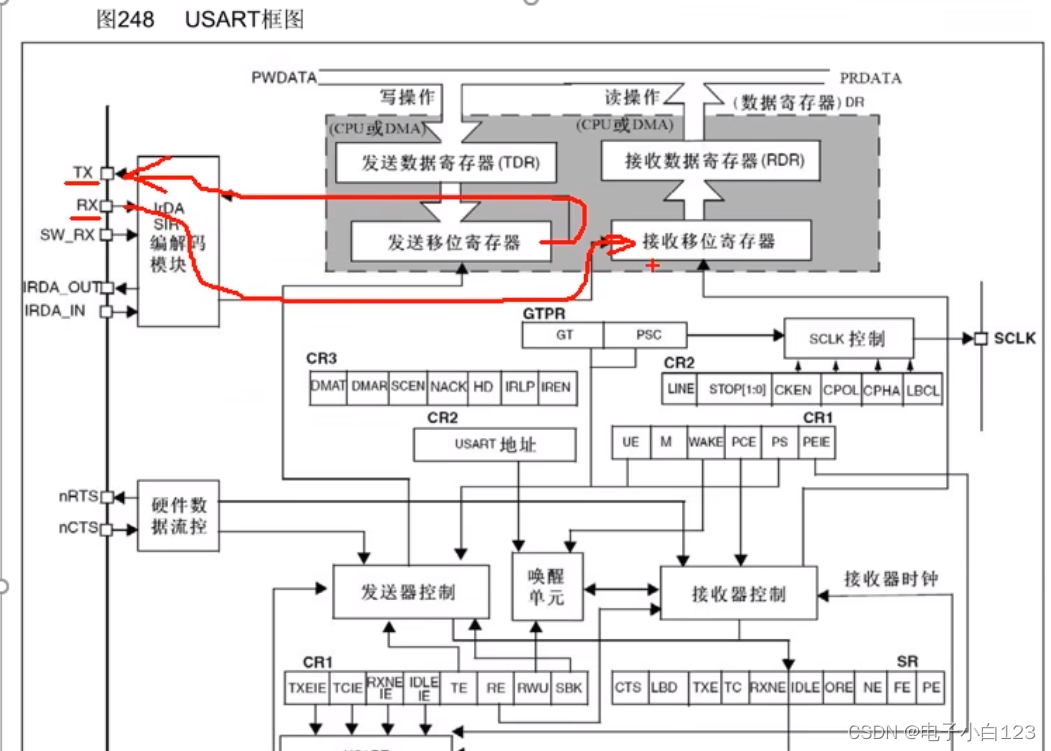

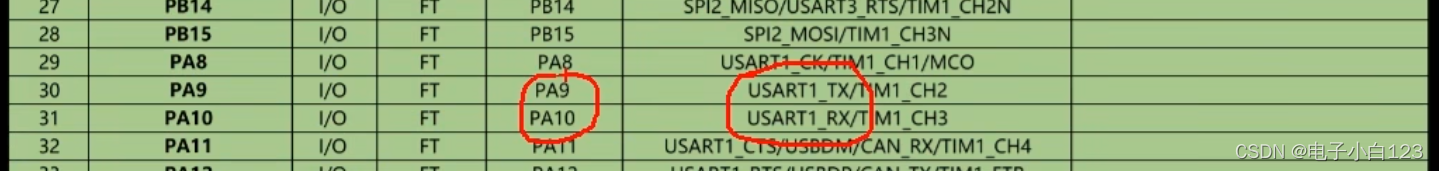

USART引脚分布表(C8T6)

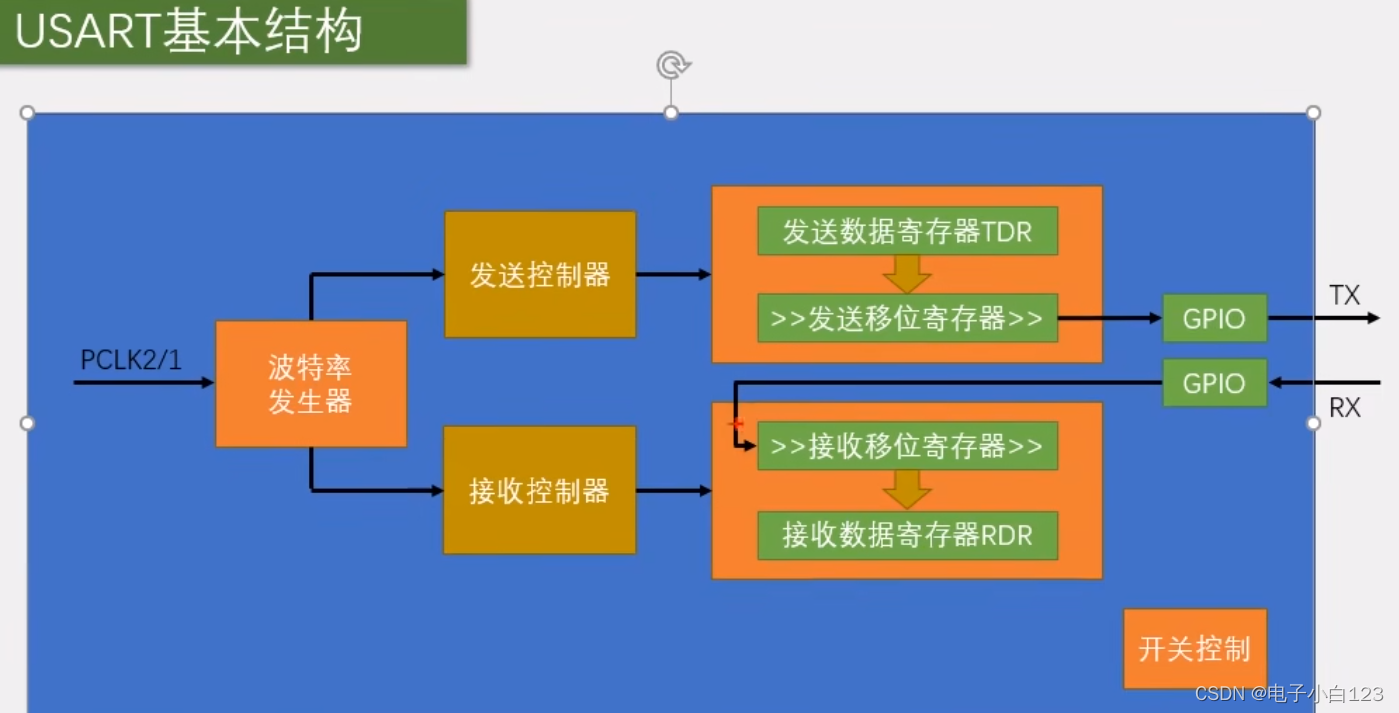

USART基本结构图

最左边这里是波特率发生器,用于产生约定的通信速率。时钟来源是PCLK2或1,经过波特率发生器分频后,产生的时钟通向发送控制器和接收控制器。发送控制器和接收控制器,用来控制发送移位和接收移位,之后,由发送数据寄存器和发送移位寄存器这两个寄存器的配合,将数据一位一位地右移出去(低位先行),通过GPIO的复用输出,输出到TX引脚,产生串口协议规定的波形。当数据由数据寄存器转到移位寄存器时,会置一个TEX的标志位,我们判断这个标志位,就可以知道是不是可以写下一个数据了。RX端也是一样的流程,在转移的同时,置一个RXNE标志位,我们检查这个标志位,就可以知道是不是收到数据了,同时这个标志位也可以去申请中断,这样就可以在收到数据时,直接进入中断函数,然后快速地读取和保存数据。

图中有四个寄存器,实际在软件层面,只有一个DR寄存器可以供我们读写。写入DR时,数据走上面这条路,进行发送;读取DR时,数据走下面这条路,进行接收。这就是USART进行串口数据收发的过程。

数据帧

在时钟的上升沿采集数据。

波特率