SPI相关理论

概述

SPI,是Serial Peripheral interface的缩写,是串行外围设备接口,是一种高速的,全双工,同步的通信总线,并且在芯片的管脚上只占用四根线,节约了芯片的管脚,同时为PCB的布局上节省空间,提供方便,正是出于这种简单易用的特性,现在越来越多的芯片集成了这种通信协议。SPI接口主要应用在 EEPROM,FLASH,实时时钟,AD转换器,还有数字信号处理器和数字信号解码器之间。

标准四线制

通常SPI通过4个引脚与外部器件相连:

MISO:主设备输入/从设备输出引脚。该引脚在从模式下发送数据,在主模式下接收数据。 MOSI:主设备输出/从设备输入引脚。该引脚在主模式下发送数据,在从模式下接收数据。 SCK: 串口时钟,作为主设备的输出,从设备的输入。

CSN(NSS): 从设备选择。这是一个可选的引脚,用来选择主/从设备。它的功能是用来作为“片选引脚”,让主设备可以单独地与特定从设备通讯,避免数据线上的冲突。从设备的CSN引脚可以由主设备的一个标准I/O引脚来驱动。

SPI通信过程分析

SPI通信中可作为从机也可以作为主机,这取决于硬件设计和软件设置。

当器件作为主机时,使用一个IO引脚拉低相应从机的选择引脚(CSN),传输的起始由主机发送数据来启动,时钟(SCK)信号由主机产生。通过MOSI发送数据,同时通过MISO引脚接收从机发出的数据。

当器件作为从机时,传输在从机选择引脚(CSN)被主机拉低后开始,接收主机输出的时钟信号,在读取主机数据的同时通过MISO引脚输出数据。

SPI总线的数据传输方式

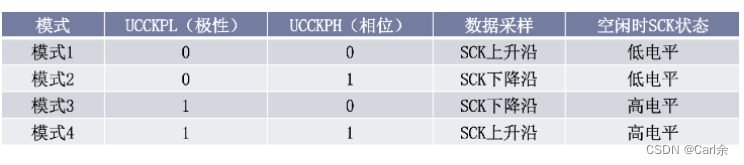

SPI总线数据传输时传输方式由两类不同的选择标准决定

CPOL:时钟极性

CPOL=1:SPI时钟线在空闲状态下为高电平

CPOL=0:SPI时钟线在空闲状态下为低电平

CPHA:时钟相位

CPHA=0:在时钟的奇数边沿采样(读取数据),在偶数边沿触发(写入数据)

CPHA=1:在时钟的偶数边沿采样(读取数据),在奇数边沿触发(写入数据)