FPGA和ARM数据交互是ZYNQ系统中非常重要的内容。PS提供了供FPGA读写的AXI-HP接口用于两者的高速通信和数据交互。一般的,我们会采用AXI DMA的方式去传输数据,DMA代码基本是是C编写,对于FPGA开发者来说不利于维护和debug。本文提供一种手写AXI_MASTER接口用于PL 向DDR指定位置写入数据并验证读写是否正确。

本项目的思路是:PS通过GPIO发起写DDR的命令ps_start(高脉冲),FPGA在收到ps_start后,开始写数据到DDR,写完后通过IRQ中断通知ARM写入完成,ARM按顺序读DDR数据并通过UART输出读出的结果,arm读完后清除中断并发起下一次的写脉冲,循环写读。本项目代码稍作修改可以为FPGA数据采集+ARM算法处理系统提供参考。

开发板为Zynq UltraScale+ xczu2cg-sfvc784-1-i

ILA 采样AXI_master读时序

uart 输出的DDR读出数据,对比写入是一致的。

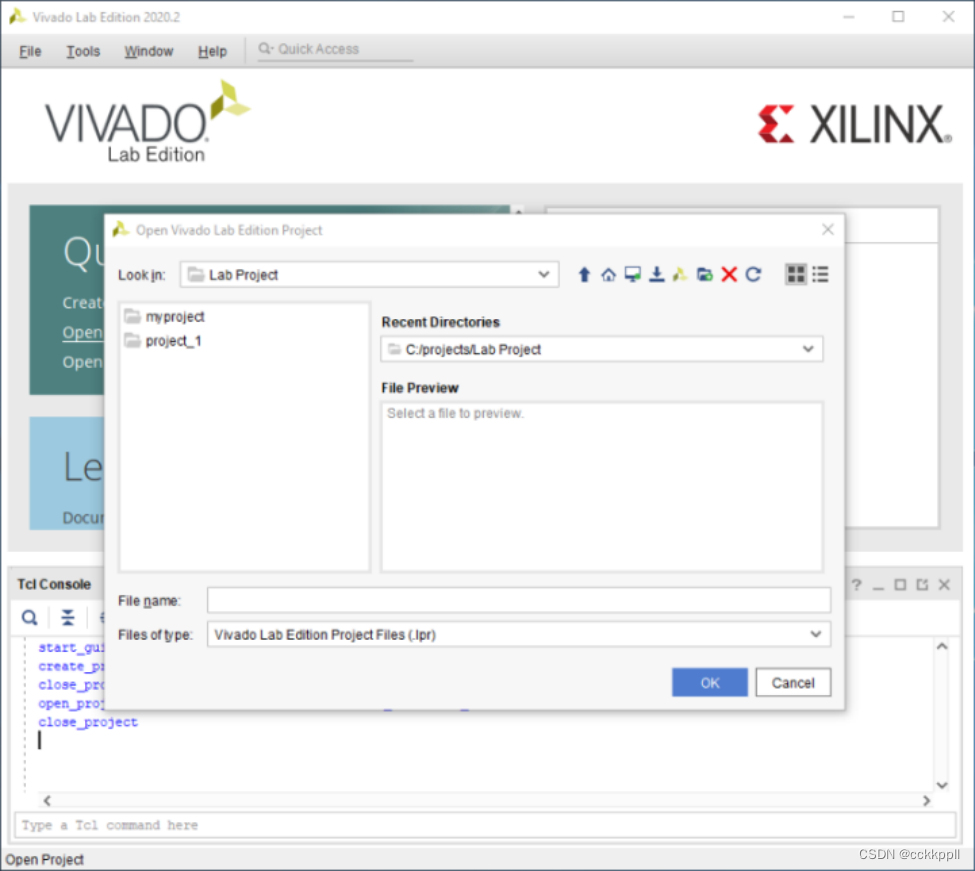

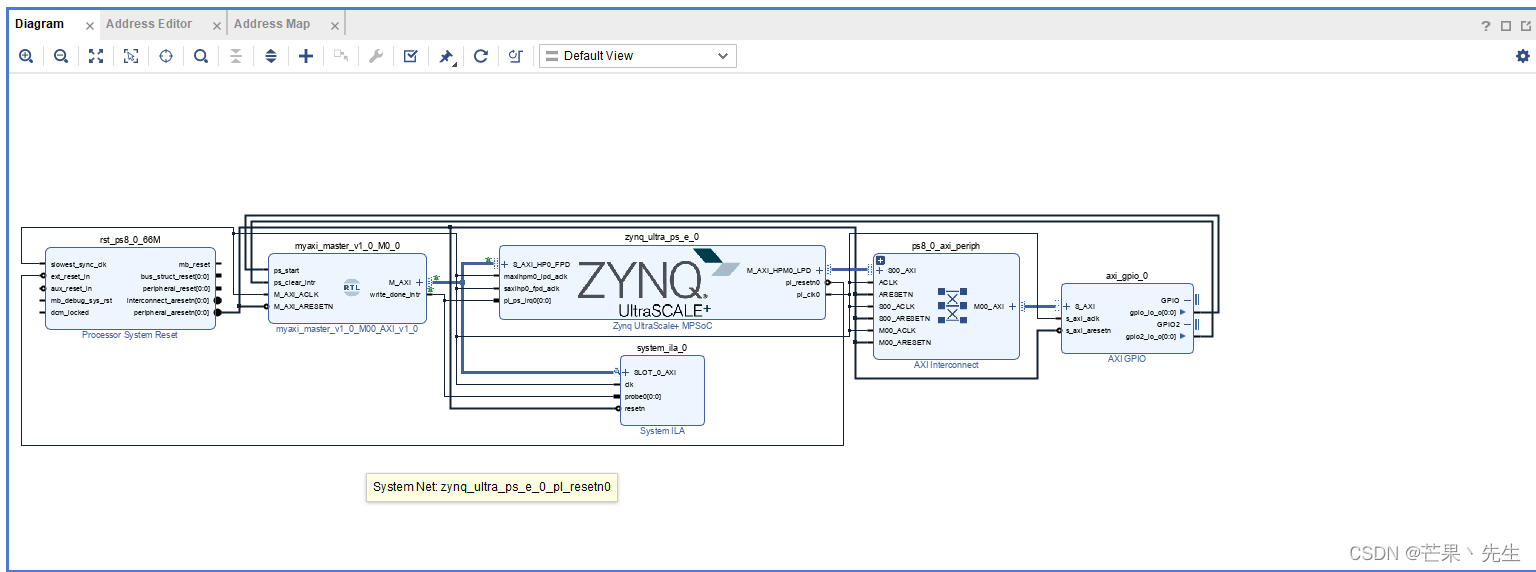

vivado block design 参考设计 注意DDR是64位DDR。

vitis 工程代码如下 需要注意 刷新CACHE后再读 不然cache和DDR数据可能不一致。

/******************************************************************************

*

* Copyright (C) 2009 - 2014 Xilinx, Inc. All rights reserved.

*

* Permission is hereby granted, free of charge, to any person obtaining a copy

* of this software and associated documentation files (the "Software"), to deal

* in the Software without restriction, including without limitation the rights

* to use, copy, modify, merge, publish, distribute, sublicense, and/or sell

* copies of the Software, and to permit persons to whom the Software is

* furnished to do so, subject to the following conditions:

*

* The above copyright notice and this permission notice shall be included in

* all copies or substantial portions of the Software.

*

* Use of the Software is limited solely to applications:

* (a) running on a Xilinx device, or

* (b) that interact with a Xilinx device through a bus or interconnect.

*

* THE SOFTWARE IS PROVIDED "AS IS", WITHOUT WARRANTY OF ANY KIND, EXPRESS OR

* IMPLIED, INCLUDING BUT NOT LIMITED TO THE WARRANTIES OF MERCHANTABILITY,

* FITNESS FOR A PARTICULAR PURPOSE AND NONINFRINGEMENT. IN NO EVENT SHALL

* XILINX BE LIABLE FOR ANY CLAIM, DAMAGES OR OTHER LIABILITY,

* WHETHER IN AN ACTION OF CONTRACT, TORT OR OTHERWISE, ARISING FROM, OUT OF

* OR IN CONNECTION WITH THE SOFTWARE OR THE USE OR OTHER DEALINGS IN THE

* SOFTWARE.

*

* Except as contained in this notice, the name of the Xilinx shall not be used

* in advertising or otherwise to promote the sale, use or other dealings in

* this Software without prior written authorization from Xilinx.

*

******************************************************************************/

/*

* helloworld.c: simple test application

*

* This application configures UART 16550 to baud rate 9600.

* PS7 UART (Zynq) is not initialized by this application, since

* bootrom/bsp configures it to baud rate 115200

*

* ------------------------------------------------

* | UART TYPE BAUD RATE |

* ------------------------------------------------

* uartns550 9600

* uartlite Configurable only in HW design

* ps7_uart 115200 (configured by bootrom/bsp)

*/

#include <stdio.h>

#include "platform.h"

#include "xil_printf.h"

#include "xgpio.h"

#include "xparameters.h"

#include "xscugic.h"

#include "xil_cache.h"

#define INTC_DEVICE_ID XPAR_SCUGIC_0_DEVICE_ID

#define INTC_DEVICE_INT_ID XPAR_FABRIC_MYAXI_MASTER_V1_0_M0_0_WRITE_DONE_INTR_INTR

#define BASE_ADDR_FOR_DDR 0x00001000

#define DATA_COUNT (64)

XScuGic InterruptController;

XScuGic_Config *GicConfig;

XGpio Gpio;

u32 intr_recv;

u32 *data_array=(u32*)BASE_ADDR_FOR_DDR;

void myHandler(void *CallbackRef);

int main()

{

intr_recv =0;

init_platform();

int Status;

/* Initialize the GPIO driver */

Status = XGpio_Initialize(&Gpio, XPAR_GPIO_0_DEVICE_ID);

if (Status != XST_SUCCESS) {

xil_printf("Gpio Initialization Failed\r\n");

return XST_FAILURE;

}

XGpio_DiscreteWrite(&Gpio, 1, 0);

XGpio_DiscreteWrite(&Gpio, 2, 0);

//GIC

GicConfig = XScuGic_LookupConfig(INTC_DEVICE_ID);

if (NULL == GicConfig) {

return XST_FAILURE;

}

Status = XScuGic_CfgInitialize(&InterruptController, GicConfig,

GicConfig->CpuBaseAddress);

if (Status != XST_SUCCESS) {

return XST_FAILURE;

}

/*

* Perform a self-test to ensure that the hardware was built

* correctly

*/

Status = XScuGic_SelfTest(&InterruptController);

if (Status != XST_SUCCESS) {

return XST_FAILURE;

}

/*

* Connect the interrupt controller interrupt handler to the hardware

* interrupt handling logic in the ARM processor.

*/

/*

* Connect a device driver handler that will be called when an

* interrupt for the device occurs, the device driver handler performs

* the specific interrupt processing for the device

*/

Status = XScuGic_Connect(&InterruptController, INTC_DEVICE_INT_ID,

(Xil_ExceptionHandler)myHandler,

(void *)&InterruptController);

if (Status != XST_SUCCESS) {

return XST_FAILURE;

}

Xil_ExceptionInit();

Xil_ExceptionRegisterHandler(XIL_EXCEPTION_ID_INT,

(Xil_ExceptionHandler) XScuGic_InterruptHandler,

&InterruptController);

/*

* Enable interrupts in the ARM

*/

Xil_ExceptionEnable();

XScuGic_SetPriorityTriggerType(&InterruptController,INTC_DEVICE_INT_ID,0x3A,0x3);

XScuGic_Enable(&InterruptController, INTC_DEVICE_INT_ID);

u32 index;

while(1){

XGpio_DiscreteWrite(&Gpio, 1, 1); //start write

if(1 == intr_recv){ //recev fpga intr

XGpio_DiscreteWrite(&Gpio, 1, 0); //start write clear

Xil_DCacheFlushRange((u32)data_array,DATA_COUNT);

for(index = 0;index <DATA_COUNT;index++)

{

xil_printf("index = %d,value = %d\r\n",index,*(data_array+index));

}

XGpio_DiscreteWrite(&Gpio, 2, 1);

intr_recv =0;

// break;

}

}

cleanup_platform();

return 0;

}

void myHandler(void *CallbackRef)

{

/*

* Indicate the interrupt has been processed using a shared variable

*/

intr_recv = 1;

xil_printf("intr occurs\r\n");

}

项目源代码地址:

fpga通过aximaster读写PS侧DDR的仿真和上板测试资源-CSDN文库