文章目录

- 前言

- 一、基础题/选做题

- 1、什么是DMA,主要优点是什么,为什么这是它的优点

- 2、SV的代码如下,给出$display中变量的值

- 3、列出4bit格雷码编码,画出二进制码转格雷码电路图

- 4、如何从慢时钟域捕获快时钟域脉冲信号,画出电路图或写出verilog代码

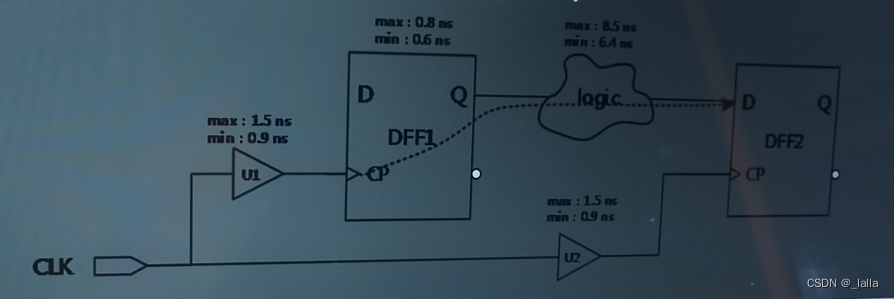

- 5、请分别计算下图所示时序路径的setup slack和hold slack,并判断是否存在违例。各个器件和组合逻辑延时如图所示,其中DFF1和DFF2的setup时间为0.2 ns, hold为0.1 ns,时钟CLK周期为10 ns.

- 6、谈谈对DFT的理解

- 7、如果在电路中使用如下两种结构的时钟门控电路:

- 8、请根据如下简单通讯电路的描述,给出验证思路或者方案

- 9、用条件编译语句generate实现如下电路

- 10、如下图所示,有两个异步时钟CLK1、CLK2,均为高速时钟,Q1为CLK1时钟域的信号,CLK2对Q1采样。请问可否以STA保证路径的时序?为什么?

- 11、仿真不能继续进行,stuck在一点不动,可能是什么原因?

- 12、请描述验证的考核指标覆盖率有哪些?并且简述其意义是什么。

- 13、检测一个输入信号i_s,当i_s宽度大于等于一个clock时钟周期时,在下一个时钟沿输出信号o_s为一个clock时钟周期的高电平。请用verilog语言实现。(声明、模块头可以省略)

- 14、请问如下电路中,所使用的两级同步电路是否正确?为什么?

- 15、如何测试如图所示电路的SA0 fault?请写出所需加载激励以及对应输出。

- 16、什么是竞争与冒险,解决竞争与冒险的方式有哪些?

- 17、请简述集成电路设计流程,并给出该流程中各环节所用到的EDA工具(注:不局限于数字前端;各环节至少给出一种EDA工具)

- 18、请简述latch与DFF的区别

- 19、使用verilog function方式实现下面的prbs多项式,输出位宽为20bit:

- 20、以下电路中,路径FF0/CK -> FF1/RN是否可以通过STA保证其时序满足器件要求?

- 21、关于task的调用问题验证平台,的输出是什么?

- 22、一个简单的仿真验证平台,有哪几部分构成?仿真平台应提供哪些关键信号?UVM都有哪些组件?什么是工厂模式?

- 23、用CMOS电路画出以下表达式:AB+~(CD)

- 24、数字电路采用Verilog完成设计,请问什么是RTL级设计?

- 25、阻塞赋值与非阻塞赋值的区别,并举例一个简单的代码。

前言

笔试题型:基础题(10个) + 选做题(5个)

笔试平台:百一测试(电脑监控)

笔试时间:2h

做题感受:题目全部都是大题目,题量很大,压根写不完,而且做完一个部分才能跳到下一个部分,建议想不出来思路的直接立马放弃做下面的题目。

一、基础题/选做题

1、什么是DMA,主要优点是什么,为什么这是它的优点

2、SV的代码如下,给出$display中变量的值

class Packet;

rand intlen;

constraint c_short {len inside {[50-100]};}

constraint c_long {len inside {[500:1000]};}

endclass

Packet P;

initial begin

p =new();

p.c_short.constraint_mode(0);

assert (p.randomize());

$display("len = %0d".p.len);

end

class ori_tran;

rand bit[31:0] i_a;

rand bit[31:0] i_b;

constraint test_cons{

i_a == 'h10;

i_ b== 'h12;}

endclasse

class div_tran extends ori_ran;

constraint test_cons{

i_b == 'h22;

}

endclass

initial begin

p=new();

p.c_shoxt.constraint.mode(0);

assert(p.randomize());

$display("len = %0d",p.len);

end

class ori_tran;

rand bit[31:0] i_a;

rand bit[31:0] i_b;

constraint test_cons{

i_a == 'h10;

i_ b== 'h12;}

endclasse

class div_tran extends ori_ran;

constraint test_cons{

i_b == 'h22;

}

endclass

initial begin

p=new();

assert(p.randomize());

$display("i_a = %0h, i_b = %0h",p.i_a, p.i_b);

end

3、列出4bit格雷码编码,画出二进制码转格雷码电路图

4、如何从慢时钟域捕获快时钟域脉冲信号,画出电路图或写出verilog代码

5、请分别计算下图所示时序路径的setup slack和hold slack,并判断是否存在违例。各个器件和组合逻辑延时如图所示,其中DFF1和DFF2的setup时间为0.2 ns, hold为0.1 ns,时钟CLK周期为10 ns.

6、谈谈对DFT的理解

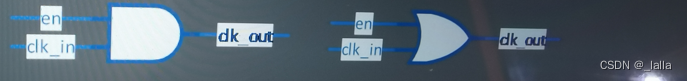

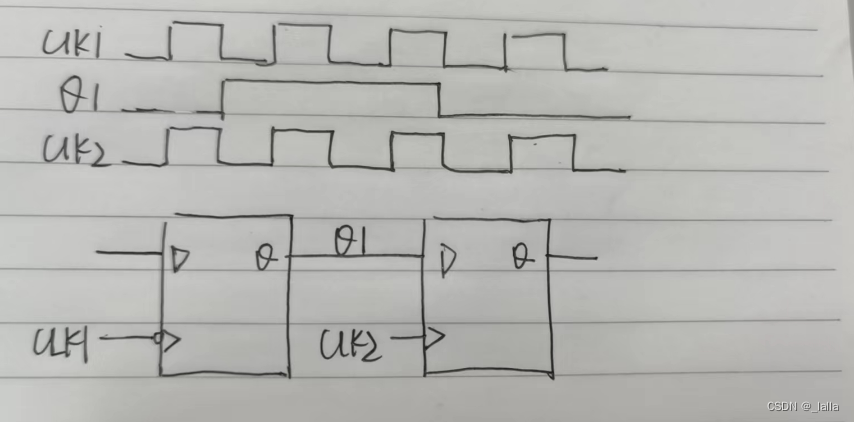

7、如果在电路中使用如下两种结构的时钟门控电路:

(1)请问会对电路产生什么影响(至少两种)?请画出相关时序图进行说明

(2)如何针对上述两种电路进行相应的修改?请画出电路结构图,并附上时序图进行说明如何消除上述影响

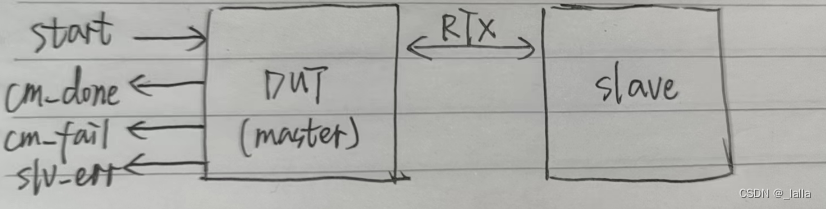

8、请根据如下简单通讯电路的描述,给出验证思路或者方案

该电路为单线通讯电路,并作为master器件,半双工工作,其信号线名字为RTX

- master能发的命令只有1个且slave一定会给出响应,响应有2种:DONE、FAIL

- master可通过输入信号start启动发命令,发完命令,立刻转入响应接收状态

- slave回的响应,由于有被外部噪声干扰的可能,因此master接收slave的响应,有可能有以下几种情况

- slave应答DONE,master置起命令执行成功标志:CMD_DONE

- slave应答FAIL,master置起命令执行失败标志:CMD_FAIL

- slave应答既不是DONE也不是FAIL,master置起非法响应标志:SLV_ERR

无论slave是上面哪种响应,master在置起标志后,都会重新回到等待发送命令状态

假设在testbench中,以上所有三个标志信号以及启动信号start,全都是直接可见的,如下图所示:

9、用条件编译语句generate实现如下电路

(1) 三输入的或门,位宽小于6

(2) 三输入与门,位宽等于8

10、如下图所示,有两个异步时钟CLK1、CLK2,均为高速时钟,Q1为CLK1时钟域的信号,CLK2对Q1采样。请问可否以STA保证路径的时序?为什么?

11、仿真不能继续进行,stuck在一点不动,可能是什么原因?

12、请描述验证的考核指标覆盖率有哪些?并且简述其意义是什么。

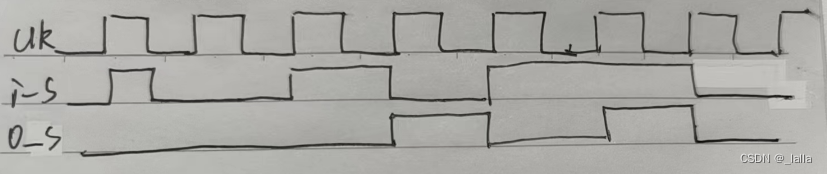

13、检测一个输入信号i_s,当i_s宽度大于等于一个clock时钟周期时,在下一个时钟沿输出信号o_s为一个clock时钟周期的高电平。请用verilog语言实现。(声明、模块头可以省略)

14、请问如下电路中,所使用的两级同步电路是否正确?为什么?

assign sig = cur_state[3:0]==4'b1010;

always @(posedge clk or negedge rst n)begin

if(~rst_n) begin

sig syn0 <= 1'b0;sig_syn1 <= 1'b0;end

else begin

sig syn0 <= sig:

sig syn1 <= sig syno;

end

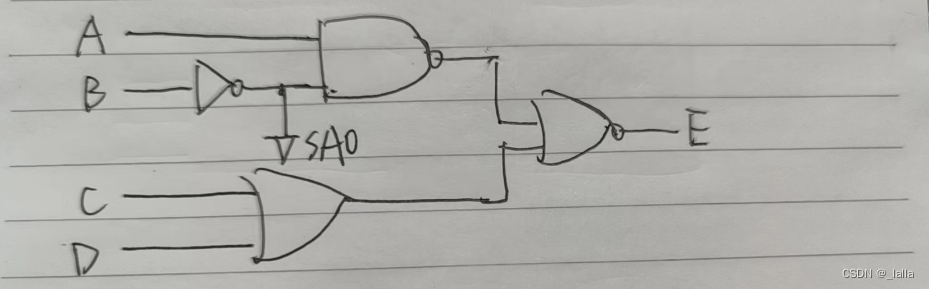

15、如何测试如图所示电路的SA0 fault?请写出所需加载激励以及对应输出。

16、什么是竞争与冒险,解决竞争与冒险的方式有哪些?

17、请简述集成电路设计流程,并给出该流程中各环节所用到的EDA工具(注:不局限于数字前端;各环节至少给出一种EDA工具)

18、请简述latch与DFF的区别

19、使用verilog function方式实现下面的prbs多项式,输出位宽为20bit:

x23+x18+1

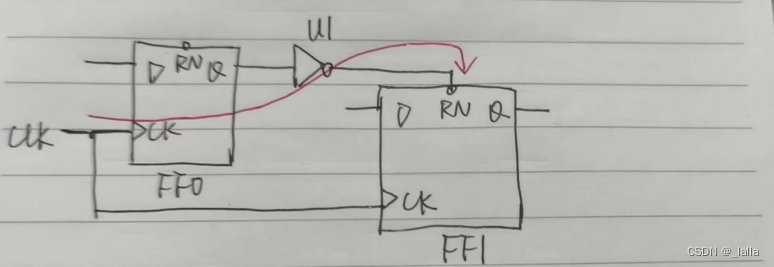

20、以下电路中,路径FF0/CK -> FF1/RN是否可以通过STA保证其时序满足器件要求?

21、关于task的调用问题验证平台,的输出是什么?

initial begin

#1 test(a);

end

task test(input bit a)

if(a=2)

$display("a=%d',a);

else

$display("HAHA!);

endtask

已知激励如下:

initial begin

a=1;

#2;

a=2;

end