视频链接

Nand flash电路设计01_哔哩哔哩_bilibili

NAND FLASH电路设计

1、NAND FLASH介绍

Nand-flash内存是flash内存的一种,其内部采用非线性宏单元模式,为固态大容量内存的实现提供了廉价有效的解决方案。Nand-flash具有容量较大,改写速度快等优点,适用于大量数据的存储。

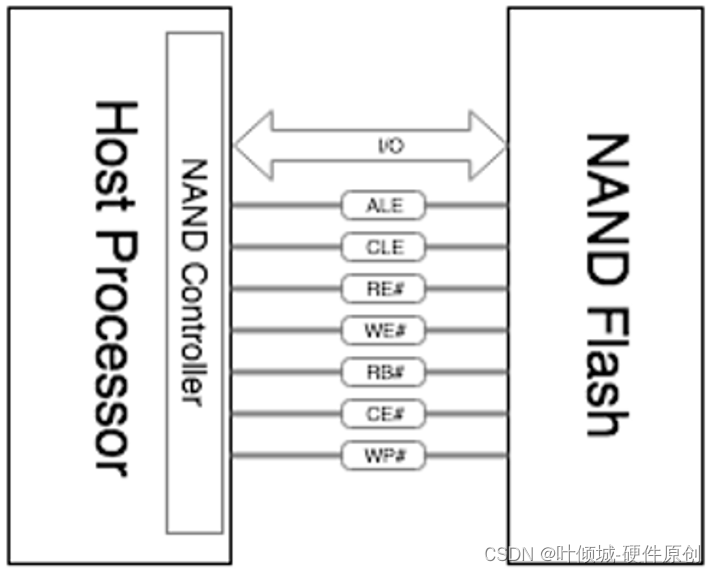

NAND Flash需要通过专门的NFI(NAND Flash Interface)与Host端进行通信,如下图所示:

NAND Flash Interface

2、NAND FLASH存储单元分类及对比

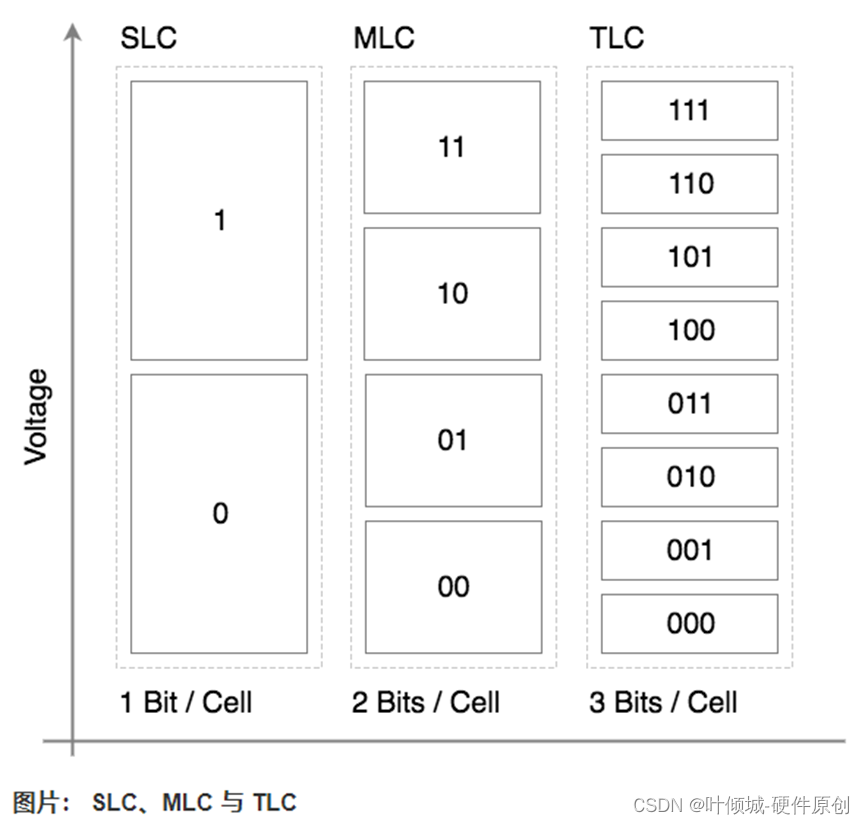

NAND Flash根据每个存储单元内存储比特个数的不同,可以分为SLC(Single-Level Cell)、MLC(Multi-Level Cell)和 TLC(Triple-Level Cell)三类。其中,在一个存储单元中,SLC可以存储1个比特,MLC可以存储2个比特,TLC 则可以存储3个比特。

NAND Flash的一个存储单元内部,是通过不同的电压等级,来表示其所存储的信息的。在SLC中,存储单元的电压被分为两个等级,分别表示0和1两个状态,即1个比特。在MLC中,存储单元的电压则被分为4个等级,分别表示00 01 10 11 四个状态,即2个比特位。同理,在TLC中,存储单元的电压被分为 8个等级,存储3个比特信息。

NAND Flash 的单个存储单元存储的比特位越多,读写性能会越差,寿命也越短,但是成本会更低。

3、嵌入式设备上eMMC逐步取代nand flash?

4、Nand Flash优点

1. 高密度存储 2. 快速读写速度 3. 低功耗 4. 可靠性

闪存通常包括NOR和NAND两种类型。

NOR闪存是由Intel公司开发的,是一种随机访问设备,具有专用的地址和数据线,以字节的方式进行读写,允许对存储器当中的任何位置进行访问,这使得NOR闪存是传统的只读存储器(ROM)的一种很好的替代方案,比如计算机的BIOS芯片。

NAND闪存则没有专用的地址线,不能直接寻址,是通过一个间接的、类似I/O的接口来发送命令和地址来进行控制的,这就意味着NAND闪存只能够以页的方式进行访问。

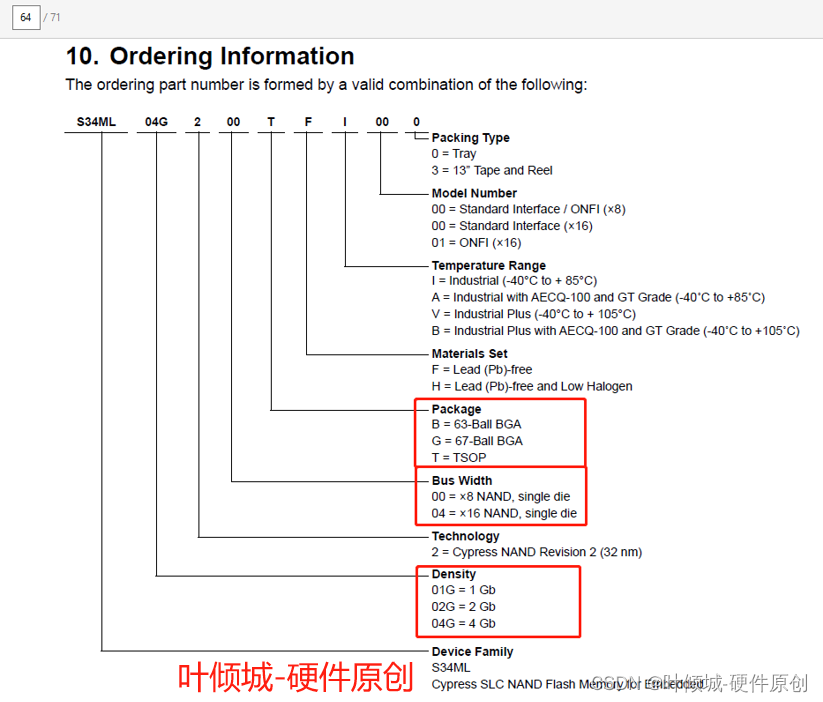

5、NAND FLASH介绍(注意区分X8和X16的 赛普拉斯和镁光有区别的!!!)以赛普拉斯为例

5.1、NAND flash命名规范

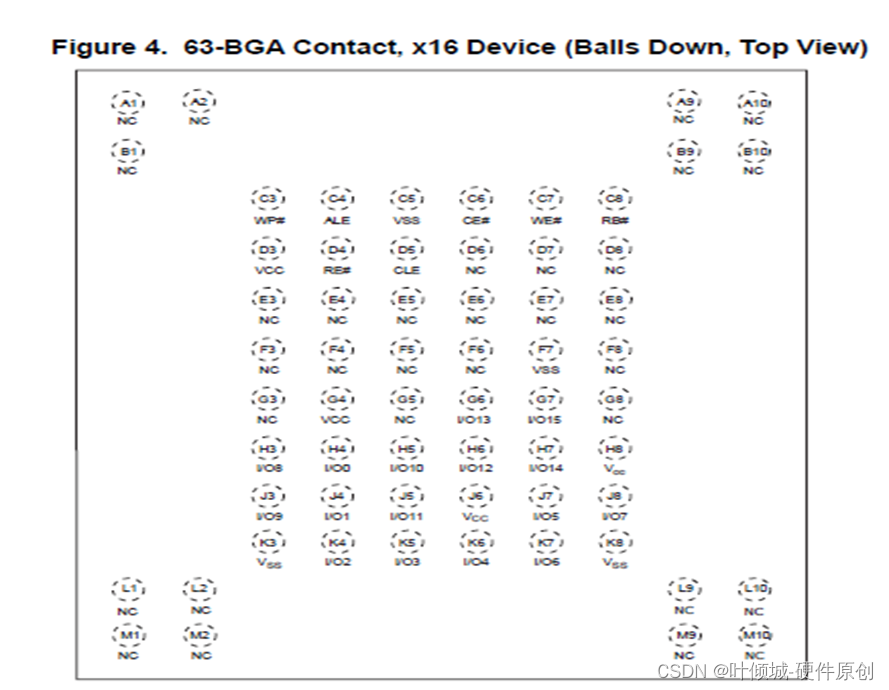

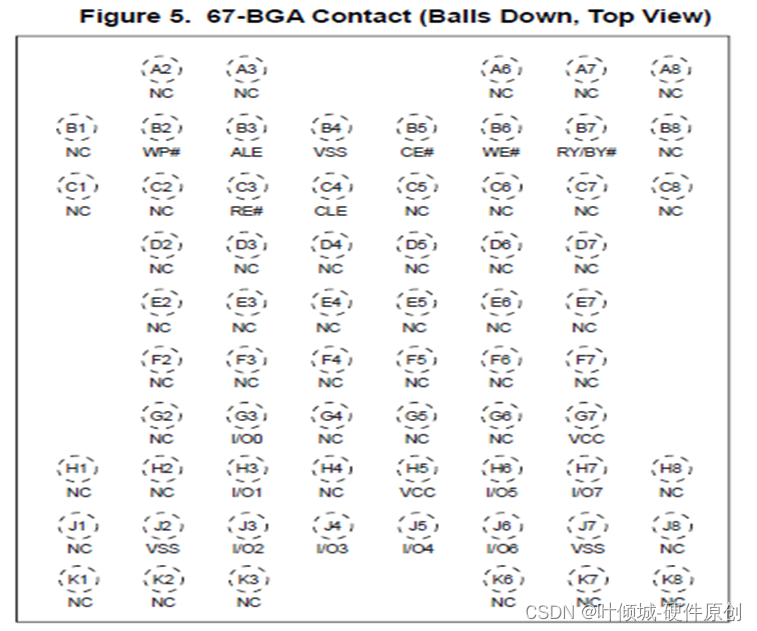

5.2、Nand flash封装

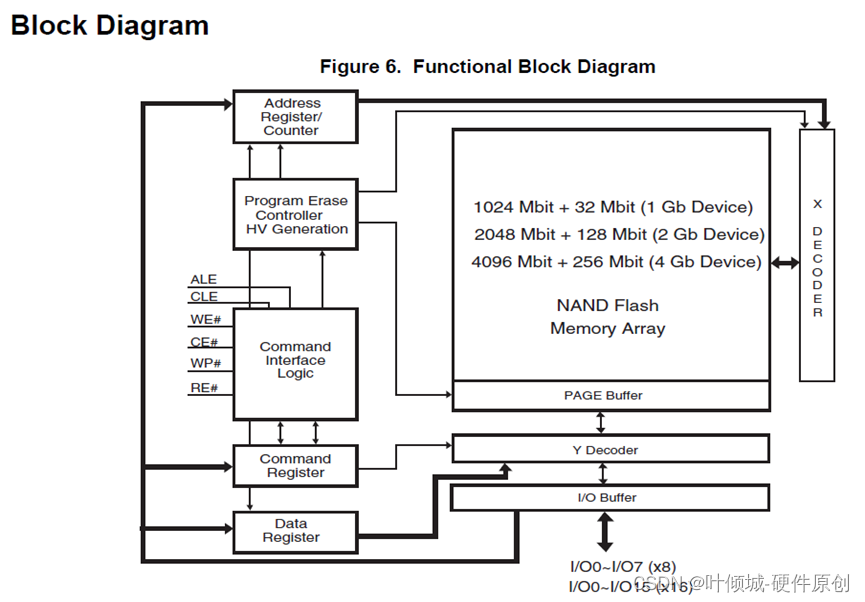

6、Nand Flash框图

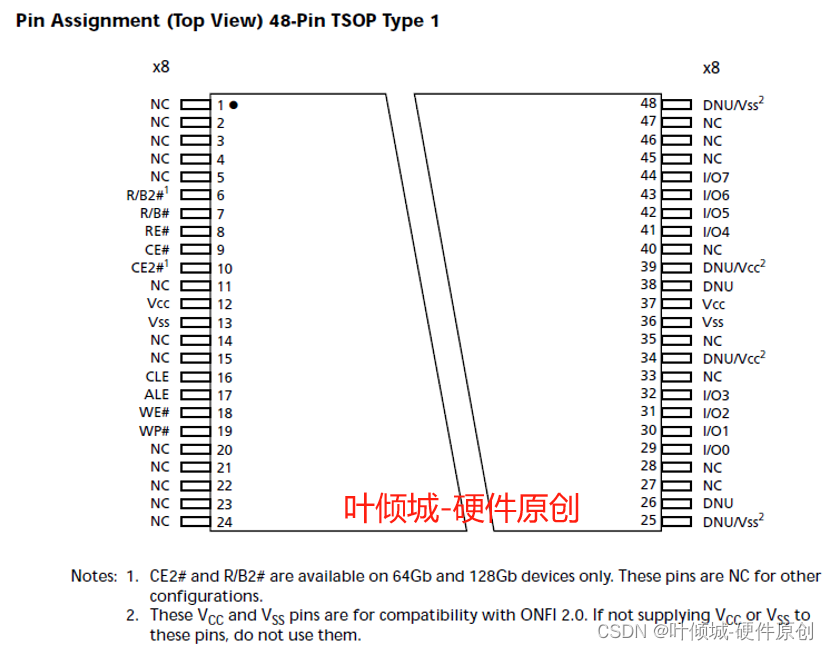

在DATA0~DATA7上既传输数据,又传输地址,也传输命令;

当ALE为高电平时传输的是地址;

当CLE为高电平时传输的是命令;

当ALE和CLE都为低电平时传输的是数据;

7、NAND FLASH管脚定义

电源线

| 管脚符号 | 类型 | 描述 |

| VCC | Supply | Power Supply The VCC supplies the power for all the operations (Read, Program, Erase) |

| VSS | Supply | Ground |

信号线

| 管脚符号 | 类型 | 描述 |

| IO[7:0](X8) IO[15:8](X16) | I/O | Inputs/Outputs:The I/O pins are used for command input, address input, data input, and data output. The I/O pins float to High-Z when the device is deselected or the outputs are disabled 输入/输出。I/O管脚用于命令输入、地址输入、数据输入和数据输出。 当取消选择设备或禁用输出时,I/O引脚浮动到高阻态。 |

| CLE | Command Latch Enable:This input activates the latching of the I/O inputs inside the Command Register on the rising edge of Write Enable (WE#) 命令锁存使能。这个输入激活了写使能上升边缘的命令寄存器内的I/O输入的锁存。 | |

| ALE | Address Latch Enable:This input activates the latching of the I/O inputs inside the Address Register on the rising edge of Write Enable (WE#) 地址锁存使能。这个输入激活了写使能上升边缘的地址寄存器内的I/O输入的锁存。 | |

| CE# | Chip Enable:This input controls the selection of the device。When the device is not busy CE# low selects the memory 芯片使能。这个输入控制设备的选择。当设备不忙时,CE为低时选择内存。 | |

| RE# | Read Enable:The RE# input is the serial data-out control, and when active drives the data onto the I/O bus。 读使能。读输入是串行数据输出控制,当活动驱动数据到I/O总线。 | |

| WE# | Write Enable:This input latches Command, Address and Data。The I/O inputs are latched on the rising edge of WE#。 写使能。这个输入锁存命令,地址和数据。I/O 输入被锁定在我们写的上升边缘。 | |

| WP# | Write Protect:The WP# pin, when low, provides hardware protection against undesired data modification (program / erase)。 写保护。WP#引脚为低,提供硬件保护,以防止不需要的数据修改(编程/擦除)。 | |

| R/B# | Ready/Busy:The Ready/Busy output is an Open Drain pin that signals the state of the memory。 就绪/忙输出是一个开漏引脚,用于显示内存状态。 |

8、NAND FLASH硬件电路设计要点(★)

9、硬件实战设计 (★)

9.1 全志H3-Nand Flash硬件电路实战

9.2 ZYNQ -Nand Flash硬件电路实战(尤其要注意!!!)

9.3 HI3798 -Nand Flash硬件电路实战

9.4 Nand Flash硬件电路实战

10、拓展

1、Nand Flash硬件特性详解(推荐)

2、Nand Flash原理