总结

还是从设备树,mac驱动,mac驱动对mdio总线的注册,phy驱动 ,phy的datasheet,cpu的datasheet 几个方面来看来看

0.确认供电,以及phy的地址(一般会有多个地址,根据相关引脚电平可配置)

1.确认reset的有效电平

2.确认IO的有效电平

3.确认phy-mode,以及它的pinctrl的复用情况 (cat /sys/kernel/debug/pinctrl/pinctrl-handles 看current state)

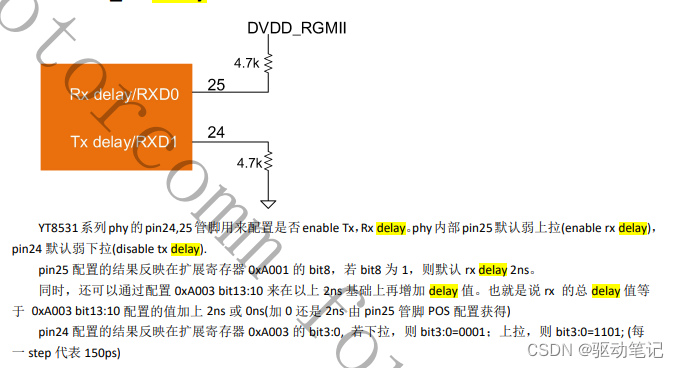

4.确认rx_tx_delay的使能,和对应平台的时序

5.确认中断属性带来的影响

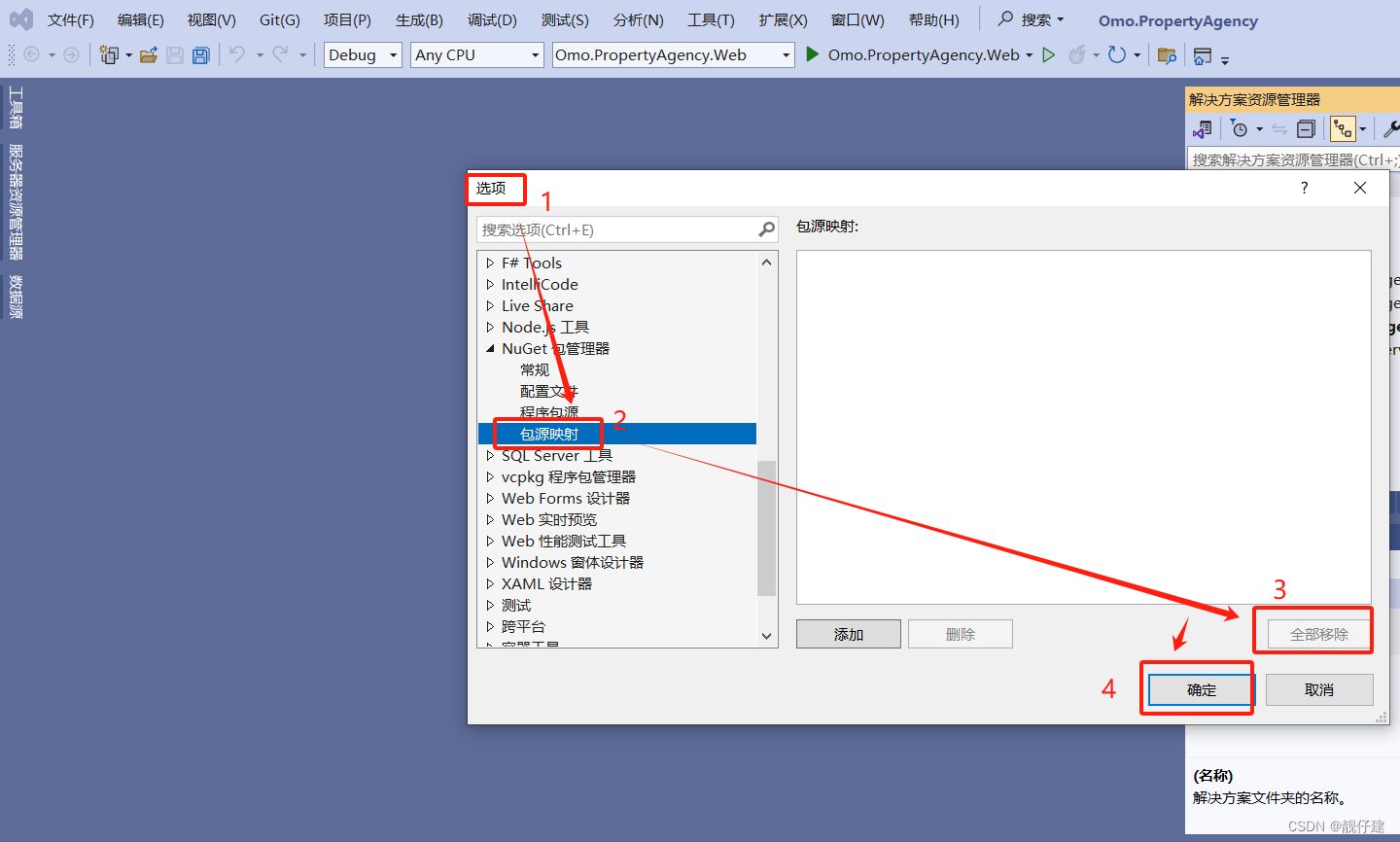

设备树

主要是选择pinctrl;配置reset脚;设置IO电平;设置phy的寄存器,phy-mode,中断属性等

eth0: eth@0xd4281800 {

compatible = "eth";

pinctrl-names = "default", "rgmii-pins";

pinctrl-0 = <&emac_pmx_func0 &emac_pmx_func2 &emac_pmx_func3 &emac_pmx_func4>;

pinctrl-1 = <&emac_pmx_func0 &emac_pmx_func1 &emac_pmx_func2 &emac_pmx_func3 &emac_pmx_func4>;

reg = <0xd4281800 0x200>;

interrupts = <10 11>;

lpm-qos = <PM_QOS_CPUIDLE_BLOCK_AXI>;

status = "okay";

reset-gpio = <&gpio 34 0>;

reset-active-low;/* 根据phy的电气属性选择这个使能电平,一般都是拉低复位,拉高正常工作 */

reset-delays-us = <0 100000 100000>;

clk-tuning-enable;

tx-clk-config = <0x1>;

rx-clk-config = <0x1>;

3v3-enable = <0>; /* IO voltage, 1 - 3.3v, 0 - 1.8v 跟据phy的电气属性选择不同电平 */

phy-handle = <&phy0>;

mdio: mdio-bus {

#address-cells = <0x1>;

#size-cells = <0x0>;

/* YT8531 10M/100M/1000M 3.3V RGMII PHY */

phy0: phy@0 {

compatible = "ethernet-phy-id4f51.e91b","ethernet-phy-ieee802.3-c22";

device_type = "ethernet-phy";

reg = <0x0>; /* set phy address*/

phy-mode = "rgmii";

//interrupts = <11>; /* 有中断属性的话,当phy的状态变为running,就不会去调用phy_read_status */

};

};

};状态机

3.10.33内核版本如下 ,不同版本内核,状态机跟设备树都是不一样的操作;具体以各版本源码为准;如果设备了配了中断属性,RUNNING状态就不会自适应百兆千兆了

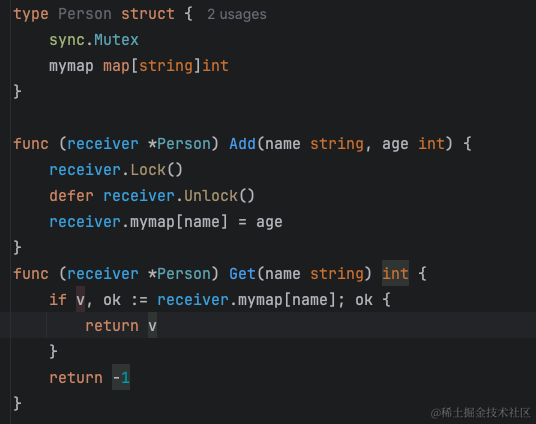

void phy_state_machine(struct work_struct *work)

{

......

case PHY_RUNNING:

/* Only register a CHANGE if we are polling or ignoring

* interrupts and link changed since latest checking.

*/

if (!phy_interrupt_is_valid(phydev)) {

old_link = phydev->link;

err = phy_read_status(phydev);

if (err)

break;

if (old_link != phydev->link)

phydev->state = PHY_CHANGELINK;

}

break;

......

}mac驱动

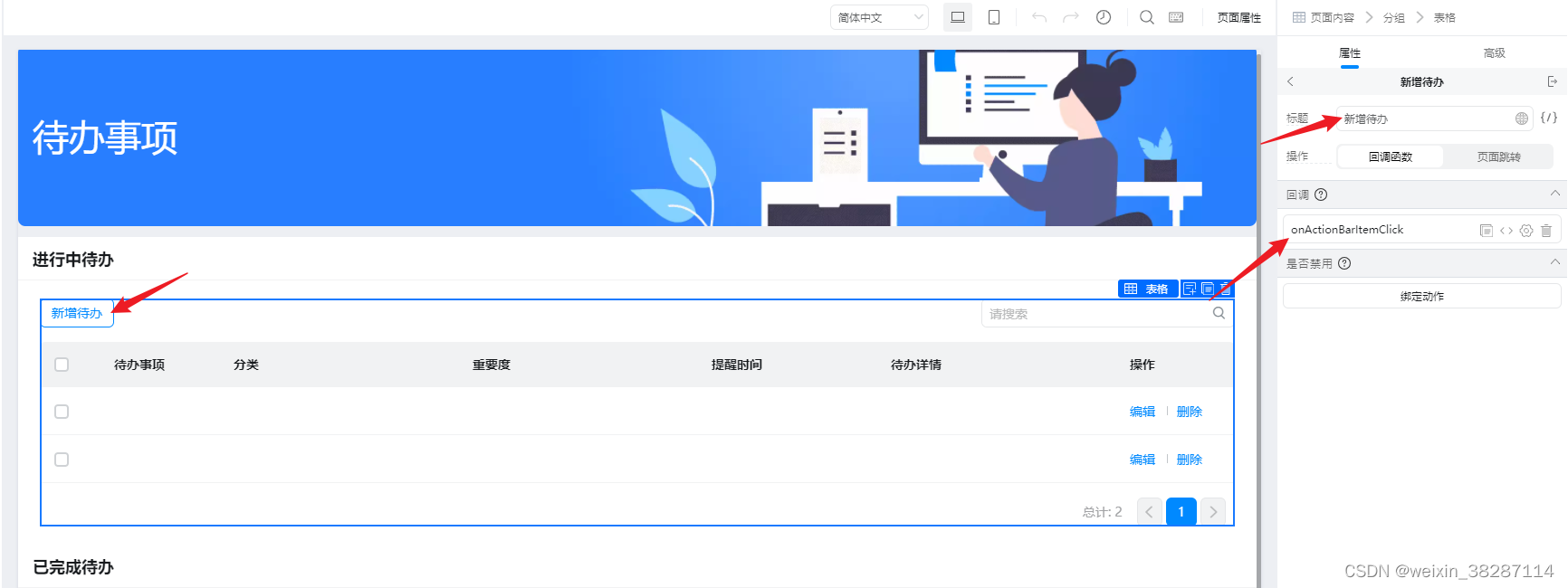

up eth0时会调用emac驱动中注册的net_device的netdev_ops成员的ndo_open

net_device_ops

ndo_open

of_phy_connect

phy_prepare_link

phydev->adjust_link = handler;这个handler是mac驱动根据link状态,来调整speed和duplexrx_tx_delay

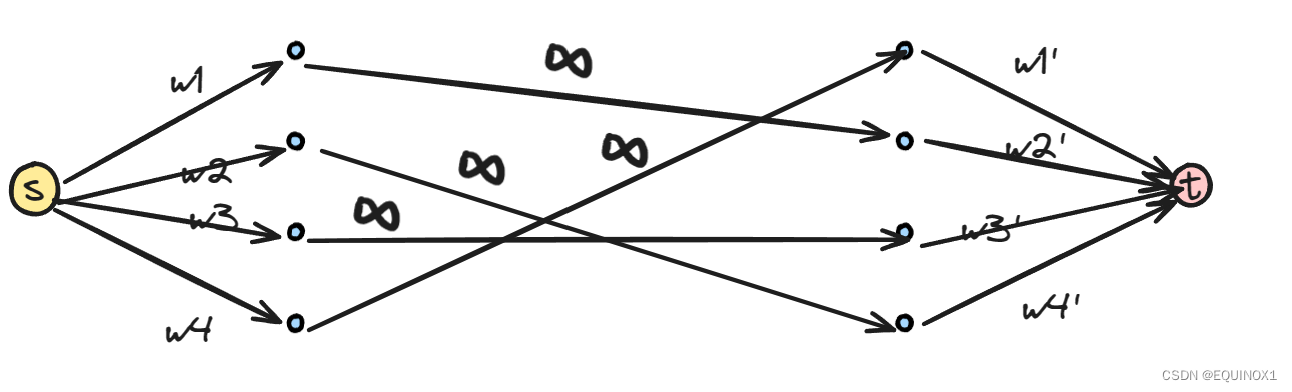

RX和TX的delay是决定数据流是否能通的关键,因为不同平台的数据传输时序各有差异,phy驱动需要对这个delay进行调整

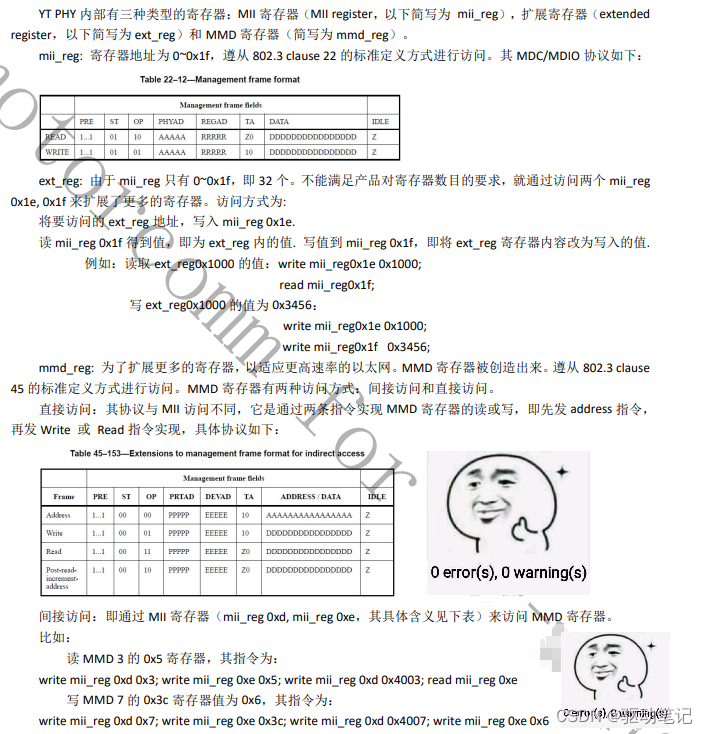

寄存器

PHY是 IEEE802.3 中定义的一个标准模块。PHY 寄存器的地址空间为 5 位,因此寄存器范围是0 到31 ,最多有 32 个寄存器。IEEE802.3 定义了地址为0-15 这16个寄存器的功能,地址16-31的寄存器留给芯片制造商自由定义。当然不同PHY,还是以他们的datasheet为准

访问方式

不同的phy的大体上都有这三种方式来访问phy的寄存器,扩展寄存器不同平台的差异就比较明显,因为是有phy厂家自己定义的