利用图形化编程的并行特性以及 FPGA 上 LabVIEW 图的真正并行实现,您可以通过将应用程序代码划分为更小的进程来进一步优化执行速度。与整个应用程序在一个循环中运行相比,这使得每个进程能够实现更高的循环速率和更高的应用程序整体执行速率。

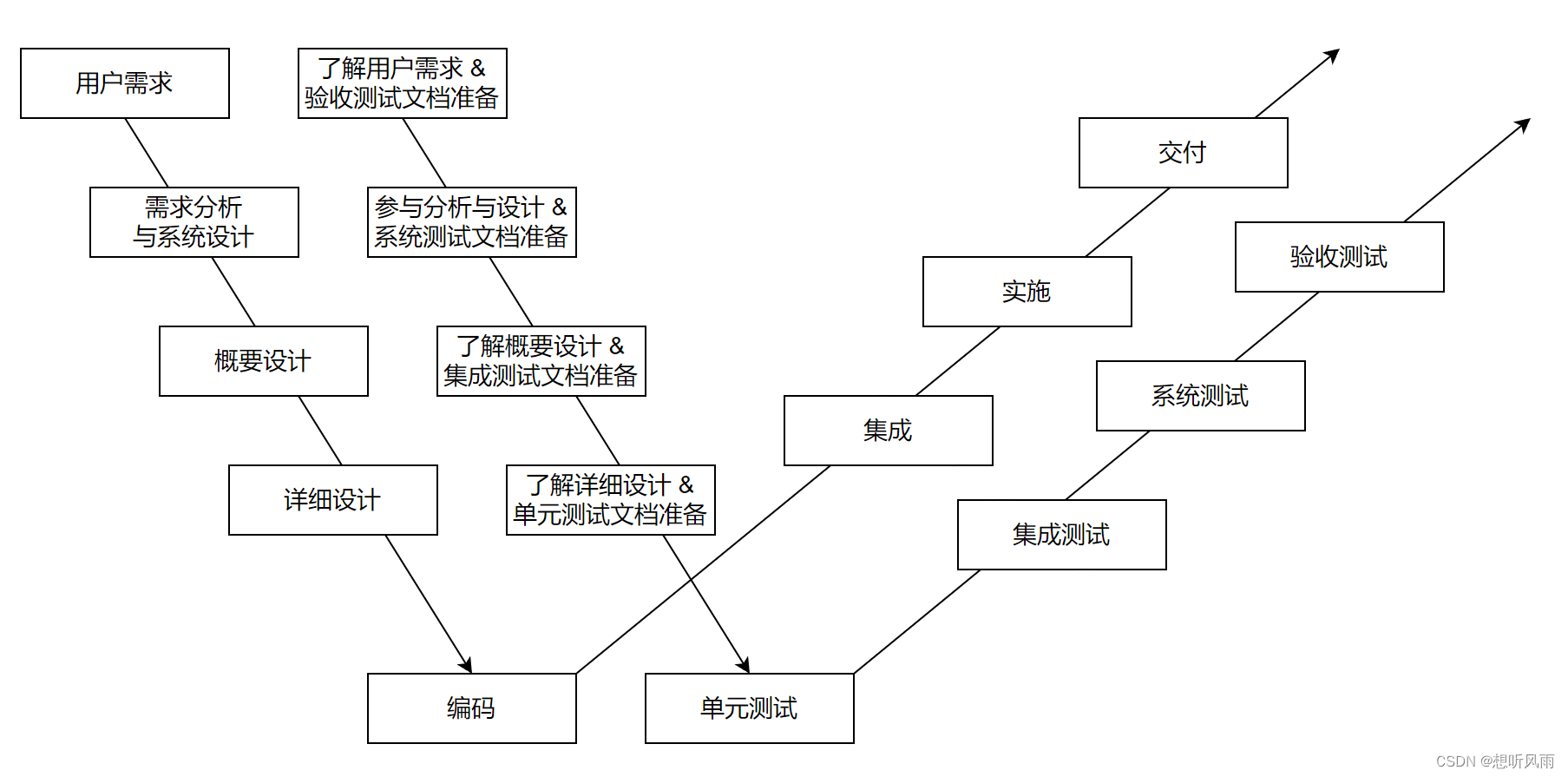

例如,典型的 DAQ 应用程序可以分为数据采集、数据处理和数据传输到主机应用程序的进程。这些任务可以作为单个循环中的序列来实现,但也可以编码为三个单独的循环,如下所示。一个循环处理数据采集和采集定时,并将数据传递给处理。第二个循环从第一个循环接收数据,对其进行处理,然后将其传递给第三个循环,第三个循环负责将处理后的数据传输到主机应用程序。

并行循环或代码段之间的数据传输和同步可以使用标准 LabVIEW FPGA 工具(包括 FIFO 和事件)进行处理。FIFO 允许您在 FPGA 应用程序中存储和缓冲数据,因此它们对于在程序框图的两个不同部分之间或子 VI 之间传递数据非常有用。它们还可用于同步两个不同的循环,以便接收循环根据其接收到的数据与发送方同步。FPGA VI 中可以创建多个 FIFO,每个 FIFO 都可以配置单独的数据类型和深度。配置用于块存储器的 FIFO 共享 FPGA 上可用的用户存储器,并且不会占用任何 FPGA 门本身。使用 FIFO 读取和写入节点上的超时参数,您可以配置这些节点的单独行为。

如果两个不直接交换数据的循环之间需要同步,则可以使用事件。事件允许您使用“等待发生”函数阻止一个循环,直到另一个循环完成特定操作并调用“设置发生”函数,如下图所示。

该技术几乎可以应用于任何应用。通过查看应用程序内的数据流,您可以识别可以彼此独立运行的不同进程,即使它们需要在应用程序的更大方案中同步。

除了提高性能之外,这种模块化编程方法还可以帮助您组织和管理应用程序代码,使您能够更轻松地测试和调试应用程序,并提高未来具有类似要求的应用程序中的代码重用。